# UNIVERSITY OF OSLO Department of Informatics

## Digital Subthreshold CMOS

Sequencing and Logic Elements for Power Analysis Resistance

Master thesis

Håvard Pedersen Alstad

2nd May 2008

## **Abstract**

This thesis examines subthreshold operation for reducing power consumption and protection against power analysis attacks of digital CMOS circuits. Subthreshold operation is considered the most efficient way to reduce the power consumption of CMOS.

There are few studies analyzing the performance of sequencing elements in subthreshold region. Sequencing elements play an important part of clocked sequential circuit systems. Therefore, it is necessary to have a good understanding of the different design types and their applicability in subthreshold circuits.

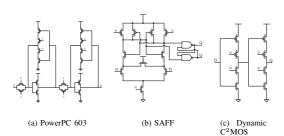

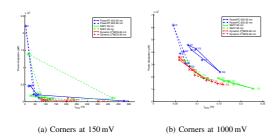

In this thesis, different flip-flop designs commonly used in super-threshold systems are compared in subthreshold operation. According to process corner simulations, a PowerPC 603 type flip-flop operates successfully in all corners in a 65 nm process down to a power supply voltage of 125 mV. This flip-flop has a delay time of 28.7 ns and a power consumption of 2.4 nW in the typical corner. The power consumption decrease corresponds to a reduction factor of 20 000, compared to normal operation.

As cryptographic algorithms have become more secure against cryptoanalysis attack, several types of attacks exploiting physical emitted informations have been reported. Power analysis attacks use the power consumption pattern to attack the chip. An increasing demand for secure data communication makes it even more important to design with resistance against side channel attacks in mind for certain applications.

Operating in subthreshold region significantly reduces the signal amplitude and the dynamic power consumption component. The reduction of these elements is used to create a S-box for the AES encryption cipher with increased resistance against power analysis attacks. By running with subthreshold operation, the correlation between power consumption of different input values decreases with a factor of 2 500 at the cost of 350 times delay degradation.

Simulations in 90 nm and 65 nm processes provided by STMicroelectronics are performed in Cadence Virtuoso Platform.

## **Preface**

This thesis is submitted as part of the degree *Master of Informatics* in Microelectronics at the Department of Informatics, University of Oslo. The project was initiated in November 2006 and concluded in May 2008.

The work on this thesis has been very interesting and challenging in many ways. The thesis addresses several relatively new topics in the VLSI design area, which in recent years have gained increased interest in research and development. Among other things, the project has lead to four scientific publications. Through the work on this project, I got the opportunity to participate on the Design and Diagnostics of Electronic Circuit Systems 2008 conference in Bratislava, Slovakia. The conference was both interesting and inspiring.

First of all, I would like to thank my supervisor Snorre Aunet for accepting me as his student and for inspiration and guidance during this project. Helpful discussions have driven the project forward and given valuable inputs on the work.

I want to thank the students at the laboratory, especially Trygve, Svein, Kristin, Olav, Jan Erik, Bård, Daniel, Kristian, Elias, Henning, Jostein, Håkon O. and Nikolaj for interesting discussions of both relevant and non-relevant contents and breaks during long working days. Thanks to Håkon H. and Hans for help and guidance on technical matters. I would also like to thank the rest of the students and staff at the Nanoelectronic research group.

Lastly, I would thank my family for support during the project.

Oslo, May 2008

Håvard Pedersen Alstad

## **Contents**

| A۱ | bstrac | et                                                   | iii |

|----|--------|------------------------------------------------------|-----|

| Pr | eface  |                                                      | v   |

| 1  |        | oduction                                             | 1   |

|    | 1.1    | Motivation                                           | 2   |

|    | 1.2    | Previous Work                                        | 3   |

|    | 1.3    | Overview of the Thesis                               | 4   |

| 2  | Sub    | threshold Operation                                  | 7   |

|    | 2.1    | Introduction                                         | 7   |

|    | 2.2    | CMOS Power Consumption                               | 7   |

|    |        | 2.2.1 Traditional Modelling of Power Consumption     | 8   |

|    |        | 2.2.2 Leakage Current Problems in Modern CMOS System | 9   |

|    | 2.3    | Modelling of Subthreshold Leakage Current            | 10  |

|    | 2.4    | Lower Bounds of CMOS Supply Voltage                  | 11  |

|    | 2.5    | Sizing for Subthreshold Operation                    | 12  |

|    | 2.6    | Body-Bias Regulation                                 | 14  |

| 3  | Sea    | uential Computing                                    | 15  |

| _  | 3.1    | Flip-Flops                                           | 16  |

|    | 3.2    | Flip-Flop Performance Characterization               | 17  |

|    |        | 3.2.1 Timing and Delay                               | 17  |

|    |        | 3.2.2 Power Consumption                              | 19  |

|    |        | 3.2.3 Performance Metrics                            | 20  |

|    |        | 3.2.4 Metastability                                  | 20  |

|    | 3.3    | Flip-Flop Designs                                    | 21  |

|    | G: 1   | • •                                                  |     |

| 4  |        | e-Channel Attacks                                    | 23  |

|    | 4.1    | Introduction                                         | 23  |

|    | 4.2    | Theoretical Background                               | 23  |

|    |        | 4.2.1 Cryptography                                   | 23  |

|    |        | 4.2.2 Side-Channel Attacks                           | 24  |

|    | 4.3    | Countermeasures against Side-Channel Attacks         | 26  |

### CONTENTS

|   |      | 4.3.1          | Algorithmic Countermeasures                |         |      |       | 27       |

|---|------|----------------|--------------------------------------------|---------|------|-------|----------|

|   |      | 4.3.2          | Electronic Countermeasures                 |         |      |       | 27       |

| 5 | Adv  | anced E        | ncryption Standard Substitution Box Imp    | lem     | enta | atior | n 31     |

|   | 5.1  |                | Ivanced Encryption Standard                |         |      |       | 31       |

|   | 5.2  | Finite 1       | Field Arithmetic                           |         |      |       | 33       |

|   |      | 5.2.1          | Polynomial Representation of Finite Fields |         |      |       | 33       |

|   |      | 5.2.2          | Arithmetic Operations on Finite Fields GF  | $(2^n)$ |      |       | 34       |

|   |      | 5.2.3          | Multiplicative Inverse                     |         |      |       | 35       |

|   | 5.3  | Rijnda         | el S-Box                                   |         |      |       | 36       |

|   |      | 5.3.1          | S-Box Operation                            |         |      |       | 36       |

|   | 5.4  | S-Box (        | Circuit Implementation                     |         |      |       | 37       |

|   |      | 5.4.1          | Isomorphisms and Transformation            |         |      |       | 37       |

|   |      | 5.4.2          | Multiplicative Inverse Computation         |         |      |       | 38       |

|   |      | 5.4.3          | Pipelining                                 |         |      |       | 39       |

| 6 | Resi | ılts           |                                            |         |      |       | 41       |

| Ū | 6.1  |                | [                                          |         |      |       | 41       |

|   | 6.2  | -              | I                                          |         |      |       | 42       |

|   | 6.3  |                | II                                         |         |      |       | 42       |

|   | 6.4  |                | V                                          |         |      |       | 43       |

|   | 0.1  | Taper          |                                            |         |      |       | 10       |

| 7 | Disc | ussion         |                                            |         |      |       | 45       |

|   | 7.1  |                | izing Power Consumption                    |         |      |       | 45       |

|   | 7.2  |                | s Variations                               |         |      |       | 46       |

|   | 7.3  | Power          | Analysis Attack Resistance                 |         |      |       | 47       |

| 8 | Con  | clusion        |                                            |         |      |       | 49       |

|   | 8.1  | Future         | work                                       |         |      |       | 50       |

| 9 | Acro | nyms           |                                            |         |      |       | 53       |

| Α | Sche | ematic I       | Drawings and Transistor Sizing             |         |      |       | 55       |

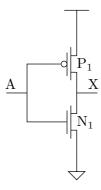

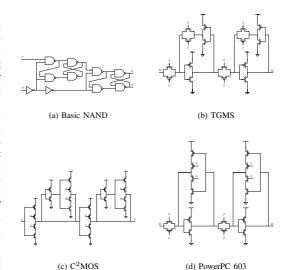

|   |      |                | ogic Functions                             |         |      |       | 55       |

|   |      |                | Inverter                                   |         |      |       | 55       |

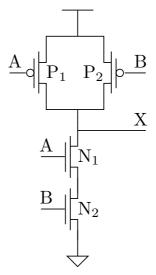

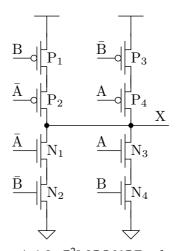

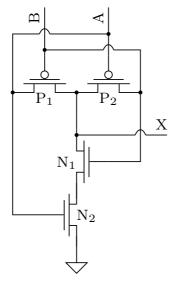

|   |      | A.1.2          | NAND                                       |         |      |       | 56       |

|   |      | A.1.3          | XOR                                        |         |      |       | 56       |

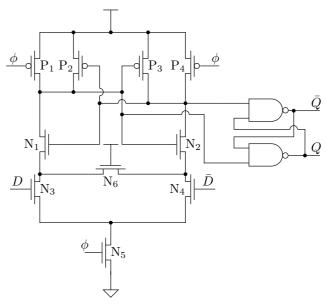

|   | Δ 2  | Flip-Flo       |                                            |         |      |       | 57       |

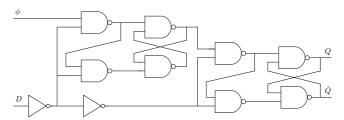

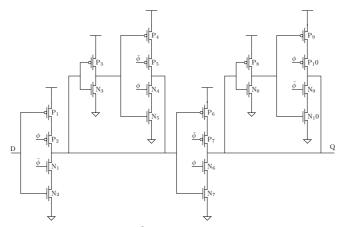

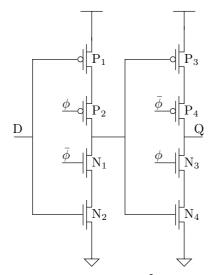

|   | 11.2 | A.2.1          | NAND-Master-Slave Flip-Flop                |         |      |       | 57       |

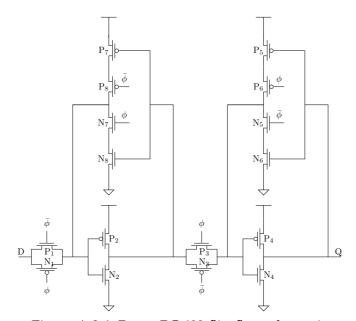

|   |      | A.2.1          | Transmission Gate Master Slave Flip-Flop   |         |      |       | 58       |

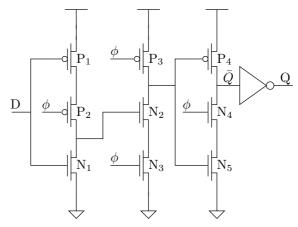

|   |      | A.2.2<br>A.2.3 | C <sup>2</sup> MOS Flip-Flop               |         |      |       | 59       |

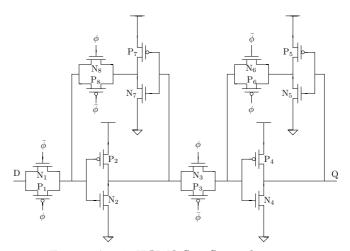

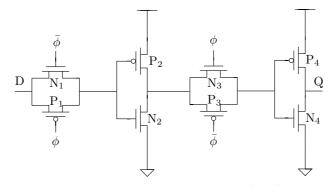

|   |      |                | PowerPC 603 Flip-Flop                      |         |      | • •   | 59       |

|   |      | A.2.4<br>A.2.5 |                                            |         |      |       | 60       |

|   |      |                | TSPC Flip-Flop                             |         |      |       |          |

|   |      | A.2.6          | Dynamic TGMS Flip-Flop                     |         |      | • •   | 60<br>61 |

|   |      | H.Z./          | DVHamic CEIVICO FIID-FIOD                  |         |      |       | n I      |

### **CONTENTS**

|     |            | A.2.8   | Sense-Amplifier Based Flip-Flop               | 62 |

|-----|------------|---------|-----------------------------------------------|----|

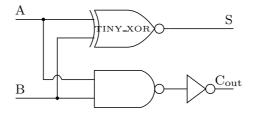

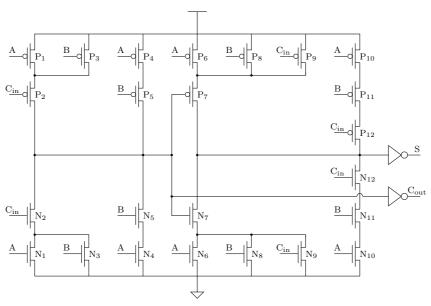

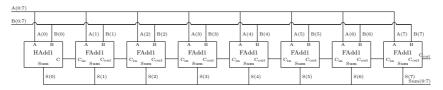

| 1   | <b>A.3</b> | Full-A  | dder                                          | 62 |

|     |            | A.3.1   | 1 Bit Half-Adder                              | 62 |

|     |            | A.3.2   | 1 Bit Full-Adder                              | 62 |

|     |            | A.3.3   | 8 Bit Full-Adder                              | 63 |

| 1   | 4.4        | S-box   |                                               | 64 |

|     |            | A.4.1   | Isomorphism                                   | 64 |

|     |            | A.4.2   | Inverse Isomorphism and Affine Transformation | 64 |

| В   | Add        | itional | Simulations                                   | 67 |

| ]   | 3.1        | Subth   | reshold Transistor Sizing                     | 67 |

|     |            | B.1.1   | Inverter                                      | 67 |

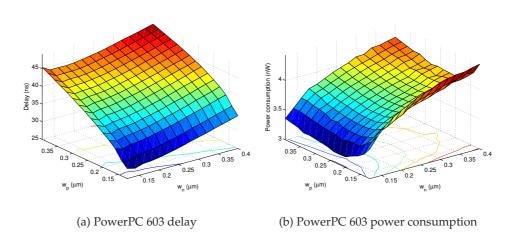

|     |            | B.1.2   | PowerPC 603                                   | 67 |

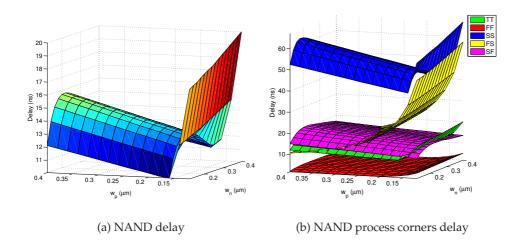

|     |            |         | NAND                                          | 67 |

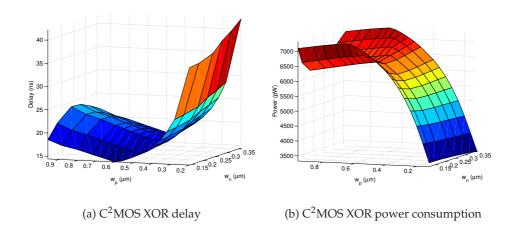

|     |            | B.1.4   | $C^2MOS XOR$                                  | 69 |

| ]   | 3.2        | S-Box   | Output                                        | 69 |

| Bib | liog       | raphy   |                                               | 71 |

| Pap | er I       |         |                                               | 79 |

| Pap | er I       | [       |                                               | 85 |

| Pap | er I       | II      |                                               | 91 |

| Pap | er I`      | V       |                                               | 95 |

## Chapter 1

## Introduction

Techniques for reducing the power consumptions in power-hungry Very Large Scale Integrated Circuit (VLSI) systems are presently becoming a major challenge and obstacle for future development of Complementary Metal-Oxide Semiconductor (CMOS) technology. The International Roadmap for Semiconductors states that power management is now the primary issue across most application segments [1]. In a 45 nm CMOS process, you can fit more than 2000 transistors across the width of a human hair [2]. When all transistors switch billions of times per second they consume an enormous amount of energy compared to the area, which is dissipated as heat.

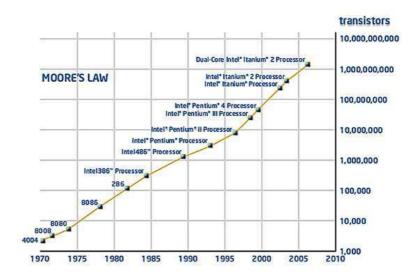

Moore presented in 1965 a prediction of further downscaling of Integrated Circuit (IC) technology by doubling the transistor density every 18 months [3]. Fig. 1.1 illustrates the exponential increase in transistor count in Intel ®Processors over the last 37 years. The increased packing density has been accompanied with increased speed, and has lead to an enormous increase in heat generation. The total chip performance is limited by the thermal dissipation capability of the mounted IC package of many of today's circuits [4].

With further downscaling of CMOS technology into deep submicron region even more transistors will be squeezed into an even smaller area. Power consumption in CMOS devices must be reduced to allow further development.

Another recent topic of interest, with the increased demand for secure communication presently is side-channel attacks. A cryptographic cipher implemented in an IC produces variation in power consumption and electromagnetic radiation due to switching activity of transistors. These variations are easily measurable with physical access to the IC and may be used to extract internal information from the circuit. With increased strengthening of cryptographic algorithms against cryptoanalysis, several types of attacks exploiting this physical emitted information have been

Figure 1.1: Moore's law Microprocessor Chart. Intel ®Corporation 2007

reported (e.g. [5, 6, 7]). Physical attacks on the implementation of the circuit, exploiting physical measurable information emitted by the device are referred to as side-channel attacks.

Side-channel attacks have become a major security threat to implementation of modern cryptographic ciphers immune to cryptoanalysis attacks. An increasing demand for secure data communication makes it more important to design with protection against side-channel attacks in mind for certain applications. Attacks on modern cryptographic ciphers have been reported to extract the correct 128 bit secret key within 3 minutes [8].

This thesis addresses both the performance of sequencing elements in the subthreshold region and techniques for improving the resistance against power analysis attacks with subthreshold operation in 4 papers included in the thesis.

#### 1.1 Motivation

Power consumption management is becoming of primary concern in the design of modern IC. Subthreshold operation is attained by reducing the operating voltage of the chip below the transistors threshold voltage. Reducing the power supply voltage is regarded as the most direct and dramatic means of reducing power consumption [9]. Subthreshold operation results in huge decrease of power consumption at the expense of decreased maximum switching frequency. Operating CMOS circuits in their subthreshold region is a promising method for reducing the power dissipation of ultra-low-power-application.

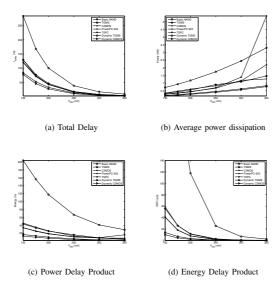

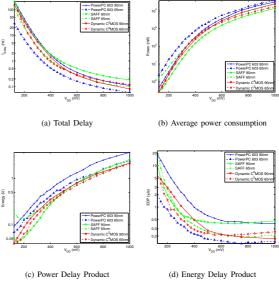

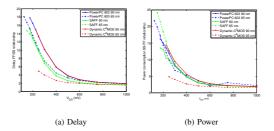

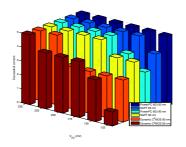

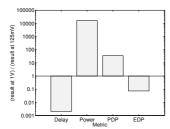

Few studies have been done on performance of sequencing elements in the subthreshold region. As sequencing elements play an important part of clocked sequential circuit systems, it is important to have a good understanding of which type of design to choose in different applications in a subthreshold CMOS system. In this thesis different flip-flop designs commonly used in superthreshold systems are compared in subthreshold operation. The comparison is done with respect to delay time, power consumption, Power-Delay Product and Energy-Delay Product. Process corner performance is also simulated.

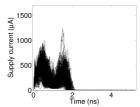

Increased resistance against power analysis attacks is obtained by reducing the signal magnitude [5]. Subthreshold operation reduces the signal amplitude significantly and can be used to increase resistance against side-channel attacks by reducing the power consumption. Reducing the signal amplitude by reducing the supply voltage makes it harder to measure the variation in power consumption. Normal arithmetic functions and a cryptographic function, the Advanced Encryption Standard (AES) S-box operation, are tested for improved power analysis resistance with subthreshold operation through simulations.

#### 1.2 Previous Work

Since the early years of CMOS technology, it has been well known that the power consumption is reduced when lowering the supply voltage. A CMOS counter circuit using reduced supply voltage was presented by Leuenberger and Vittoz in 1969 [10]. The effect of voltage scaling for reducing the power consumption of a CMOS counter circuit was explored. Operating transistors in the subthreshold region has been a well known method for reducing the power consumption for a long time. In 1972, Swanson and Meindl explored the lower bounds of supply voltage [11], which they derived as 8kT/q, approximately 200 mV at room temperature. This limit has later been reduced.

Subthreshold operation has gained renewed research interest in recent years as the demand for low power devices has increased. Research activity on the subthreshold operation increased in the early 90's. E.g. Burr and Shott reported an encoder/decoder circuit in 1994 operating at 200 mV [12].

In this millennium there has been a lot of research on subthreshold operation, e.g. at Massachusetts Institute of Technology, Purdue University and University of California, Berkeley. Some subthreshold circuit implementations are listed in Tab. 1.1. Works in the area of minimizing energy consumption [13, 14, 15], optimizing devices' performance [16] and increasing the robustness of subthreshold logic [17] are also worth mentioning. After this work was initiated the only extensive work known on sequencing elements in subthreshold operation is a comparative study on flip-flops by Fu

Table 1.1: Overview of some subthreshold applications

| Year | Application                             | Ref  |

|------|-----------------------------------------|------|

| 1994 | Encoder-decoder circuit at 200 mV       | [12] |

| 2005 | FFT-processor at 180 mV                 | [15] |

| 2006 | SRAM circuit at 190 mV                  | [19] |

| 2007 | Add-Compare-Select (ACS) unit at 180 mV | [20] |

| 2007 | SRAM circuit at 160 mV                  | [21] |

| 2007 | Programmable Register file at 200 mV    | [22] |

| 2008 | CPU processor below 200 mV              | [23] |

and Ampadu published in 2007 [18].

Side-channel attacks on electronic circuit was first reported by Kocher *et al.* in 1996 [24]. Three years later Kocher *et al.* introduced power analysis attacks [5]. After the theoretical introduction to these attacks by Kocher *et al.* the topic has gained much interest in recent years. Practical implementations of attacks have been presented, as well as means of improving resistance against attacks.

#### 1.3 Overview of the Thesis

This thesis examines subthreshold operation for reducing power consumption and protection against power analysis attacks of digital CMOS circuits.

The thesis includes a collection of 3 published papers and one unpublished paper, which will be submitted for conference inclusion.

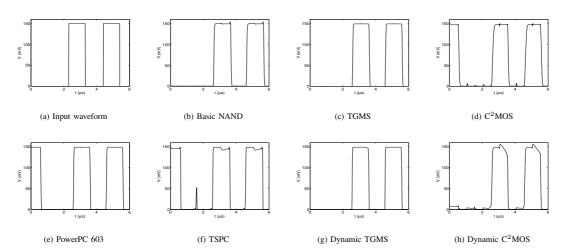

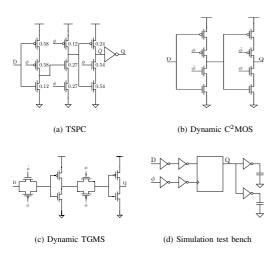

- Paper I presents seven subthreshold flip-flop cells characterized with respect to metrics such as speed, power dissipation, Power Delay Product and Energy-Delay Product.

- Paper II takes a deeper look at three flip-flop cells, which are characterized both in a 65 nm and 90 nm process. Differences between technologies are presented and simulations in different process corners are performed.

- Paper III examines the effect of subthreshold operation for increasing resistance against power analysis attacks by simulations on an 8-bit full-adder circuit.

- Paper IV contains further examinations on the effect of subthreshold operation for increased resistance against power analysis attacks on the implementation of the AES S-box.

In addition to the technical papers, a separate introduction to the work (this part) is organized as followed:

- Chapter 1 presents the motivation for working with digital subthreshold CMOS and lists a selection of previous works done on topics of interest.

- Chapter 2 gives an introduction to subthreshold CMOS modelling and power estimation.

- Chapter 3 presents the operation of flip-flops and different measures for comparing the performance of different flip-flops.

- Chapter 4 gives an introduction to side channel attacks and reported countermeasures against them.

- Chapter 5 gives a brief introduction to the Advanced Encryption Standard and presents the implementation of the Rijndael S-Box.

- Chapter 6 presents a summarization of the included papers.

- Chapter 7 is a discussion of this thesis contributions.

- Chapter 8 gives a summarization and conclusion to the work done in this thesis, and lists some ideas for future work in the field discussed.

Two appendices are also included:

- Appendix A includes schematic drawings and transistor sizing of CMOS cells used in this thesis and included papers.

- Appendix B presents additional simulation results (not published).

## **Chapter 2**

## **Subthreshold Operation**

#### 2.1 Introduction

Among the most promising methods for reducing the power consumption of VLSI, reducing the power supply voltage offers the most direct and dramatic means of reducing the power consumption [25, 9]. Presently, subthreshold operation is considered to be the most energy-efficient solution for low-power applications where performance is of secondary importance [15, 26].

A transistor is said to operate in its subthreshold region when the gate-source voltage,  $V_{\rm gs}$ , is below the absolute voltage of the transistor's threshold voltage,  $V_{\rm t}$ . The power supply voltage,  $V_{\rm DD}$ , is reduced below the threshold voltage for ensuring subthreshold operation.

As the technology evolution proceeds, mobile electronic devices are continuously emerging in new areas with new usability. This leads to an increasing demand for device designs offering low power consumption. Reducing the power consumption with subthreshold operation has been known for decades [11]. In recent years, subthreshold operation has received more attention due to the increasing demand for power-efficient electronics. Applications well suitable for subthreshold operations include wearable medical equipment such as hearing aids and pacemakers, wristwatch computers, self-powered devices and wireless sensor networks [27, 15, 28].

### 2.2 CMOS Power Consumption

CMOS has emerged as the mainstream technology in modern VLSI design during the past decades. A major factor contributing to the success of CMOS over the past decades has been its power consumption characteristic. In traditional CMOS technologies operating with a power supply voltage well above the transistor's threshold voltage,  $V_t$ , significant

power consumption only occurs during transistor switching between on and off state.

When estimating the total power consumption in a device or system two different power dissipation components must be taken into account. *Dynamic power consumption* is due to charging and discharging of load capacitance and short-circuit current drawn directly from the power supply to ground when both pMOS and nMOS transistors are partially on. *Static power consumption* is always present in a powered up circuit. This component is due to non-ideal currents of CMOS transistors.

The total power consumption can be expressed as the sum of these two components [29]:

$$P_{\text{total}} = P_{\text{static}} + P_{\text{dynamic}} \tag{2.1}$$

Static power consumption has traditionally been a negligible part of the total power consumption compared to the dynamic power consumption. But due to increased leakage it must be taken into account in modern CMOS processes. The understanding of the static power consumption is therefore important for estimating power consumption in modern CMOS technologies. The static power consumption is a composition of different leakage currents. Static power dissipation is mainly due to *subthreshold leakage current* and *gate leakage current* [29]. Other leakage effects include junction leakage, hot-carrier injection leakage, gate-induced drain leakage (GIDL) and punch-through leakage currents [30].

#### 2.2.1 Traditional Modelling of Power Consumption

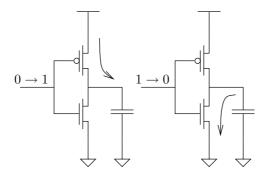

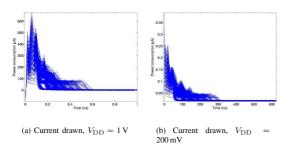

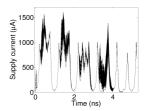

The dynamic component of the power consumption has been dominating in traditional CMOS technologies, and static power consumption has usually not been taken into account when estimating the total power consumption. Taking only the dynamic power consumption into account, power dissipation occurs only when a transistor changes state by charging and discharging the load capacitance. The current drawn from the power supply during these transitions is illustrated in Fig. 2.1. In a digital integrated circuit system such capacitances are mainly input gates of the next transistors in the signal path.

The average dynamic power consumption is a square function of the supply voltage  $V_{\rm DD}$ , and can be approximated to [31]:

$$P_{\rm dynamic} = \frac{1}{2} \cdot \alpha \cdot C_{\rm L} \cdot V_{\rm DD}^2 \cdot f \tag{2.2}$$

where  $\alpha$  is the probability of a signal transition within a clock period (0  $\leq \alpha \leq$  1),  $C_L$  is the circuit capacitance to switch,  $V_{DD}$  is the power supply voltage and f is the clock frequency.

Figure 2.1: Current flows in a CMOS inverter during transitions

#### 2.2.2 Leakage Current Problems in Modern CMOS System

The instantaneous power, P(t), drawn from the power supply is proportional to the supply current,  $i_{\rm DD}(t)$ , and the supply voltage,  $V_{\rm DD}$ . Over the past decades  $V_{\rm DD}$  has decreased from typical 5 V down to typical 1 V in present state-of-the-art processes. As the dynamic power consumption quadratically depends on the supply voltage, according to Eq. 2.2, a result of this has been a dramatic reduction in the dynamic power consumption. While the dynamic power consumption has decreased, the static leakage currents have simultaneous increased, due to thinner gate-channel isolation layer and lowered threshold voltage.

Subthreshold leakage current is the current flowing between the source and drain node of a Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) when the gate-to-source voltage,  $V_{\rm gs}$ , is below the threshold voltage,  $V_t$ .

As the leakage current increases exponential when threshold voltage decreases, leakage is emerging as a major problem for modern deep submicron CMOS processes. Subthreshold leakage power can consume as much as 60 % of the total power in a 65 nm technology [32]. A formula for modelling the subthreshold leakage current is given in Sec. 2.3.

Although subthreshold leakage is considered an undesirable effect by most digital circuits, it is the cornerstone in subthreshold circuits. Subthreshold circuits utilize the leakage current as the conduction current.

The gate leakage current is the current flowing through the oxide layer insulating the gate from the channel. Thickness of the oxide layer has decreased proportional to  $V_{\rm DD}$  [33]. The probability of carriers tunneling through the insulating layer increases exponentially with decreased oxide thickness. For gate oxide thickness less than 15-20 Å, gate leakage current becomes comparable to subthreshold current [29]. The gate leakage current contribution was simulated to 40 % of the total inverter off current in a 90 nm process in [13]. The contribution to the total leakage current is

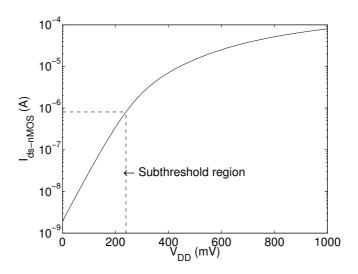

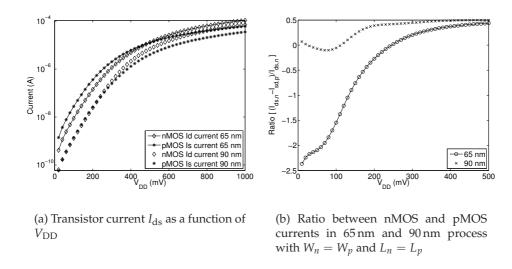

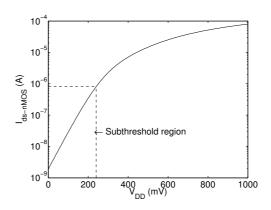

Figure 2.2: nMOS transistor current  $I_{ds}$  as a function of  $V_{DD}$ ,  $V_{gs} = V_{DD}$

rapidly diminished when the supply voltage is decreased.

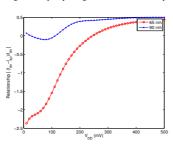

The on-current going through a N-channel MOSFET (nMOS)-transistor,  $I_{\rm ds}$ , in a 90 nm CMOS process is plotted as the function of the power supply voltage,  $V_{\rm DD}$ , in Fig. 2.2. As seen in the figure, the  $I_{\rm on}/I_{\rm off}$  ratio can be reduced with as much as a factor of approximately  $10^3$  if  $V_{\rm DD}$  is reduced from  $1\,\rm V$  down to  $150\,\rm mV$ .

By operating the circuit's transistors in their subthreshold region, transistors are never fully turned on. Instead they are varying between being turned off and partially turned on, starting to conduct subthreshold leakage current to a greater degree. While the dynamic power consumption increases quadratically with the supply voltage, the maximum clock frequency increases only linearly with the supply voltage [4]. The static power consumption contribution exceeds the dynamic when operating at very low supply voltage [13].

When transistors are operated in the subthreshold region, power consumption is dramatically reduced without the need for major design changes of the circuit. This region has been regarded as the 'OFF' region in traditional circuit design.

### 2.3 Modelling of Subthreshold Leakage Current

It is essential to use an accurate model for calculating the subthreshold leakage current and other currents present in this region for estimation of power consumption. A list of important parameters influencing a transistor's subthreshold drain-source current is given in Tab. 2.1.

The drain current of a nMOS transistor operating in subthreshold,

| Symbol               | Description                          | Unit              |

|----------------------|--------------------------------------|-------------------|

| $v_T = \frac{kT}{q}$ | Thermodynamic Voltage                | V                 |

| $V_t$                | Threshold voltage                    | V                 |

| $V_0$                | Early voltage                        | V                 |

| n                    | Slope factor                         | no unit           |

| μ                    | Mobility of electrons in the channel | $m^2/(V \cdot s)$ |

| $C_{ox}$             | Oxide capacitance per unit area      | F/m <sup>2</sup>  |

| $\frac{W}{L}$        | Width/length ratio                   | no unit           |

| К                    | Technology dependent constant        | no unit           |

Table 2.1: Important MOSFET subthreshold current model parameters

$V_{\rm gs} < V_t$ , can be modelled as [26]:

$$I_{\rm ds} = I_0 e^{\frac{\kappa V_{\rm gs}}{v_T}} e^{(1-\kappa)\frac{V_{\rm bs}}{v_T}} \left( 1 - e^{\frac{-V_{\rm ds}}{v_T}} + \frac{V_{\rm ds}}{V_0} \right)$$

(2.3)

where  $I_0$  is the zero-bias current for the device, as given in Eq. 2.4.  $V_{\rm gs}$  is the gate-to-source potential,  $V_{\rm ds}$  is the drain-to-source potential and  $V_{\rm bs}$  is the substrate-to-source potential (body-bias).  $V_0$  is the Early voltage, proportional to the channel length.  $\kappa$  gives the effectiveness for which the gate potential is controlling the channel current, normally in the range 0.7-0.75 [26]. The thermal voltage,  $v_T$ , is calculated as  $v_T = kT/q$ , where k is the Boltzmann's constant, T is the temperature and q is the elementary charge. At room temperature ( $T = 300 \, {\rm K}$ ),  $v_T$  is about 26 mV. The threshold voltage,  $V_t$ , varies with length, width,  $V_{\rm ds}$ ,  $V_{\rm bs}$ , temperature and processing [29], as well as the body effect as described in Sec. 2.6.

Typical parameters for a 2  $\mu$ m n-well process are  $I_0=0.72$  aA,  $\kappa=0.75$  and  $V_0=15$  V [26]. The current changes by a factor 10 for an 80 mV change in  $V_{gs}$  or a 240 mV change in  $V_{bs}$  (up to 100 nA, which is the limit of the subthreshold region).

$I_0$  may be expressed as [34]:

$$I_0 = 2n\beta v_T^2 = 2n\mu_n C_{ox} \frac{W}{L} v_T^2$$

(2.4)

where  $\beta$  is the technology dependent transconductance factor.

### 2.4 Lower Bounds of CMOS Supply Voltage

Swanson and Meindl derived in 1972 equations suggesting a minimum useful supply voltage of 8kT/q for inverters operating in weak inversion

Table 2.2: Ideal-case minimum supply voltage  $V_{\mathrm{DD}}$  for given circuit design

constraints [4]

| Constraint              |                   | $V_{ m DDmin}$         | $V_{ m DDmin}$ |

|-------------------------|-------------------|------------------------|----------------|

|                         |                   | $(T = 300 \mathrm{K})$ | $[v_T]$        |

| $A_{max} > 1$           | (ring oscillator) | 36 mV                  | 1.40           |

| NM > 10%                | (inverter)        | 55 mV                  | 2.13           |

| $A_{max} > 4$           | (standard design) | 83 mV                  | 3.22           |

| $F_U > 9$               | (fan-in of 3)     | 83 mV                  | 3.22           |

| $I_{on}/I_{off} > 10^4$ | (dynamic logic)   | 238 mV                 | 9.22           |

[11]. At room temperature this compares to approximately 200 mV. By further research in the area, Schrom *et al.* reported in 1996 an analytic absolute lower bound of supply voltage [4]. This absolute lower bound assumes ideal and perfectly symmetrical devices, not likely achievable by any CMOS technology according to [35]. The lowest bounds of supply voltage for a CMOS inverter is 36 mV at a temperature of 300 K, corresponding to the *minimum-inverter-gain criterion*.

Achievable values for minimum supply voltage for various design constraints, calculated and presented in [4], are listed in Tab. 2.2. Minimum supply voltage  $V_{\rm DD}$  is given in millivolts on a temperature of 300 K, and may be estimated for other temperatures by a factor of  $n = S/(v_T \ln(10))$  where S is an achievable average gate swing as a worst-case estimate for subthreshold operation [4].

A minimum of logic function, such as NAND, NOR and XOR, is required to operate successfully in most circuit implementations for practical use. In practical use a minimum value of  $V_{\rm DD}$  may be around 83 mV, according to Tab. 2.2.

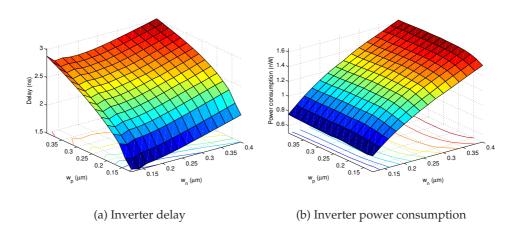

### 2.5 Sizing for Subthreshold Operation

For optimal performance, transistors in a pull-up and pull-down network should be able to drive the same current. In traditional design, pMOS sizing is done proportionally to nMOS with the relationship  $W_p = 2 \cdot W_n$ . But the optimum pMOS/nMOS ratio varies with the supply voltage. In the subthreshold region it is highly dependent on process variation as well [15]. Requirements for power consumption, minimum supply voltage and yield requirements must be taken into accounts when dimensioning transistors.

Minimum sized devices minimize power consumption but can reduce the functionality of circuits at low supply voltages, thus limiting the minimum supply voltage [36]. Minimum sized devices are theoretically

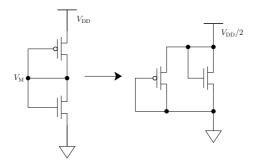

Figure 2.3: Small-signal equivalent of inverter for width optimization

Figure 2.4: Transistor channel conduction at different supply voltages

optimal for reducing energy per operation when accounting for the impact of sizing on voltage and energy consumed [13].

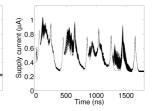

Symmetrical devices give minimum  $V_{\rm DD}$  operation [36]. The optimum pMOS/nMOS width ratio for minimum  $V_{\rm DD}$  can be obtained by comparing currents in the devices. With the setup from Fig. 2.3, the transistor current as a function of  $V_{\rm DD}$  is plotted in Fig. 2.4(a), with  $V_{\rm gs}=V_{\rm DD}$  for the STMicroelectronics 90 nm and 65 nm general purpose processes. The corresponding n/p ratios are calculated and plotted in Fig. 2.4(b). For both plots minimum sized transistors with  $W_n=W_p$  and  $L_n=L_p$  have been used. Remembering that the current through the transistor is linear dependent on the W/N the ideal  $W_p/W_n$  ratio can be found.

The variation in threshold voltage due to random doping fluctuations is proportional to  $1/\sqrt{WL}$ , causing minimum sized devices to produce the worst case random  $V_t$  variations [14].

### 2.6 Body-Bias Regulation

The body effect is a second-order effect, occurring due to potential difference between the source and body of a transistor [29]. It can be modelled as an increase in the threshold voltage  $V_t$  for a nMOS transistor that occurs when the source and substrate have different voltage potentials. With this effect taken into account, the threshold voltage for a n-channel transistor is[37]:

$$V_{\rm t} = V_{\rm t0} + \gamma \left( \sqrt{V_{\rm sb} + |2\Phi_{\rm F}|} - \sqrt{|2\Phi_{\rm F}|} \right)$$

(2.5)

where  $V_{t0}$  is the threshold voltage without body effect ( $V_{sb}=0$ ),  $\Phi_F$  is the difference between the Fermi potential of the substrate and intrinsic silicon (approximated to 0.35 V at room temperature for typical doping levels). The factor  $\gamma$ , often called the *body-effect constant*, is:

$$\gamma = \frac{\sqrt{2qN_{\rm A}K_{\rm S}\varepsilon_0}}{C_{\rm ox}} \tag{2.6}$$

where  $N_{\rm A}$  is the doping concentration,  $K_{\rm S}$  is the relative permittivity of silicon,  $\varepsilon_0$  is the permittivity of free space and  $C_{\rm ox}$  is the gate oxide capacitance. The body-effect constant is proportional to the doping concentration.

Body-bias regulation can improve the inverse subthreshold slope *S* due to reduced short-channel effects and reduce the junction capacitances by increasing the junction depletion widths [16]. These effects lead to faster operation and lower power consumption in a subthreshold device. For example, a 19% decrase in the switching delay and 30% reduction in the Power-Delay Product (PDP) of an inverter is obtained in [16] by applying a reverse body-bias of 150 mV.

Body-bias regulation has been presented as a promising method for decreasing  $V_t$  variations [38]. Threshold voltage is stabilized by regulating the back-gate voltage of transistor with a small bias regulator circuit.

## **Chapter 3**

## **Sequential Computing**

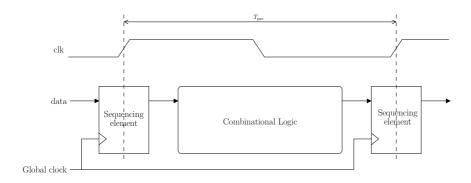

A major part of digital VLSI systems is designed as a *clocked sequential system*, using a global clock to synchronize the system. The activity of such a system is controlled by the global clock, which triggers registers all over the system at the same time.

A *sequencing element*, connected to the global clock, is used to synchronize data. Combinational logic is placed between the sequencing elements, as illustrated in Fig. 3.1. The purpose of a sequencing element is to enforce sequence, to distinguish the current token from the previous or next token [29].

The two most commonly used sequencing elements are *flip-flops* and *latches*. Flip-flops and latches can mainly be separated into how the output signal is changed when the input signal changes. When the input signal flows directly through to the output the element is said to be *transparent*. Latches are transparent while the clock signal is high, while flip-flops are not transparent at any time.

Figure 3.1: Clocked sequential system

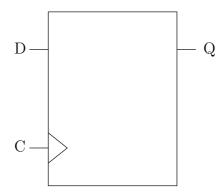

Figure 3.2: D flip-flop symbol

### 3.1 Flip-Flops

Flip-flops are an important building block in modern digital VLSI systems. Some of the major usage areas of flip-flops are in registers, pipelines and state machines, ensuring sequencing of data.

A flip-flop has the ability to read an input value, save it for some time and then write the stored value somewhere else, even if the element's input value has subsequently changed.

Based on the comparison of the power breakdown for different elements in VLSI chips, latches and flip-flops are the major source of the power consumption in synchronous systems [39]. Flip-flops have a direct impact on power consumption and speed of VLSI systems. Therefore study on low-power performance of flip-flops are important. When estimating the power dissipation of a system, flip-flops may be a major power consumption component.

In this thesis, the *delay flip-flop* (D flip-flop) is used [40]. This type of flip-flops can be interpreted as a primitive delay line or zero-order hold, since the data is posted at the output one clock cycle after it arrives at the input. It is called delay flip-flop because the output takes the value of data-in from the previous clock period.

The operation of a D flip-flop can be expressed as:

$$Q_{\text{next}} = D \tag{3.1}$$

where  $Q_{\text{next}}$  is the output value in the next clock period and D is the input value sampled at the rising edge of the clock signal for the start of the clock period.

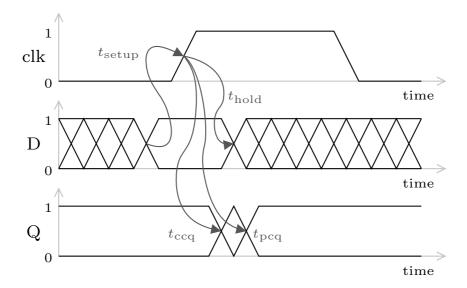

Figure 3.3: Flip-flop timing diagram

### 3.2 Flip-Flop Performance Characterization

Significant parameters in characterizing a flip-flop's performance are its delay time and power dissipation. An optimal flip-flop design has low power consumption, imposes no delay and gives a valid output at all time. Trade-offs between these parameters must be done in practical implementation.

#### 3.2.1 Timing and Delay

For estimating the performance of a flip-flop, three important timings and delays are used: (1) propagation delay, (2) setup time and (3) hold time. Setup and hold time define the relationship between the clock and input data, while the propagation delay defines the relationship between the internal delay for the input signal to propagate through the flip-flop and change the output signal.

The total delay of a sequencing element can be expressed as the time from the input signal changes its state to the output signal is stabilized.

A flip-flop can capture an input signal even though it arrives later than the setup time, but the propagation delay might increase, resulting in a large total delay[29].

#### **Propagation Delay**

The propagation delay of a flip-flop is defined as its clock-to-output delay. This equals the maximum delay from the arrival of the clock's active edge

#### **Sequential Computing**

to the output of the flip-flop is considered stable. Usually the propagation delay differs from low to high transition and high to low transition. By definition, the delay is the maximum value of these two delay:

$$t_{pcq} = \max\left(t_{pcq_{LH}}, t_{pcq_{HL}}\right) \tag{3.2}$$

#### **Clock Contamination Delay**

The clock contamination delay is the minimum time from the clock changes to the output is available that occurs when the data input arrives early. I.e. the time it takes from the clock goes high to a valid output signal is available.

$$t_{ccq} = \max\left(t_{ccq_{LH}}, t_{ccq_{HL}}\right) \tag{3.3}$$

#### **Setup Time**

The input must be stable for some time before the flip-flop triggers at the clock edge. The setup time is defined as the time the data value must remain stable around the arrival of the clock's active edge to ensure that the flip-flop retains the proper output value.

The setup time may differ for a low-to-high and high-to-low transition. Setup time is by definition the maximum of these values:

$$t_{\text{setup}} = \max(t_{\text{setup,LH}}, t_{\text{setup,HL}})$$

(3.4)

#### **Hold Time**

After the clock signal has changed, the input must be hold for a period of time to allow the signal to propagate through the flip-flop for ensuring a stable output. This delay time is called *hold time*. The hold time may be negative, which means that the input signal may change before the clock changes and still ensuring the proper output value. As for other timing measurements, the hold time may differ for a low-to-high and high-to-low transition. The hold time is defined as:

$$t_{\text{hold}} = \max\left(t_{\text{hold,LH}}, t_{\text{hold,HL}}\right) \tag{3.5}$$

#### **Total Delay**

The delay of a flip-flop can be expressed as the time taken from the input changes its state to the output has stabilized. The total delay can be expressed as  $t_{\rm delay} = t_{\rm setup} + t_{\rm pcq}$ , where  $t_{\rm setup}$  is the time taken for the input to propagate and stabilize in the flip-flop, and  $t_{\rm pcq}$  is the time taken from the clock goes high to a valid output Q is available.

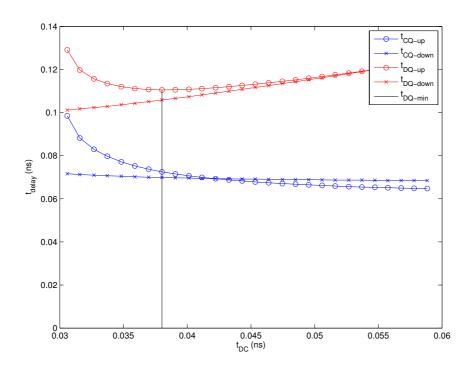

Figure 3.4: PowerPC 603 flip-flop:  $t_{\text{delay}}$  vs  $t_{\text{setup}}$

In Fig. 3.4 simulation of  $t_{\rm delay}$  vs.  $t_{\rm setup}$  has been done at  $V_{\rm DD} = 200$  mV. It is clearly shown how the delay is directly dependent on the time the input signal arrives in relationship to the clock signal. At the left side of the plot, the input signal exceeds the clock edge, and the output is not valid. At the right side the output signal monolithically grows due to increased  $t_{\rm setup}$ .

#### 3.2.2 Power Consumption

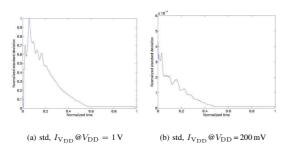

A common method for measuring the power consumption of a flip-flop is to operate the flip-flop at maximum operating frequency with a maximum power consumption pattern applied on the input. The power consumption is then measured as the average supply current drawn by the flip-flop with input buffers and some load taken into account.

The average power consumption *P* can be defined:

$$P = i_{V_{\rm DD}avg} \cdot V_{\rm DD} \tag{3.6}$$

where  $i_{V_{\text{DD}}avg}$  is the average current drawn from the power supply by the circuit over the time being measured and  $V_{\text{DD}}$  is the power supply voltage.

#### 3.2.3 Performance Metrics

#### **Power-Delay Product**

Both power and delay are metrics which can be adjusted individually. Therefore they are usually not considered as good figure-of-merits for a design or circuit. The Power-Delay Product (PDP) is the product of delay time and power consumption, taking both metrics into account. PDP is considered a good figure of merit for a circuit's performance.

PDP is calculated as:

$$PDP = t_{\text{delay}} \cdot P \tag{3.7}$$

where  $t_{\text{delay}}$  is the delay found in Sec. 3.2.1 and P is the power consumption, as defined in Sec. 3.2.2.

#### **Energy-Delay Product**

The Energy-Delay Product (EDP) weights the execution time more than PDP. EDP is considered a relatively implementation neutral metric, causing architectural improvements contributing most to both performance and energy efficiency to stand out [41].

EDP can be expressed as:

$$EDP = PDP \cdot t_{\text{delay}} = t_{\text{delay}} \cdot t_{\text{delay}} \cdot P$$

(3.8)

where PDP is the Power-Delay Product found in Sec. 3.2.3,  $t_{\text{delay}}$  is the delay found in Sec. 3.2.1 and P is the power consumption, as defined in Sec. 3.2.2.

#### 3.2.4 Metastability

A flip-flop is a *bistable device*, meaning it has two stable states (0 and 1).

The binary decision which the flip-flop must take to set the output can take an unbounded amount of time in the case of colliding inputs [42]. When a flip-flop experience this, it is said to be in a *metastable state* where the output is at an indeterminate level between 0 and 1 [29].

When the output of a flip-flop in a metastable state is sampled by other digital circuitry, non-binary signals will propagate through the binary systems. This effect is called a *synchronization failure*.

Metastable states cannot be totally avoided when designing a systems, but the probability of occurrence can be made reasonably small with careful consideration of timing.

### 3.3 Flip-Flop Designs

The basic method for designing a flip-flop cell is to combine two latches with complementary non-overlapping clock signals. Two common types of characterization of flip-flop designs is to separate them into *static* and *dynamic* designs.

Static flip-flop designs have some sort of feedback to retain its output value indefinitely. Dynamic flip-flop designs do not have this type of feedback, generally maintaining their value as charge on capacitors. If the flip-flop is not refreshed for a long period of time, the charge will leak away [29]. A static master-slave flip-flop cell can be made dynamic by removing its feed-back elements. Dynamic flip-flops are prone to internal dynamic node discharge. The storage capacitances in a dynamic flip-flop must be periodically refreshed, otherwise the charge on these nodes will leak away resulting in invalid data [39].

Another commonly used flip-flop design is sense-amplified based flip-flops. A sense-amplified based flip-flop has a sense amplifier on its input gates (D and its complementary value). The sense amplifier is followed by a normal static latch to retain the output signal.

Many other flip-flop architectures have been presented. For example, the Semi-Dynamic Flip-Flop (SDFF) and Hybrid Latch Flip-Flop (HLFF) designs are commonly used in conventional circuit implementations. Due to their high power consumption these cells have not been considered in this thesis [39].

Schematic drawings and transistor sizings for flip-flops reviewed in Paper I and II are shown in A.2.

## **Chapter 4**

## Side-Channel Attacks

#### 4.1 Introduction

Cryptography is extensively used in modern electronic communication for protecting message secrecy, ensuring personal privacy and proving message authenticity. Cryptographic algorithms have after extensive academic research over the past decades evolved to be secure against known mathematical cryptoanalysis attacks. However, in recent years several attacks based on the physical implementation of electronic cryptographic systems have been presented.

A cryptographic system is only as secure as its weakest link. It has become of primary concern for an increasing number of researchers that the physical implementation is the weakest link of many cryptographic systems.

This chapter intend to investigate the vulnerability against *side-channel attacks* in modern cryptographic circuits. Side-channel attacks use physical measurements of informations such as time delay, power consumption and electromagnetic radiation for finding secret keys inside the circuit.

Theoretical background on the nature of power consumption in CMOS technology, an introduction to cryptography and the different types of side-channel attacks is given in Sec. 4.2. In Sec. 4.3, proposed countermeasures against side-channel attacks are presented.

### 4.2 Theoretical Background

#### 4.2.1 Cryptography

The term cryptography refers to the study of secret messages [43]. In modern communication over the Internet, cryptography is of primary importance for secure communication, keeping privacy, ensuring message authenticity and access control. Information transmitted over the Internet

passes nodes neither controlled by the sender nor the receiver and may easily be eavesdropped.

The purpose of an encryption algorithm is to protect the secrecy of messages sent over an insecure channel [44].

Lots of processing are required for encryption and decryption of data. With large data flows, dedicated cryptographic hardware is used to keep up with the speed. Dedicated cryptographic hardware is also considered to be more secure than software implementation because secret cryptographic keys can be kept in a controlled environment, specially designed for secure keeping. Nevertheless, cryptographic ICs are also vulnerable against break-in-attempts. Attempts on breaking in through the physical implementation of a cryptographic IC are called *side-channel attacks*.

A *cipher* is a cryptographic algorithm for transposing a known input text to be hidden from eavesdropping, *plaintext*, into a ciphertext. A *ciphertext* contains the same information as the plaintext, but in a format not readable unless you know the cipher being used and a secret *key*. The key is used as an input to the cipher and controls the operation of the cipher. Without a correct key it is impossible to transform the ciphertext back into the original plaintext.

*Encryption*, or enciphering, is the transformation of a plaintext P into a ciphertext C. The operation is performed by a cipher as  $C = E_K(P)$ , where E is the encryption algorithm of the cipher and K is the provided key.

*Decryption*, or deciphering, of a ciphertext C is the transformation back to readable text by the receiver, by performing  $P = D_K(C) = D_K(E_K(P))$ , where D is the decryption algorithm.

Ciphers can be divided into two main categories, transposition and substitution ciphers. *Substitution ciphers* replace letters or large blocks with substitutes. *Transposition ciphers* rearrange the letters in the plaintext.

Product ciphers are created by composing substitution and transposition ciphers. The cryptographic ciphers defined by the US National Institute of Standard and Technology (NIST) as the Data Encryption Standard (DES) [43] in 1976, as well as its proceeder, the Rijndael cipher [43], selected as the Advanced Encryption Standard (AES) by NIST in 2002, are well known examples of product ciphers used as a base in major communication systems today.

#### 4.2.2 Side-Channel Attacks

Modern ciphers are designed to be immune against known cryptoanalysis methods, and therefore attacks on them are hard to perform. But when cryptography is used in computer systems these ciphers are prone to attack on the physical implementation.

A cipher implemented in an electronic circuit produces timing information, power consumptions variations due to switching activity and radi-

ates electromagnetic energy, which can easily be measured at low costs [5]. Such side channel informations can provide a source of information which can be used to break the cryptographic circuit in order to recover the secret encryption key the device is using.

Side-channel attacks can be categorized by the side-channel information they are exploiting. The first theoretical presentation of a side-channel attack was reported by Kocher in 1996 [24], analyzing the difference in time used by different inputs.

Kocher presented the concept of power analysis attack in 1999 [5]. This type of attack was performed on an actual implementation of a cryptographic circuit by Örs in 2004 [45]. Power analysis attack uses the variation in power consumption correlated to the operations done in calculating the secret key being used.

A side-channel attack may require considerable technical knowledge of the internal operation of the system on which the cryptographic algorithm is implemented.

#### **Timing Attack**

Implementations of cryptographic systems where the execution time of certain operations differs depending on the input values are vulnerable against *timing attacks*. Differences in the execution time are often deliberately implemented in the algorithm by the designer for performance optimization. Kocher showed in [24] that it is possible to find the entire secret key of a vulnerable cryptographic system only by timing measurements.

By careful algorithmic and electronic design, timing attacks can be completely avoided by making the system run in fixed time.

#### Simple Power Analysis Attack

In a *simple power analysis (SPA)* attack, the power consumption of a cryptographic IC is measured directly during cryptographic operations. Using a set of power consumption measurements taken across a cryptographic operation an attacker can directly determine information about a device's operation and the secret key [5].

SPA can be used to break cryptographic implementations in which the execution path depends on the data being processed, exploiting the relationship between the executed operations and the power leakage [45].

#### Differential Power Analysis Attack

While SPA attacks are used to reveal power variations in the execution path due to the instruction sequence, *differential power analysis (DPA)* attacks can

reveal effects correlated to data values being manipulated [5]. This type of attack is also referred to as *correlation power analysis* [46].

A differential power analysis attack is hard to protect against, as it uses statistical and error-correcting methods to extract secret information from a power consumption signal [47].

In a DPA attack, the attacker uses a prediction model of the device being attacked. This model is used for predicting the amount of side-channel output for a certain moment of time in the execution of the cipher. These predictions are correlated to the real side-channel output of the circuit by applying statistical methods. Some common statistical methods used in DPA are the *distance-of-mean* test and the *correlation analysis* [45].

#### **Electromagnetic Radiation Attack**

Electromagnetic radiation is leaked from all electronic devices. A magnetic field is produced when motion occurs in the electronic current flowing in the circuits. An *electromagnetic analysis* (EMA) attack measures the electromagnetic radiation, and the attack can be performed during the same methods as for power attacks [48].

#### **Fault Analysis Attack**

Fault analysis attacks are not directly side-channel attacks. They can be placed under the category of implementation attacks, as they exploit the physical working environment required by the system.

Fault analysis attacks can be divided into two categories. A *differential fault analysis* attack exploits a circuit by changing the operating voltage, tampering with the clock, or applying radiation of various types to the circuit. By measuring the output differences from the output of the circuit at normal operation, a circuit vulnerable to differential fault analysis attacks may reveal secret key information.

A *non-differential fault analysis* attack is based on causing permanent damage to a circuit for the purpose of extracting symmetric keys.

### 4.3 Countermeasures against Side-Channel Attacks

The goal of countermeasures against side-channel attacks are to decrease or preferably completely remove any side channel information leaked by the chip.

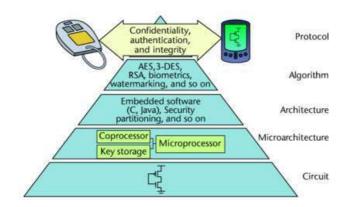

Countermeasures can be done at several layers of the cryptographic system. Beginning on the top-level, protocol and algorithmic countermeasures can be done. At a lower lever, physical electronic countermeasures can reduce the side channel information emitted. Fig. 4.1 illustrates the

Figure 4.1: Security pyramid of an embedded system [49]

different layers. To ensure security in embedded systems, security measures must be addressed in all abstraction layers [49].

### 4.3.1 Algorithmic Countermeasures

Algorithmic countermeasures address the problem of side-channel attacks in the design of a cryptographic algorithm. By taking realistic assumptions about the underlying hardware into account when designing a cryptographic system, side-channel attacks can be made much more difficult to accomplish.

For example, nonlinear key update procedures can be employed to ensure that power traces cannot be correlated between transactions [50]. Aggressive use of exponent and modulus modification processes in public key schemes can also be used to prevent attackers from accumulating data across large numbers of operation [50].

This may solve the problem, but it does require design changes in the algorithms and protocols themselves, which are likely to make the resulting product non-compliant with standards and specifications.

### 4.3.2 Electronic Countermeasures

Electronic countermeasures are taken on the hardware design level. The goal of such countermeasures is to minimize side-channel information leakage by careful design of the logic gates. Such countermeasures are independent of the cryptography algorithm and may be implemented as standard hardware libraries [8].

### **Blinding**

Kocher proposed in [24] a technique for preventing timing attack. By adapting techniques used for blinding digital signatures it is possible to prevent the attacker from knowing the input of the modular exponentiation operation. The correlation between the input data known to the attacker and the time used is removed. This makes it impossible to calculate the secret key by timing attacks, while the cipher still may use performance optimization on modular exponentiation operations.

## Adding noise

Adding noise to a signal helps hiding the secret key, because the statistical evaluation is worse and it is required more measurements if it is noisy. It is important to ensure that added noise does not affects the internal operations of the chip, as it may cause malfunction.

### Reducing signal variation

The ultimate goal of a reduction in the signal variation is to attain a constant power consumption. In [8], Tiri specifies two conditions which must be satisfied to have a constant power consumption:

- a logic gate must have exactly one switching event per signal transition

- the logic gate must charge a constant capacitance in that switching

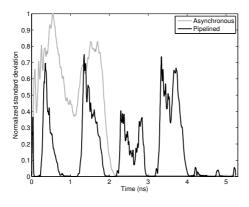

Some differential logic styles have been presented to meet these conditions. For instance, wave dynamic differential logic (WDDL) was presented in [8]. The goal of these countermeasures is to balance the power consumption of the logic gates to be insensitive to switching activity and thus not create any side-channel information.

By reducing the signal amplitude power consumption will also be decreased. An attacker will require more samples to be able to perform a differential power analysis because of more noise. However, an attacker with an infinite number of samples will still be able to perform DPA on the signal [51].

Bouesse *et al.* reduced the power supply voltage to 0.4 V [52]. The reduction in supply voltage with a factor of 3 resulted in a reduction of the energy consumption with a factor of 8.

Operating transistors in the subthreshold region reduces the signal amplitude significantly and decreases the signal-noise ratio. This will be an advantage in a cryptographic system making it harder to get side-channel information. This also has a significant effect on the power analysis.

The dynamic power consumption component is not the significant power consumption part in subthreshold region, but rather the static component, independent of the signal and switching activity.

# **Chapter 5**

# Advanced Encryption Standard Substitution Box Implementation

National Institute of Standard and Technology (NIST) announced in 1997 a competition for a new cryptographic algorithm, as the successor of the aging Data Encryption Standard (DES). In 2000, the Rijndael cipher was announced as the winner of the competition. One year later, NIST announced the new Advanced Encryption Standard (AES) algorithm as approved in Federal Information Processing Standard (FIPS) 197 [53].

The final AES algorithm is almost identical with the Rijndael algorithm, designed by Joan Daemen and Vincent Rijmen [53]. Rijndael supports a larger range of block and key sizes than AES. AES is currently one of the most popular algorithms for symmetric key ciphers [54], and is offering a straight-forward software and hardware implementation.

The best known software implementations of AES achieve about 15 cycles/byte on a modern PC [55]. Hardware implementation can speed up encryption significantly.

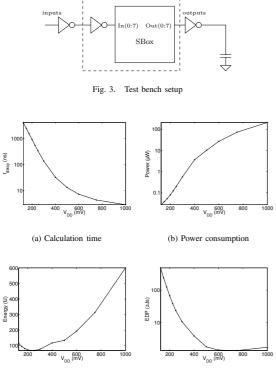

One of the major building block in AES is the SubBytes operation, also called Substitution box (S-box), which substitutes bits in a non-linear operation. The SubByte transformation is used to obscure the relationship between plaintext and ciphertext. In Paper IV, the S-box is implemented in 90 nm CMOS process and simulated in super- and subthreshold operation, exploring the power analysis attack resistance in subthreshold operation.

# 5.1 The Advanced Encryption Standard

AES is a block cipher cryptographic algorithm, operating with a block size and key length which can be chosen independently to be 128, 192

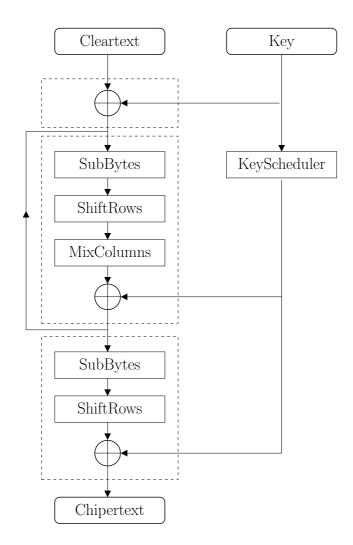

Figure 5.1: AES encryption round structure

or 256 bits. Depending on block and key lengths, a different number of steps, called *rounds*, are performed to encrypt or decrypt data. Each round consists of four operations, called *layers*: *SubBytes*, *ShiftRows*, *MixColumns* and *AddRoundKey*. According to the standard, the basic units of the AES algorithm is an 8-bit *byte*, but these operations can as well be performed on 32-bits words. The round structure of AES is illustrated in Fig. 5.1.

The *input* and *output* of the AES algorithm each consists of *sequences of 128 bits*. These sequences are referred to as blocks. The *Cipher Key* for the AES algorithm is a *sequence of 128, 192 or 256 bits*. Other input, output and Cipher Key lengths are not permitted [56].

AES is designed to be simple, resistant against all known algorithmic attacks, and to offer fast and compact code on many platforms. The major

building blocks of the AES algorithm are the non-linear S-boxes (SubByte-operation) and the MixColumn-operation. A hardware implementation may require up to 20 instances of the S-box, depending on the throughput and clock frequency requirements [57]. The implementation of the S-Boxes mainly determines the efficiency of a hardware implementation in terms of area, throughput and power consumption.

### 5.2 Finite Field Arithmetic

All bytes in the AES algorithm are interpreted as *finite field* elements. The following section introduces the mathematics needed for implementation of the AES S-Box.

A finite field contains a finite set of elements, completely known. Finite field arithmetic differs from standard arithmetic, as all arithmetic operations result in an element within the same field. The operations addition, subtraction, multiplication and division are defined in finite fields [58].

A field K of order  $p^n$  is denoted  $GF(p^n)$  and contains  $p^n$  elements. The letters GF are the abbreviation for *Galois field*, which is another name of finite fields, named after Évariste Galois. The prime p is the *characteristic* of the field K and the positive integer n is called the *dimension* of the field over its prime field GF(p). Each field K of order  $p^n$  must contain the prime field GF(p) [59]. When the characteristic of the field is 2, it is conventional to express elements of the field as binary numbers.

Finite fields are important in coding theory and is a central part of many cryptographic algorithms. The AES algorithm's S-box uses a finite field on the form  $GF(2^8)$ .

### 5.2.1 Polynomial Representation of Finite Fields

It is often advantageous to represent finite fields as polynomials when doing mathematical operations. The elements of the finite field  $K \in GF(2^n)$  can be represented as polynomials of degree strictly less than n with binary coefficients. The resulting polynomials are n-dimensional vectors over the binary field GF(2).

Operations are then performed modulo the *irreducible polynomial* P(x) of degree n. A polynomial is irreducible if and only if its only divisors are one and itself.

For the AES algorithm, the irreducible polynomial is [56]:

$$m(x) = x^8 + x^4 + x^3 + x + 1. (5.1)$$

It is possible to do operations on a reduced order field by mapping an element a from  $GF(2^8)$  to  $GF(((2^2)^2)^2)$  such as the two fields are

| Table 5           | 5.1: Polynomial representation          | on of reduced fields        |

|-------------------|-----------------------------------------|-----------------------------|

| Field             | Bit representation                      | Irreducible polynomial      |

| GF(2)             | $b_0$                                   | n/a                         |

| $GF(2^2)$         | $b_1x+b_0$                              | $P_x(x) = x^2 + x + 1$      |

| $GF((2^2)^2)$     | $b_3xy + b_2y + b_1x + b_0$             | $P_y(y) = y^2 + y + \phi$   |

|                   |                                         | $\phi \in \mathrm{GF}(2^2)$ |

| $GF(((2^2)^2)^2)$ | $b_7xyz + b_6yz + b_5xz + b_4z$         |                             |

|                   | $+b_3xy + b_2y + b_1x + b_0$            | $\lambda \in GF((2^2)^2)$   |

|                   |                                         | _                           |

|                   | $b_0$                                   | GF(2)                       |

|                   | $egin{bmatrix} b_1 & b_0 \end{bmatrix}$ | $GF(2^2) 	 P_x(x)$          |

|                   | $b_3$ $b_2$ $b_1$ $b_0$                 | $GF((2^2)^2) 	 P_y(y)$      |

| $b_7$ $b_6$       | $b_5$ $b_4$ $b_3$ $b_2$ $b_1$ $b_0$     | $GF(((2^2)^2)^2) P_z(z)$    |

| xyz $yz$ :        | xz $z$ $xy$ $y$ $x$ 1                   |                             |

| MCD               | I CD                                    |                             |

Figure 5.2: Binary representation in composite fields

isomorphic using an isomorphism. To reduce the complexity of operations elements in  $GF(2^{2n})$  can be represented as polynomials of first degree with coefficients from  $GF(2^n)$  to reduce the complexity. The field  $GF(2^{2n})$  is generated as an extension field of  $GF(2^n)$  using an irreducible polynomial  $P(x) = x^2 + \alpha x + \beta$ , where  $\alpha, \beta \in GF(2^n)$ ). The field  $GF(2^{2n})$  is then a field extension of degree 2 over  $GF(2^n)$  and can be represented as polynomials of first degree with coefficients from  $GF(2^n)$ , i.e. K = px + q,  $p, q \in GF(2^n)$ . Any higher power of the irreducible polynomial, e.g.  $y^2$ , is reduced according to the primitive polynomial, e.g.  $y^2 = y + \phi$  [60].

General polynomial representations of reduced fields in GF(2),  $GF(2^2)$ ,  $GF((2^2)^2)$  and  $GF(((2^2)^2)^2)$  are listed in Tab. 5.1. Binary representations of polynomials in the fields are illustrated in Fig. 5.2 [60].

# **5.2.2** Arithmetic Operations on Finite Fields $GF(2^n)$

Arithmetic operations on fields with characteristic 2, i.e.  $GF(2^n)$ , are of interest for the S-box implementation and will be discussed in this section. Arithmetic operations needed by the S-box are addition, multiplication and multiplicative inverse. Using polynomial representation, addition and multiplication are relatively trivial operations to implement in hardware.

Calculation of the multiplicative inverse of a number is not a trivial operation and will be described in the next section.

Addition is achieved by adding the coefficient for the corresponding powers in the polynomial vectors in  $GF(2^n)$  for the two elements. The addition can be implemented in hardware with the binary operator exclusive OR (XOR) [58].

Multiplication in  $GF(2^n)$  is defined as polynomial multiplication modulo the irreducible polynomial P(x) of degree n of the field [58]. The multiplication operation can be described mathematically as:

$$p = q \cdot r \operatorname{mod} P(x) \tag{5.2}$$

where p, q, r are polynomials of order  $GF(2^n)$  and P(x) is the irreducible polynomial for the given field.

Unlike addition, there are no simple hardware operations that corresponds to this multiplication. The hardware implementation used for performing this operation is described in Sec. 5.4.2.

# 5.2.3 Multiplicative Inverse

A non-trivial and costly operation in the S-box is calculating the multiplicative inverse over the field  $GF(2^8)$ . The inverse of an element a, i.e.  $a^{-1}$ , is calculated such that  $a \cdot a^{-1} \equiv 1 \mod P(x)$ , where P(x) is the irreducible polynomial [55].

The simplest technique for finding an inverse element for any  $a \in GF(2^n) \neq 0$  is using a table look-up from a pre-generated table. As the table look-up approach is costly to implement in hardware due to large area demands, it is common to use the *extended Euclidean algorithm* and composite field arithmetics to reduce the implementation size [61, 62, 55, 60].

Using the extended Euclidean algorithm, multiplicative inverse in  $GF((2^n)^m)$  can be defined recursively in terms of a sub-field  $GF(2^n)$  and its extension  $GF((2^n)^m)$  [60]. By using polynomial representation of the finite field the problem of calculating the inverse in  $GF(2^8)$  can be translated to calculating the inverse in a smaller field. The multiplicative inverse of an arbitrary polynomial bx + c is given by:

$$(bx+c)^{-1} = b(b^2\beta + bc\alpha + c^2)^{-1}x + (c+b\alpha)(b^2\beta + bc\alpha + c^2)^{-1}$$

(5.3)

when the irreducible polynomial is  $P(x) = x^2 + \alpha x + \beta$  [61].

When Eq. 5.3 is applied recursively down to the base field GF(2), the equation consists of operations which can be performed in the subfield  $GF(2^m)$ . The repeating degree-2 extensions are done using different irreducible polynomials listed in Tab. 5.1 [60]. By using this procedure, the multiplicative inverse operation may be implemented in hardware, as described in Sec. 5.4.2.

Figure 5.3: Multiplicative inverse,  $GF(((2^2)^2)^2)$

# 5.3 Rijndael S-Box

The Rijndael S-box performs the SubBytes operations of the AES algorithm. The main operation of the S-box is to calculate the multiplicative inverse to a given 8-bit number over a finite field  $GF(2^8)$ .

In most AES software implementations, the S-box is pre-generated into a look-up table, offering easy implementation and fast operation. This approach can also be taken when designing a hardware implementation, but such implementations are very area-demanding. By using composite field arithmetic a compact S-box with reduced computation cost may be realized [62]. Regardless of chosen solution, the S-box results in the biggest element in the AES algorithm.

# 5.3.1 S-Box Operation

The S-box function of an input byte *a* consists of the two following two transformations:

**Inverse:** The multiplicative inverse in the finite field  $GF(2^8)$  is calculated,  $b = a^{-1}$ . For the special case a = 0x00, b = 0x00.

**Affine transformation:** The following affine transformation is applied over GF(2):

$$b_i = a_i \oplus a_{(i+4) \bmod 8} \oplus a_{(i+5) \bmod 8} \oplus a_{(i+6) \bmod 8} \oplus a_{(i+7) \bmod 8} \oplus c_i \quad (5.4)$$

for  $0 \le i < 8$  where  $a_i$  is the  $i^{th}$  bit of the byte, and  $c_i$  is the  $i^{th}$  bit of a byte c with the value 01100011. The affine transformation element of

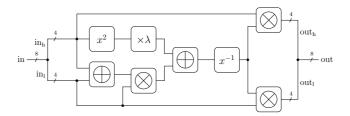

Figure 5.4: Implementation of the compact S-box

the S-box can be expressed in matrix form as:

# 5.4 S-Box Circuit Implementation

Designing a compact S-box is one of the most critical challenges for reducing the total circuit size of the AES hardware [62]. A compact S-box reduces the power consumption significantly by reducing the number of gates. Large reduction in implementation area is obtained by using finite field arithmetic to reduce the fields order  $GF((2^8))$  to  $GF(((2^2)^2)^2)$  [62, 55, 60].

The S-box implementation selected is based on the implementation described by Satoh *et al.* [62], with the size optimization of Mentens *et al.* implemented [55].

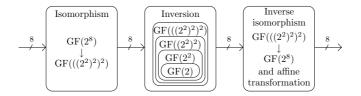

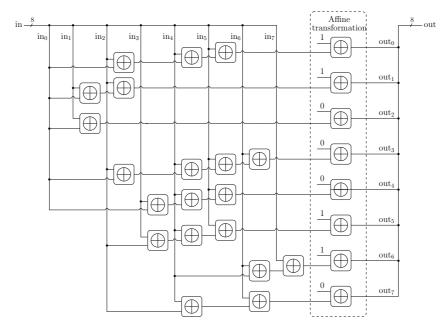

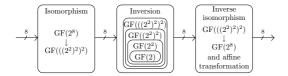

As illustrated in Fig. 5.4, the compact S-box implementation consists of three stages:

- **Stage 1:** Map all elements of the field A to a composite field B, using an isomorphism function  $\delta$ .

- **Stage 2:** Compute the multiplicative inverse over the field *B*.

- **Stage 3:** Map all elements of the field *B* back to *A*, using the isomorphism function  $\delta^{-1}$ .

# 5.4.1 Isomorphism, Inverse Isomorphism and Affine Transformation

The S-box implementation uses the isomorphism suggested by Mentens *et al.* in [55], which results in a small implementation. The isomorphic

mapping used is:

$$\begin{bmatrix} b_0 \\ b_1 \\ b_2 \\ b_3 \\ b_4 \\ b_5 \\ b_6 \\ b_7 \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 1 & 1 \\ 0 & 0 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 1 & 0 & 1 & 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 & 0 & 1 & 0 & 1 \\ 0 & 1 & 1 & 1 & 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} a_0 \\ a_1 \\ a_2 \\ a_3 \\ a_4 \\ a_5 \\ a_6 \\ a_7 \end{bmatrix}$$

where  $a_i, b_i \in GF(2)$  are the coefficients of  $a \in GF(2^8)$ ,  $b \in GF(((2^2)^2)^2)$ . The resulting inverse transformation with affine transformation is:

The corresponding irreducible polynomials are:

$$GF(2^2): P(x) = x^2 + x + 1$$

$GF((2^2)^2): P(y) = y^2 + y + \phi$

$GF(((2^2)^2)^2): P(z) = z^2 + z + \lambda$

where  $\phi = \{10\}_2$  and  $\lambda = \{1100\}_2$ .

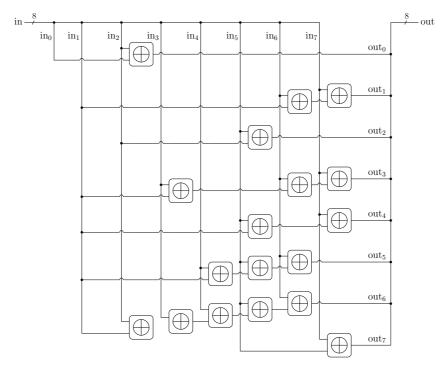

Mappings and affine transformation are implemented by bit-addition using exclusive-OR gates. Schematic drawing of isomorphism from  $GF(2^8)$  to  $GF(((2^2)^2)^2)$  can be found in Sec. A.4.1. Inverse isomorphism and affine transformation are combined. The schematic drawing is shown in Sec. A.4.2.

### 5.4.2 Multiplicative Inverse Computation

By implementing Eq. 5.3 recursively down to GF(2) it is possible to implement the multiplicative inverse operation in hardware.

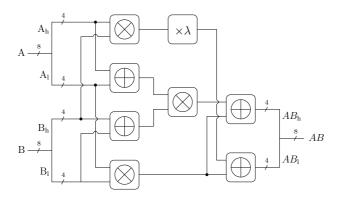

The multiplicative inverse cell is constructed of addition and multiplication cells. Addition in  $GF(2^n)$  is implemented by doing exclusive-OR of corresponding bits of two numbers. Implementation of multiplication is described below.

Figure 5.5: Multiplier  $A \times B$ , GF(2<sup>8</sup>)

### Multiplication