# Benchmarking Persistent Memory with Respect to Performance and Programmability

Svein Gunnar Fagerheim

Thesis submitted for the degree of

Master in Informatikk: Programming and System

Architecture

60 credits

Institutt for informatikk

Faculty of mathematics and natural sciences

UNIVERSITY OF OSLO

Autumn 2021

# Benchmarking Persistent Memory with Respect to Performance and Programmability

Svein Gunnar Fagerheim

@ 2021 Svein Gunnar Fagerheim Benchmarking Persistent Memory with Respect to Performance and Programmability http://www.duo.uio.no/ Printed: Reprosentralen, University of Oslo

#### 1 Abstract

High performance computing is to process data and do calculation on that data at high speed. Traditionally high performance computing uses dynamic random access memory in their computers.

This thesis will explore an alternative form of memory called persistent memory that will occupy half the DIMM slots in the computer. The persistent memory will be tested for its performance and will be compared to traditional memory. The performance will also be tested in competition and cooperation with traditional memory and its performance will be evaluated.

This thesis will also have a look at how to program with persistent memory, are there any programming choices that could be recommended.

# 2 Acknowledgements

I would like to thank my supervisor Xing Cai, his guidance and support are what made it possible for me to complete this thesis. I also would like to thank Tore H. Larsen the Chief Research Engineer HPC at Simula Research Laboratory for fixing all the hardware related issues that came up during this thesis.

I would also like to thank Simula Research Laboratory for allowing me to use their servers in this thesis.

I would also like to thank my parents for their support during this thesis.

# **Contents**

| 1 | Abs | tract                                  | 1  |

|---|-----|----------------------------------------|----|

| 2 | Ack | nowledgements                          | 2  |

| 3 | Int | roduction                              | 5  |

|   | 3.1 | What is persistent memory              | 5  |

|   | 3.2 | Challenges                             | 6  |

|   |     | 3.2.1 Security                         | 6  |

|   |     | 3.2.2 Durability                       | 7  |

|   |     | 3.2.3 Persistent memory leaks          | 7  |

|   | 3.3 |                                        | 8  |

|   |     | 3.3.1 Cost                             | 8  |

|   |     | 3.3.2 Capacity, larger physical memory | 8  |

|   |     | 3.3.3 Byte addressable, low latency    | 8  |

|   | 3.4 | The rest of thesis                     | 8  |

|   | 3.5 | Research questions                     | 9  |

| 4 | Bas | ic programming with NVDIMM             | 10 |

|   | 4.1 | Introduction                           | 10 |

|   | 4.2 | Different types of libraries           | 10 |

|   |     | 4.2.1 Libpmemobj                       | 10 |

|   |     | 4.2.2 libpmemblk and libpmemlog        | 10 |

|   | 4.3 |                                        | 11 |

|   | 4.4 | NVDIMM Functions used in thesis        | 11 |

|   |     | 4.4.1 Open memory pool                 | 11 |

|   |     | 4.4.2 Declaring an array               | 12 |

|   |     | 4.4.3 Allocating array                 | 12 |

|   |     | 4.4.4 Read/Write to array              | 12 |

|   | 4.5 | Coding example                         | 13 |

| 5 | Ber | nchmarks                               | 16 |

|   | 5.1 | Introduction                           | 16 |

|   |     | 5.1.1 Hardware                         | 16 |

|   | 5.2 | STREAM DRAM                            | 17 |

|   | 5.3 | STREAM NVDIMM                          | 19 |

|   | 5.4 | Competition benchmarks                 | 23 |

|   |     | 5.4.1 NVM-NVM                          | 23 |

|   |     | 5.4.2 NVM-DRAM                         | 28 |

|   |     | 5 4 3 DRAM-NVM                         | 33 |

|   |     | 5.4.4   | Observations                   | 38 |

|---|-----|---------|--------------------------------|----|

| 6 | DR  | AM and  | d NVDIMM Cooperation           | 40 |

|   | 6.1 |         | uction                         | 40 |

|   | 6.2 |         | ation of NVDIMM part           | 40 |

|   |     |         | Explanation of formula         | 40 |

|   |     | 6.2.2   | Distribution                   | 42 |

|   |     | 6.2.3   | Prediction                     | 43 |

|   | 6.3 | First p | orogram version                | 43 |

|   | 6.4 | _       | d program version              | 51 |

|   |     |         | Comparisons of versions        | 55 |

| 7 | DR  | AM and  | d NVDIMM working independently | 56 |

|   | 7.1 |         | uction                         | 56 |

|   | 7.2 | Test w  | rith only DRAM                 | 56 |

|   |     | 7.2.1   | Description of code            | 56 |

|   |     | 7.2.2   | Data generation                | 58 |

|   |     | 7.2.3   | Analyzing the data             | 60 |

|   |     | 7.2.4   | Result                         | 60 |

|   | 7.3 | NVM s   | simulation                     | 61 |

|   |     | 7.3.1   | Locks                          | 61 |

|   |     | 7.3.2   | Calculation                    | 62 |

|   |     | 7.3.3   | Analysis                       | 64 |

|   |     | 7.3.4   | Prediction                     | 67 |

|   |     | 7.3.5   | Result                         | 68 |

| 8 | Cor | clusio  | n                              | 70 |

| _ | 8.1 |         | ary                            | 70 |

|   | 8.2 |         | rch questions                  | 71 |

|   |     | 8.2.1   | Question 1                     | 71 |

|   |     | 8.2.2   | Question 2                     | 71 |

|   |     | 8.2.3   | Question 3                     | 71 |

|   |     | 8.2.4   | Question 4                     | 71 |

|   | 8.3 |         | tions                          | 72 |

|   | Q / |         | or worls                       | 79 |

#### 3 Introduction

High performance computing is to process data and do calculation on that data at high speed. The amount of data that is being generated is increasing every year. The data that is being generated in the biggest projects exceeds the capacity of traditional memory. Traditional memory in this context is dynamic random access memory(DRAM). Traditional way this is solved is to make use of the hard drive which is making the processing and calculation of data significant slower.

A possible solution to this problem could be to use NVDIMM. This is a persistent random-access memory[15][16], the difference between DRAM and NVDIMM is that data will not be deleted from NVDIMM when the computer shuts down. It has a faster load/store than a hard drive, but is also slower than traditional DRAM. Since NVDIMM is persistent it can also be used as a storage device the same way as traditional hard drives.

This thesis will explore several things. First is to explore how fast NVDIMM is compared to DRAM when NVDIMM is working alone. The speed of NVDIMM and DRAM will also be measured when they are working simultaneously, they will be made to work simultaneously using the openMP library. The thesis will also explore how the persistent memory performs in experiments that simulate what persistent memory might be used for in the real world. The goal is to come up with a set of advice that may help other people who are using NVDIMM in their projects.

The rest of this chapter will describe what persistent memory is and how it will be used in this thesis. There will also a explanation of the challenges and advantages of persistent memory such as cost, durability and persistent memory leak. There will also be an outline of research questions at the end of the chapter.

## 3.1 What is persistent memory

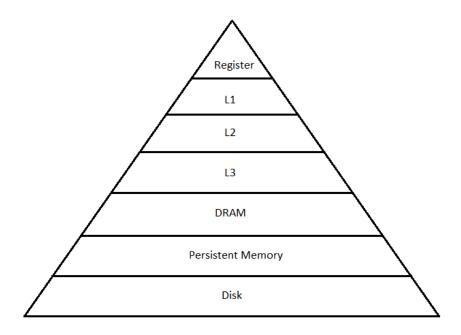

Persistent memory[8] is a non-volatile storage memory[5] that is byte-addressable and has speed close to that of DRAM. Which is a volatile storage system that will lose all its data when the computer is shut down or restarted. Applications and data used by the CPU are temporarily loaded into DRAM from a hard drive in order to reduce latency and increase bandwidth. Persistent memory is another layer between the CPU and the disk. The data the CPU has the most use for is stored in the L1-L3 caches. When the cache is full the data needs to be evicted

the evicted data will be sent back to the memory. If the data usage of the program is so large that it exceeds the memory available on the computer then the computer will start using virtual memory on the disk which is a lot slower then DRAM. The reason virtual memory is so slow is because one must do an I/O block to read and write to disk which takes time. Persistent memory is a layer between the DRAM and the disk in which the CPU can access directly just like it would do a normal DRAM. Figure 1 illustrates where in the hierarchy the persistent memory is placed.

Figure 1: Persistent memory becomes a new level between DRAM and Disk[9]

### 3.2 Challenges

#### 3.2.1 Security

One challenge when it comes to persistent memory is security and privacy[1]. When an encryption key is used to unlock files, the key is stored in the memory. If it is DRAM then the key will disappear when the computer is shut down, but if it is stored in persistent memory it will persist and remain there until it is deleted. It will be very easy for

someone to extract data from persistent memory if the person is able to gain access to it. The same concern also applies to personal information that is being stored in the persistent memory. When developing applications that will use persistent memory and handling sensitive information the programmer needs to remember that data he puts in persistent memory will stay there until it is deleted. It's also worth mentioning that when the data is deleted or deallocated in the memory, the OS makes the space available to another application. The data is only deleted when its overwritten.

#### 3.2.2 Durability

Another challenge for persistent memory is durability. While persistent memory behaves more like DRAM it still has a considerably shorter lifespan than DRAM[1]. This is because persistent memory can only write data to a certain amount of time to a region before the region can no longer hold any data reliably. While the storage capacity of persistent memory has increased, so has the bit error rate increased even more. The solution to this is to either have the hardware mask all the regions with bit error from the software or have the hardware expose them to the software and let the software handle the rest. There is also the possibility of letting the hardware and software work together in order to mask regions with bit errors. This will expand the lifespan of persistent memory, but the challenge for hardware producers is to come up with new technologies that can increase the durability of the persistent memory.

#### 3.2.3 Persistent memory leaks

A common problem one might have when programming in C concerns memory leaks. When the application is using normal DRAM, the memory consumed by the application can be freed just by restarting the application. If the application is using persistent memory on the other hand, then the memory consumed by the application will remain consumed even after the program has been restarted.[14][3] Memory leaks will persist a shutdown just like persistent memory will. The technology must ensure that the memory occupied on the persistent memory can be tracked down to the application that allocated the memory. By doing this it is possible to track down and remove memory leak for the persistent memory.

#### 3.3 Advantages

#### 3.3.1 Cost

One of the biggest shortcomings of DRAM is that it is expensive. When the amount of memory increases in a system the cost of DRAM scales nonlinearly.[1] This has led to memory becoming a bottleneck in servers that run programs where a lot of memory is needed. Persistent memory is more scalable in terms of cost compared to DRAM.

This will enable servers to have more storage capacity that can be read at almost the same speed as DRAM.

#### 3.3.2 Capacity, larger physical memory

The memory capacity of persistent memory represents a drastic increase in the size of memory that is available to the user. Intel has announced a new persistent memory called Intel Optane DC[10]. This is a persistent memory that is compatible with a DDR4 socket and each memory module can contain 512 Gigabytes of memory. The bigger memory size will make it possible to keep more of the data the user is working on in the memory and reduce the traffic between the memory and the hard drive.

#### 3.3.3 Byte addressable, low latency

Since the persistent memory is connected to a DRAM slot it is also byte-addressable. When a program accesses traditional storage it must wait for the OS to do an I/O block in order to get access which takes a long time and read/write are done in 4 kB blocks. With persistent memory the program can skip the I/O block and access the data directly, this will dramatically decrease the latency. Typical latency when using DRAM would be around  $10^{-7}$  seconds[4] while Intel has measured their Optane DC to have a latency of 4.1 ms[2]. Persistent memory is 40 times slower than normal DRAM, but it is still a lot better than SSD that can have 80 ms latency.

#### 3.4 The rest of thesis

In Chapter 4 there will be an explanation of how to program with NVDIMM. There will be an explanation of some of the different types of libraries that exist. How to set up a memory pool that will be used by

the programmer and an explanation of method that will be most used by the programmer.

In chapter 5 will be several benchmarks that will show the performance of DRAM and NVDIMM when whey are working alone and when they are working simultaneously. There will also be made observations about the results from the benchmarks.

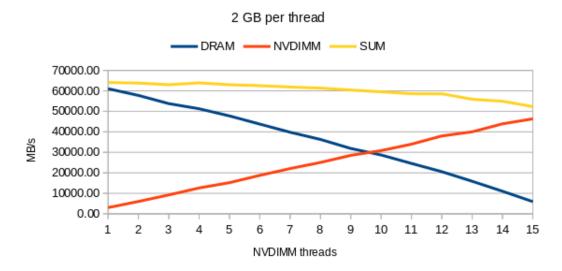

Chapter 6 will be about a scenario that a programmer can encounter. That is when the data exceed the the total capacity of DRAM and the programmer is forced to split the data in two part and place the part that exceeds DRAM on NVDIMM. There will be a formula that calculates how many threads should be reallocated to work on NVDIMM.

Chapter 7 will be about a different scenario. The chapter will test the ability of DRAM and NVDIMM to work with two different tasks. The two groups will synchronize by using a lock/unlock function.

Chapter 8 will contain a summary and a conclusion.

#### 3.5 Research questions

This thesis will try to answer the following research questions.

- What is the data transfer speed of NVDIMM compared to DRAM?

- In an competitive environment, in what way will NVDIMM and DRAM affect each other?

- When the size of the data is higher than the capacity of the DRAM, how much data should be transferred to NVDIMM? How many threads should be allocated to work on the data on NVDIMM?

- While DRAM is working on a task, is it possible for NVDIMM to be working on a different type of task?

# 4 Basic programming with NVDIMM

#### 4.1 Introduction

This chapter will be about how to program with NVDIMM. In order to create code that is using NVDIMM the programmer must choose what library to use and there are many libraries to pick from and all are made for different purposes and have many different types of methods. This chapter exists so others can start on the right track and quickly learn how to use NVDIMM.

The libraries and methods described in this chapter are relevant for NVDIMM devices that support the libraries created by Intel at pmem.io.

#### 4.2 Different types of libraries

#### 4.2.1 Libpmemobj

Libpmemobj[13] allows objects to be stored in persistent memory. The objects in question are not class objects one finds in C++, but instead they are variable-sized blocks of data. The object has an object ID that is independent when it comes to location. The changes or updates to these objects are atomic because the library have transactions to make this happen. This library can be used for multithreading and have been optimized for scaling when it comes to multithreading. The main author also mentions that the C++ version of this library is the cleanest and least prone to error compared to all the other libraries[7]. He therefore recommends that programmers should start using this library if they are new to persistent memory programming.

#### 4.2.2 libpmemblk and libpmemlog

These libraries are made for specific cases. Libpmemblk[11] is used for handling large arrays of persistent memory blocks. The blocks must be larger than 512 bytes in order to work. This library is useful if the program is made to manage a block cache. Libpmemlog[12] is used to append log files. If the program logs a lot of data, it might be better to use libpmemlog in order to avoid going through the traditional file system where most of the time would be spent waiting.

#### 4.3 Creating pmempool

Before NVDIMM can be used, the user must create what is called a memory pool on the NVDIMM. The NVDIMM has several modes, in order to be able to create a memory pool the mode must be set to fsdax. On a server this must be done by the system administrator. To see what mode the NVDIMM is in can be done by the command ndctl-list. A program called pmempool must also be installed on the server, it is this program that will create the memory pool. The command used for creating the memory pool for this thesis is

```

pmempool create --layout Layout_name --size=170G obj

```

The layout is a string stored in the memory pool. When a program accesses a memory pool it needs to send a string that matches the string in the memory pool in order to use it. The user can specify the size of the memory pool, if size is not specified the pmempool will create a pool with the lowest size allowed. There are three different types of memory pool to choose from, they are obj, log and blk. Which type of memory pool to use depends on which type of library is used in the program. In this thesis the libpmemobj library was used and that is why obj was used in the creating of memory pool. Log and blk are for the libraries libpmemlog and libpmemblk. The last part of the command line is the name and file address of the memory pool.

#### 4.4 NVDIMM Functions used in thesis

In this project it is the libpmemobj library that will be used. Below is a short description of all the functions that will be used in the thesis.

#### 4.4.1 Open memory pool

The memory pool uses a pointer called PMEMobjpool. The memory pool is opened by using the method pmemobj\_open that needs two arguments. The first argument is the path to the memory pool created in chapter 4.3. The second argument is a text string that identifies what data belongs to what program.

```

PMEMobjpool *pop = pmemobj_open(path, LAYOUT_NAME);

```

#### 4.4.2 Declaring an array

When the programmer wants to declare an array, the follow command must be used.

```

TOID(Type) Array_name;

```

Type is the data type the programmer wants to use and the name is the name of the array.

#### 4.4.3 Allocating array

When allocating the array the method called POBJ\_ALLOC is used. The method has six arguments. The first argument is the memory pool created in chapter 4.4.1. The second argument is the the array the user wants to allocate memory. Third argument is the data type and the fourth argument is the array length in bytes. The last two arguments are irrelevant in this context and can be given the value NULL.

```

//Allocating of the array

POBJ_ALLOC(Memory_pool, &Array_name, Type, sizeof(double)

* ARRAY_LENGTH, NULL, NULL);

//Deallocating of the array

POBJ_FREE(&Array_name);

```

When the user want to deallocate the array the function POBJ\_FREE must be used. The function is similar to the free function when using malloc. The user only need to the name of the they want to deallocate as argument in POBJ\_FREE.

#### 4.4.4 Read/Write to array

This section will explain the function D\_RO and D\_RW which stands for DIRECT\_RO and DIRECT\_RW and they will read and write directly to the NVDIMM array. Reading from the array is done by using the method D\_RO that must have the array the user wants to read from as argument. The method also uses square brackets after the argument that needs the index of the element in the array the user want to read. The method D\_RW is used when reading to the array. The use of this method is identical to D\_RO.

<sup>1 //</sup>Reading an array variable.

```

var = D_RO(Array_name)[index];

//Writing to an array variable.

D_RW(Array_name)[index] = var;

```

#### 4.5 Coding example

This is an example on how to use the pmemobj library. The example will find the average of an array where the array is replaced with an NVDIMM array. The purpose is to show how easy it is to code with NVDIMM by having all the relevant methods in an easy example. The way of using the a NVDIMM library is a lot similar to using ordinary arrays. Once the programmer has chosen what NVDIMM library to use and included the library in the code the memory pool must be opened. The first thing the code needs is the path to the memory pool and a layout, which is a string that identifies the pool that the user can choose what it will be. This can either be a command line argument the user gives when starting the program or it can be hard coded into the code. This is what has been done in listing 1 at line 5 and 11. These two strings are used as arguments when initiating the pool at line 14-15. The initiation is also followed up with an if-sentence at line 16-19 to check that the memory pool has been successfully created. If it has not the program will print out an error message and exit the program.

Next is to create a NVDIMM array, this is what happens at line 21. The NVDIMM array pointer is a void pointer that is casted to a double pointer. The array gets initiated at line 22. The method used is called POBJ\_ALLOC, this method is similar to malloc for DRAM. The method has six arguments, the first argument is what memory pool the array will be assigned to. The second argument is the address of the pointer. Third argument is the type of the elements in the array. The fourth argument is the length of the array, that is the size of type multiplied with the number of elements in array. The last two arguments are set to NULL.

When writing to an NVDIMM array the programmer must use the method called D\_RW. It only has one argument which is the name of the array. It is followed up with a pair square brackets that contains the index of the element the programmer wants to write to, an example can be found at line 25.

D\_RO is the name of the method one must use to read an element from an NVDIMM array. This method also has one argument which is the name of the array and the square brackets contains the index of the element that will be read. Line 29 is an example of how to add the value of an element in a NVDIMM array to a variable.

In order to deallocate the a NVDIMM array one must use the method POBJ\_FREE and the only argument needed is the address of the NVDIMM pointer, an example can be found in line 34. If the programmer forgets to free up the NVDIMM array there will be a permanent memory leak that will last even after the program have stopped running. In order to get rid of the memory leak one must delete the memory pool and create a new one.

Lastly one must close the memory pool before the program is terminated. This is done with pmemobj\_close, it only has the pointer for the memory pool as argument. Line 35 shows how to close the memory pool.

The functions introduced in this chapter will be used in all the other chapters where I create new benchmarks and tests.

Listing 1: Example of coding with NVDIMM

```

#include <stdio.h>

#include <stdlib.h>

#include <libpmemobj.h>

POBJ_LAYOUT_BEGIN(array);

POBJ_LAYOUT_TOID(array, double);

POBJ_LAYOUT_END (array);

#define ARRAY_LENGTH 1000

#define LAYOUT_NAME "my_layout"

int main(int argc, char *argv[])

11

double average = 0.0;

13

int i;

14

//The path for the memory pool.

15

const char path[] = "/mnt/pmem1-ext4/pool.obj";

16

/* create the pmemobj pool or open it if it already

18

exists */

PMEMobjpool *pop;

19

pop = pmemobj_open(path, LAYOUT_NAME);

20

if (pop == NULL) {

21

perror (path);

exit(1);

```

```

24

//Creation of NVDIMM array.

TOID(double) nvm_array;

POBJ_ALLOC(pop, &nvm_array, double, sizeof(double) *

ARRAY_LENGTH, NULL, NULL);

//Writing to the array.

28

for (i=0; i<ARRAY_LENGTH; i++) {</pre>

29

D_RW(nvm_array)[i] = i;

30

31

//Reading from the NVDIMM array.

32

for (i=0; i<ARRAY_LENGTH; i++) {</pre>

33

average += D_RO(nvm_array)[i];

34

35

average = average / ARRAY_LENGTH;

36

printf("%f\n", average);

37

POBJ_FREE(&nvm_array);

39

pmemobj_close(pop);

40

return 0;

41

```

#### 5 Benchmarks

#### 5.1 Introduction

Persistence memory is slower than DRAM. But there is not much information on how much slower the NVDIMM is in comparison to DRAM. This chapter will test the performance of NVDIMM when it work alone and when it works simultaneously with DRAM. The results will be presented with graphs and tables that will show the difference in performance. The chapter will start off with using the STREAM[6] benchmark in order to find the performance of DRAM. The NVDIMM will also be tested with a STREAM benchmark that have been modified by me for this thesis. Three original benchmarks will also test the NVDIMM when it works simultaneously with DRAM. In the first benchmark DRAM will copy an array from DRAM while NVDIMM copies an array from NVDIMM. In the second benchmark DRAM will copy from DRAM while NVDIMM will copy an array to DRAM. In the last benchmark DRAM will copy from DRAM while NVDIMM will copy an array from DRAM.

#### 5.1.1 Hardware

All the benchmarks has been tested on a server with the following hardware.

Motherboard: Supermicro X11DPU-Z+

CPU: Intel(R) Xeon(R) Gold 6130 CPU @ 2.10GHz, 16 cores

DRAM: Samsung RDIMM, 2666 MT/s.

NVDIMM: Micron Technology NV-DIMM, 2933 MT/s

The server have two CPU, both CPU have twelve memory slots each. Each CPU have six channels. There are one DRAM and one NVDIMM sharing one channel. The compiler used to compile the code is gcc (Ubuntu 7.5.0-3ubuntu1 18.04) 7.5.0. The code have been optimized to level two (-o2).

All of the benchmarks have been tested on socket two. This is to avoid disturbances as much as possible since most of the other processes are running on socket one.

#### 5.2 STREAM DRAM

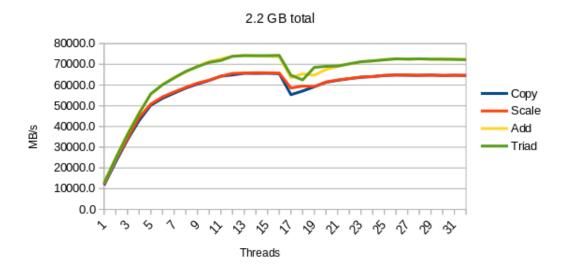

The STREAM[6] benchmark is a synthetic and simple benchmark that is designed to measure bandwidth in MB/s. This benchmark is seen as the standard for measuring memory bandwidth and has not been modified in any way after it was downloaded from the creator websites. The benchmark tests memory bandwidth by running four different tests. The first one test is copy where the elements in one array are copied to another array. The second test is called scale where each element is multiplied with a constant and the result is placed in a second array, the index of the element in the first array and the result in the second array is the same. Third test is add where the elements from two different arrays with the same index are added together and place in a third array where the index is the same as in the two other arrays. Last test is the triad where the one array is multiplied with a constant then added together with a second array and then placed in a third array.

The DRAM Stream benchmark runs the test 32 times and only on one socket, every time it restarts with one extra thread is added. The CPU has 16 cores and when the thread number surpasses that number it starts using the hyper threads on the same core. The Linux program numactl is also used to manage the number of threads and what socket the benchmark is allowed to use.

The result shown in figure 2 and table 1 is what was expected, adding more threads in beginning will give a big increase in transfer speed. But at thread 5 the gains in transfer speed will start to diminish and at thread 11 there will be very little increase in transfer speed when adding more threads. This means that it might be possible to allocate five of the sixteen threads to work on NVDIMM and not loose a significant amount of performance for the eleven remaining threads that are still working on DRAM.

After sixteen threads the benchmark starts to use the hyper-threads. There is a 10,000 MB/s decrease when the benchmark starts to use the hyper-threads. When more and more hyper-threads are added the bandwidth will increase until it is almost at the same level when there were only sixteen threads. 32 threads have 2,000 MB/s lower bandwidth than sixteen threads.

| Threads | Copy    | Scale   | Add     | Triad   |

|---------|---------|---------|---------|---------|

| 1       | 11673.5 | 12180.6 | 12799.4 | 12745.3 |

| 2       | 22995.1 | 23892.4 | 24637.1 | 24807.8 |

| 3       | 33554.9 | 34206.9 | 36248.9 | 36070.7 |

| 4       | 42917.3 | 44315.0 | 46759.0 | 46333.7 |

| 5       | 50260.9 | 50853.1 | 55574.9 | 55784.3 |

| 6       | 53612.5 | 54305.3 | 60174.4 | 60129.4 |

| 7       | 56100.8 | 56671.2 | 63670.6 | 63425.1 |

| 8       | 58554.6 | 58888.6 | 66348.1 | 66607.5 |

| 9       | 60491.7 | 60947.7 | 69059.1 | 68923.9 |

| 10      | 62242.2 | 62368.3 | 71335.2 | 70900.6 |

| 11      | 64257.1 | 64270.1 | 72604.0 | 71854.1 |

| 12      | 64890.3 | 65611.6 | 73973.6 | 73866.7 |

| 13      | 65648.8 | 65805.9 | 74285.3 | 74204.8 |

| 14      | 65606.5 | 65943.6 | 74128.9 | 74158.9 |

| 15      | 65665.5 | 65897.7 | 73918.8 | 74199.9 |

| 16      | 65509.8 | 65770.4 | 73721.2 | 74312.2 |

| 17      | 55365.3 | 58578.1 | 63624.8 | 64728.6 |

| 18      | 57104.2 | 59481.5 | 65404.0 | 62472.2 |

| 19      | 59160.6 | 59279.3 | 64749.4 | 68522.2 |

| 20      | 61328.6 | 61453.3 | 67489.5 | 69020.7 |

| 21      | 62290.7 | 62453.6 | 68987.6 | 69178.2 |

| 22      | 63091.2 | 63146.4 | 70173.6 | 70239.2 |

| 23      | 63737.2 | 63887.6 | 71195.5 | 71235.8 |

| 24      | 64056.6 | 64108.0 | 71629.1 | 71669.4 |

| 25      | 64601.7 | 64685.7 | 72282.9 | 72167.3 |

| 26      | 64824.5 | 64850.8 | 72729.4 | 72623.9 |

| 27      | 64706.3 | 64890.3 | 72444.1 | 72525.6 |

| 28      | 64654.6 | 64743.1 | 72586.7 | 72656.9 |

| 29      | 64827.0 | 64750.6 | 72505.7 | 72481.2 |

| 30      | 64589.2 | 64659.6 | 72453.0 | 72472.8 |

| 31      | 64703.8 | 64714.4 | 72531.8 | 72356.7 |

| 32      | 64610.4 | 64721.9 | 72459.3 | 72212.9 |

Table 1: DRAM Stream,  $2.2~\mathrm{GB}$  total. Speed are in MB/s.

#### DRAM STREAM

Figure 2: DRAM Stream, 2.2 GB total. Graph of table 1.

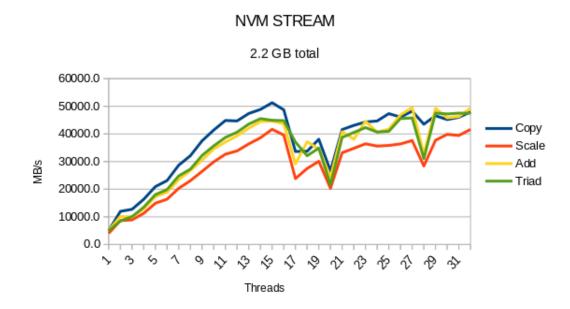

#### 5.3 STREAM NVDIMM

The stream NVDIMM benchmark measures the memory speed of the NVDIMM. This benchmark is the same as the STREAM benchmark has been described in chapter 5.2. The difference is that the memory type has been changed from DRAM to NVDIMM by me. The code shown in listing 2 is part of the original code that has been removed from the code.

Listing 2: Original STREAM benchmark code at line 175-181.

```

#ifndef STREAM_TYPE

#define STREAM_TYPE double

#endif

static STREAM_TYPE a[STREAM_ARRAY_SIZE+OFFSET],

b[STREAM_ARRAY_SIZE+OFFSET],

c[STREAM_ARRAY_SIZE+OFFSET];

```

It has been replaced with the code shown in listing 3. The code starts by opening the memory pool at line 21-27. The code will use a method called initiate at line 28 that will initiate the three arrays. Once this is done the code will continue executing the rest of the STREAM benchmark code just like the original code. The difference is that lines with

read or write to DRAM array has been replaced with the functions D\_RO and D\_RW which read and write to NVDIMM.

Listing 3: Code that has replaced original code.

```

1 PMEMobjpool *pop;

POBJ_LAYOUT_BEGIN(array);

POBJ_LAYOUT_TOID(array, double);

4 POBJ_LAYOUT_END(array);

5 //Declearing the arrays

6 TOID (double) a;

7 TOID (double) b;

TOID(double) c;

void initiate()

10

11

//Initiating the arrays.

12

POBJ_ALLOC (pop, &a, double,

13

(STREAM_ARRAY_SIZE+OFFSET) *sizeof(STREAM_TYPE), NULL,

NULL);

POBJ_ALLOC (pop, &b, double,

(STREAM_ARRAY_SIZE+OFFSET) * sizeof(STREAM_TYPE), NULL,

NULL);

POBJ_ALLOC (pop, &c, double,

15

(STREAM_ARRAY_SIZE+OFFSET) *sizeof(STREAM_TYPE), NULL,

NULL);

16

int main()

19

const char path[] = "/mnt/pmem1-ext4/pool.obj";

20

pop = pmemobj_create(path, LAYOUT_NAME, 10737418240,

21

0666);

if (pop == NULL)

22

pop = pmemobj_open(path, LAYOUT_NAME);

23

if (pop == NULL) {

24

perror (path);

exit(1);

26

27

initiate();

//The rest of the STREAM benchmark after this.

```

The result on the NVDIMM Stream benchmark shown in figure 3

and table 2 is very different from the DRAM Stream benchmark. The DRAM Stream benchmark had a steep increase in bandwidth in the beginning that started to taper off at thread five and almost no increase from thread eleven. The NVDIMM has a more linear increase in bandwidth when the threads are increased from one thread towards sixteen threads. This might be because the speed of one thread is half the bandwidth of one thread in the DRAM Stream benchmark. The max bandwidth reached by the NVDIMM Stream benchmark is 51,273 MB/s and the DRAM Stream benchmark starts to taper off at around 55,000 MB/s. The NVDIMM Stream benchmark never reaches a speed high enough so it can start to taper off and therefore it look more like linear increase in bandwidth.

Thread seventeen and after are the hyper-threads and at thread seventeen there is a 15,000 MB/s decrease before the bandwidth overall start to increase with more hyper-threads added. The bandwidth swings up and down a lot. There is no clear explanation on why the bandwidth fluctuates so much.

Figure 3: NVDIMM Stream, 2.2 GB total. Graph of table 2.

| 1         5036.7         4026.4         5151.3         4956.0           2         11970.2         8616.8         10120.7         8515.8           3         12715.1         8903.4         9972.6         10085.0           4         16349.6         11266.2         12922.7         13474.2           5         20935.0         14924.3         17282.1         18050.7           6         23119.7         16381.2         18887.2         19859.8           7         28694.5         20320.0         23509.8         24824.9           8         32104.6         23082.0         26744.5         27255.4           9         37491.8         26450.3         30517.3         32194.4           10         41394.8         29897.7         34575.6         35671.3           11         44856.8         32659.1         37032.5         38714.6           12         44695.1         33848.9         39292.6         40625.8           13         47377.9         36377.7         42050.6         43542.1           14         48853.3         38589.6         44440.4         45509.7           15         51273.9         41662.3         44663.6 <th< th=""><th>Threads</th><th>Copy</th><th>Scale</th><th>Add</th><th>Triad</th></th<> | Threads | Copy    | Scale   | Add     | Triad   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|

| 2       11970.2       8616.8       10120.7       8515.8         3       12715.1       8903.4       9972.6       10085.0         4       16349.6       11266.2       12922.7       13474.2         5       20935.0       14924.3       17282.1       18050.7         6       23119.7       16381.2       18887.2       19859.8         7       28694.5       20320.0       23509.8       24824.9         8       32104.6       23082.0       26744.5       27255.4         9       37491.8       26450.3       30517.3       32194.4         10       41394.8       29897.7       34575.6       35671.3         11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024                                                                                                                                                      |         |         |         |         |         |

| 3         12715.1         8903.4         9972.6         10085.0           4         16349.6         11266.2         12922.7         13474.2           5         20935.0         14924.3         17282.1         18050.7           6         23119.7         16381.2         18887.2         19859.8           7         28694.5         20320.0         23509.8         24824.9           8         32104.6         23082.0         26744.5         27255.4           9         37491.8         26450.3         30517.3         32194.4           10         41394.8         29897.7         34575.6         35671.3           11         44856.8         32659.1         37032.5         38714.6           12         44695.1         33848.9         39292.6         40625.8           13         47377.9         36377.7         42050.6         43542.1           14         48853.3         38589.6         44440.4         45509.7           15         51273.9         41662.3         44663.6         44941.4           16         48704.8         39592.3         43615.7         44797.8           17         33638.9         23842.9         29161.2                                                                                |         |         |         |         |         |

| 4       16349.6       11266.2       12922.7       13474.2         5       20935.0       14924.3       17282.1       18050.7         6       23119.7       16381.2       18887.2       19859.8         7       28694.5       20320.0       23509.8       24824.9         8       32104.6       23082.0       26744.5       27255.4         9       37491.8       26450.3       30517.3       32194.4         10       41394.8       29897.7       34575.6       35671.3         11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9 <td< td=""><td></td><td></td><td></td><td></td><td></td></td<>                                                                                             |         |         |         |         |         |

| 5         20935.0         14924.3         17282.1         18050.7           6         23119.7         16381.2         18887.2         19859.8           7         28694.5         20320.0         23509.8         24824.9           8         32104.6         23082.0         26744.5         27255.4           9         37491.8         26450.3         30517.3         32194.4           10         41394.8         29897.7         34575.6         35671.3           11         44856.8         32659.1         37032.5         38714.6           12         44695.1         33848.9         39292.6         40625.8           13         47377.9         36377.7         42050.6         43542.1           14         48853.3         38589.6         44440.4         45509.7           15         51273.9         41662.3         44663.6         44941.4           16         48704.8         39592.3         43615.7         44797.8           17         33638.9         23842.9         29161.2         37024.5           18         33712.5         27466.9         37166.7         32095.5           19         38073.6         30095.0         34539.9                                                                            |         |         |         |         |         |

| 6       23119.7       16381.2       18887.2       19859.8         7       28694.5       20320.0       23509.8       24824.9         8       32104.6       23082.0       26744.5       27255.4         9       37491.8       26450.3       30517.3       32194.4         10       41394.8       29897.7       34575.6       35671.3         11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       <                                                                                                                                                  |         |         |         |         |         |

| 7       28694.5       20320.0       23509.8       24824.9         8       32104.6       23082.0       26744.5       27255.4         9       37491.8       26450.3       30517.3       32194.4         10       41394.8       29897.7       34575.6       35671.3         11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6                                                                                                                                                         |         |         |         |         |         |

| 8       32104.6       23082.0       26744.5       27255.4         9       37491.8       26450.3       30517.3       32194.4         10       41394.8       29897.7       34575.6       35671.3         11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9                                                                                                                                                        |         |         |         |         |         |

| 9       37491.8       26450.3       30517.3       32194.4         10       41394.8       29897.7       34575.6       35671.3         11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3                                                                                                                                                       |         |         |         |         |         |

| 10       41394.8       29897.7       34575.6       35671.3         11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8                                                                                                                                                      |         |         |         |         |         |

| 11       44856.8       32659.1       37032.5       38714.6         12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2                                                                                                                                                      |         |         |         |         |         |

| 12       44695.1       33848.9       39292.6       40625.8         13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8                                                                                                                                                      |         |         |         |         |         |

| 13       47377.9       36377.7       42050.6       43542.1         14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8       45762.3         28       43507.7       28391.9       32673.6                                                                                                                                                      |         |         |         |         |         |

| 14       48853.3       38589.6       44440.4       45509.7         15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8       45762.3         28       43507.7       28391.9       32673.6       31051.1         29       46562.0       37710.1       49211.6                                                                                                                                                      |         |         |         |         |         |

| 15       51273.9       41662.3       44663.6       44941.4         16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8       45762.3         28       43507.7       28391.9       32673.6       31051.1         29       46562.0       37710.1       49211.6       47533.4         30       45188.7       39833.6       45820.8                                                                                                                                                      |         |         |         |         |         |

| 16       48704.8       39592.3       43615.7       44797.8         17       33638.9       23842.9       29161.2       37024.5         18       33712.5       27466.9       37166.7       32095.5         19       38073.6       30095.0       34539.9       34835.6         20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8       45762.3         28       43507.7       28391.9       32673.6       31051.1         29       46562.0       37710.1       49211.6       47533.4         30       45188.7       39833.6       45820.8       47210.6         31       46011.6       39429.2       46247.3                                                                                                                                                      |         |         |         |         |         |

| 17     33638.9     23842.9     29161.2     37024.5       18     33712.5     27466.9     37166.7     32095.5       19     38073.6     30095.0     34539.9     34835.6       20     26627.1     20307.7     24445.4     21617.2       21     41575.9     33180.5     40777.5     38727.8       22     43078.1     34787.1     38100.6     40516.5       23     44306.5     36409.9     44583.9     42289.1       24     44679.1     35595.9     40602.3     40671.9       25     47327.4     35824.6     41718.8     40939.5       26     46085.6     36378.7     46893.2     45583.9       27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                               |         |         |         |         |         |

| 18     33712.5     27466.9     37166.7     32095.5       19     38073.6     30095.0     34539.9     34835.6       20     26627.1     20307.7     24445.4     21617.2       21     41575.9     33180.5     40777.5     38727.8       22     43078.1     34787.1     38100.6     40516.5       23     44306.5     36409.9     44583.9     42289.1       24     44679.1     35595.9     40602.3     40671.9       25     47327.4     35824.6     41718.8     40939.5       26     46085.6     36378.7     46893.2     45583.9       27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                        |         | 48704.8 | 39592.3 |         |         |

| 19     38073.6     30095.0     34539.9     34835.6       20     26627.1     20307.7     24445.4     21617.2       21     41575.9     33180.5     40777.5     38727.8       22     43078.1     34787.1     38100.6     40516.5       23     44306.5     36409.9     44583.9     42289.1       24     44679.1     35595.9     40602.3     40671.9       25     47327.4     35824.6     41718.8     40939.5       26     46085.6     36378.7     46893.2     45583.9       27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17      | 33638.9 | 23842.9 | 29161.2 | 37024.5 |

| 20       26627.1       20307.7       24445.4       21617.2         21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8       45762.3         28       43507.7       28391.9       32673.6       31051.1         29       46562.0       37710.1       49211.6       47533.4         30       45188.7       39833.6       45820.8       47210.6         31       46011.6       39429.2       46247.3       47491.9                                                                                                                                                                                                                                                                                                                                                                                                                    | 18      | 33712.5 | 27466.9 | 37166.7 | 32095.5 |

| 21       41575.9       33180.5       40777.5       38727.8         22       43078.1       34787.1       38100.6       40516.5         23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8       45762.3         28       43507.7       28391.9       32673.6       31051.1         29       46562.0       37710.1       49211.6       47533.4         30       45188.7       39833.6       45820.8       47210.6         31       46011.6       39429.2       46247.3       47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19      | 38073.6 | 30095.0 | 34539.9 | 34835.6 |

| 22     43078.1     34787.1     38100.6     40516.5       23     44306.5     36409.9     44583.9     42289.1       24     44679.1     35595.9     40602.3     40671.9       25     47327.4     35824.6     41718.8     40939.5       26     46085.6     36378.7     46893.2     45583.9       27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20      | 26627.1 | 20307.7 | 24445.4 | 21617.2 |

| 23       44306.5       36409.9       44583.9       42289.1         24       44679.1       35595.9       40602.3       40671.9         25       47327.4       35824.6       41718.8       40939.5         26       46085.6       36378.7       46893.2       45583.9         27       48237.8       37579.8       49538.8       45762.3         28       43507.7       28391.9       32673.6       31051.1         29       46562.0       37710.1       49211.6       47533.4         30       45188.7       39833.6       45820.8       47210.6         31       46011.6       39429.2       46247.3       47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21      | 41575.9 | 33180.5 | 40777.5 | 38727.8 |

| 24     44679.1     35595.9     40602.3     40671.9       25     47327.4     35824.6     41718.8     40939.5       26     46085.6     36378.7     46893.2     45583.9       27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22      | 43078.1 | 34787.1 | 38100.6 | 40516.5 |

| 25     47327.4     35824.6     41718.8     40939.5       26     46085.6     36378.7     46893.2     45583.9       27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23      | 44306.5 | 36409.9 | 44583.9 | 42289.1 |

| 26     46085.6     36378.7     46893.2     45583.9       27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24      | 44679.1 | 35595.9 | 40602.3 | 40671.9 |

| 27     48237.8     37579.8     49538.8     45762.3       28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25      | 47327.4 | 35824.6 | 41718.8 | 40939.5 |

| 28     43507.7     28391.9     32673.6     31051.1       29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26      | 46085.6 | 36378.7 | 46893.2 | 45583.9 |

| 29     46562.0     37710.1     49211.6     47533.4       30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27      | 48237.8 | 37579.8 | 49538.8 | 45762.3 |

| 30     45188.7     39833.6     45820.8     47210.6       31     46011.6     39429.2     46247.3     47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28      | 43507.7 | 28391.9 | 32673.6 | 31051.1 |

| 31 46011.6 39429.2 46247.3 47491.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29      | 46562.0 | 37710.1 | 49211.6 | 47533.4 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30      | 45188.7 | 39833.6 | 45820.8 | 47210.6 |

| 32 47961.6 41638.6 49278.3 47481.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31      | 46011.6 | 39429.2 | 46247.3 | 47491.9 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32      | 47961.6 | 41638.6 | 49278.3 | 47481.3 |

Table 2: NVDIMM Stream,  $2.2~\mathrm{GB}$  total. Speeds are in MB/s

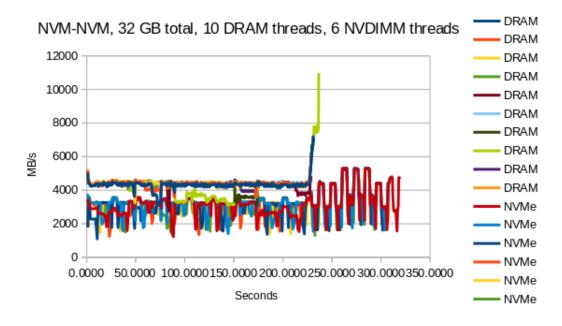

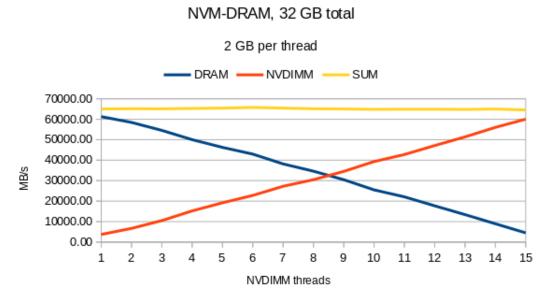

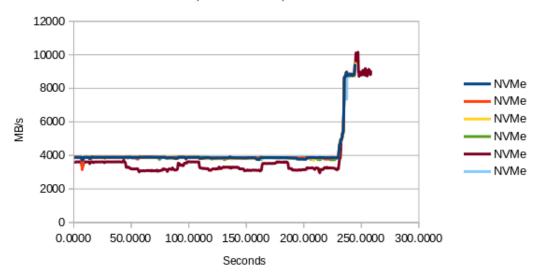

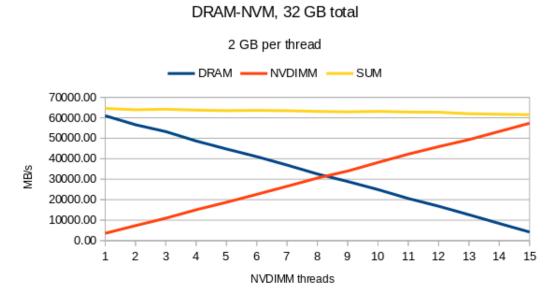

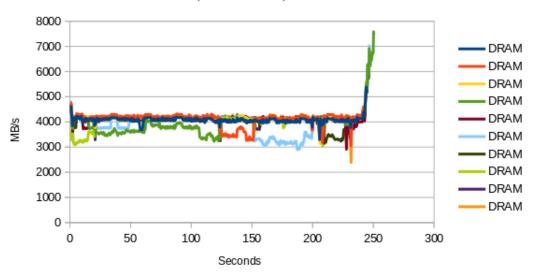

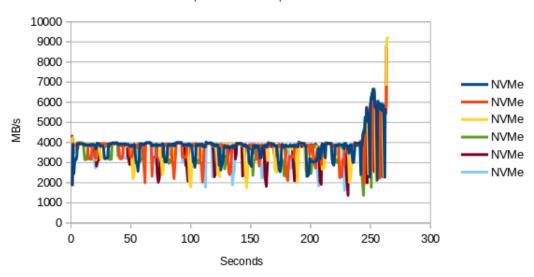

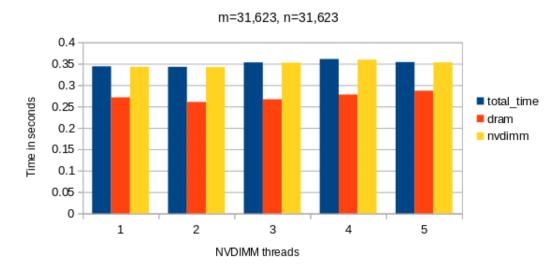

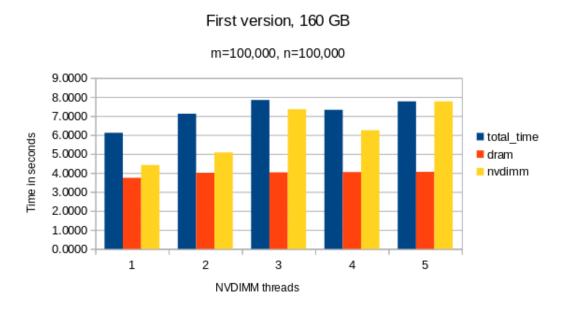

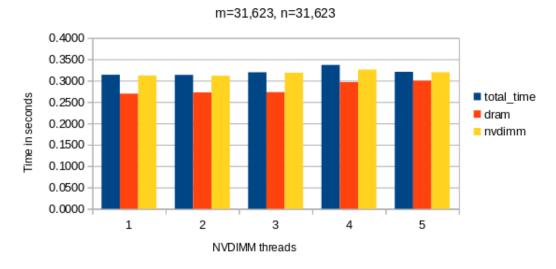

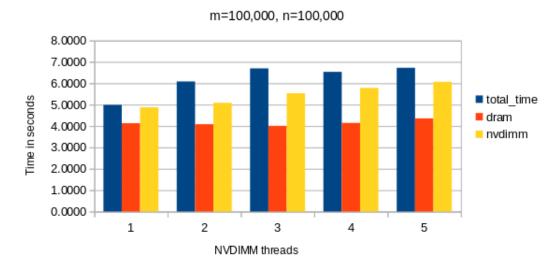

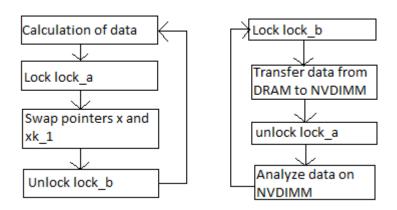

#### 5.4 Competition benchmarks