# Topology Agnostic Methods for Routing, Reconfiguration and Virtualization of Interconnection Networks

Åshild Grønstad Solheim

February 14, 2012

# Acknowledgements

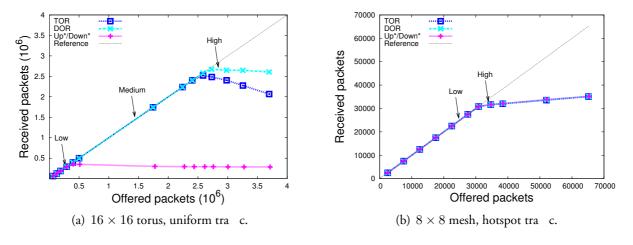

A number of people have supported me during the work with this PhD thesis. First and foremost, the advice, constructive criticism and encouragement provided by my supervisors, Olav Lysne and Tor Skeie, have been invaluable. I am deeply grateful for their willingness to share knowledge and ideas; for their friendliness and patience; and for their open door policy. I would also like to thank Ingebjørg Theiss – my third supervisor for the first 18 months at Simula Research Laboratory – for giving me a thorough introduction to the research area of interconnection networks.

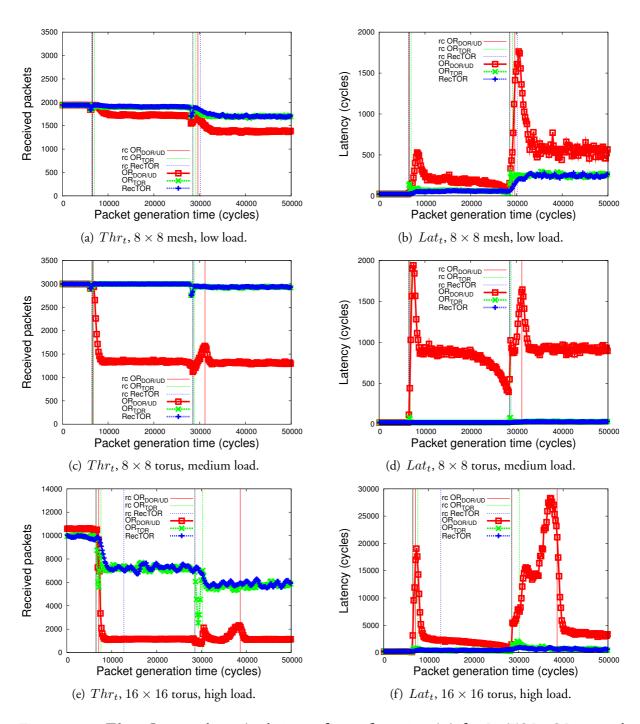

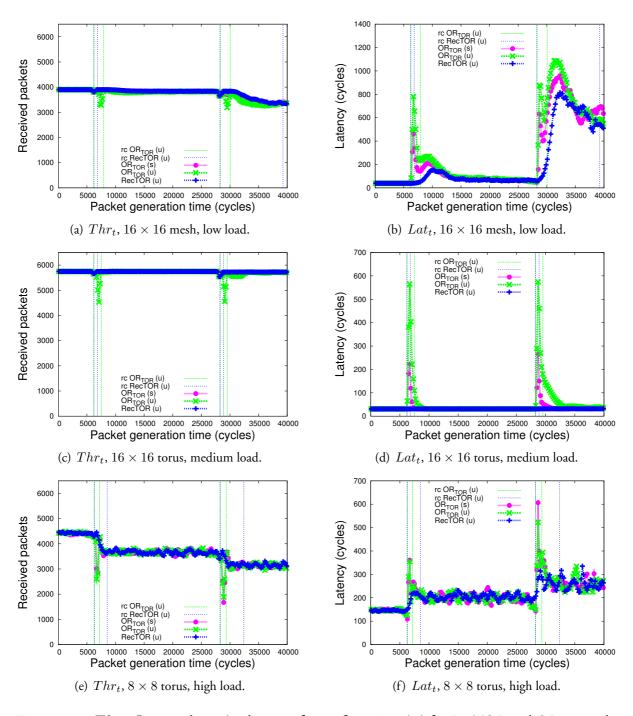

My colleagues and friends at Simula Research Laboratory are an exceptionally likeable, interesting and knowledgeable group of people from various parts of the world, and a list of those of my colleagues who mean a great deal to me would have contained too many names to be included here. I will, however, mention two of my colleagues in particular. Their contributions have significantly improved the quality of the research papers upon which this thesis is based, as well as the quality of the thesis itself. Thomas Sødring has been a close collaboration partner, inspiring colleague and supportive friend. I thank him for useful discussions over numerous cups of tea; for being prepared to share his constant stream of ideas; for co-authoring research papers; and for developing main parts of our simulator models. (In addition, on behalf of my entire family and myself, I am grateful for having obtained the recipe for Thomas's delicious pink cheesecake.) Sven-Arne Reinemo has always been willing to answer my questions, provide useful comments and give helpful advice, and he is also a co-author of two of the research papers upon which this thesis is based. I would also like to thank the remaining co-authors for their contributions, and the members of the IT support team for always being friendly and ready to help.

This thesis could not have been written without the funding from Simula Research Laboratory. My husband and best friend, Pål Grønstad Solheim, noticed the advertisement for a vacant PhD position at Simula Research Laboratory, encouraged me to apply, and has since been most enthusiastic and supportive. As always, my parents, Anne Synnøve and Jens Jørgen Grønstad, have been very important supporters. Fortunately, my family and friends have shown understanding for the necessity of working long hours while pursuing a PhD.

# **Contents**

| 1 | Intr | duction                                         | 1    |

|---|------|-------------------------------------------------|------|

|   | 1.1  | Contributions                                   | . 3  |

|   |      | 1.1.1 Routing                                   | . 3  |

|   |      | 1.1.2 Reconfiguration                           | . 3  |

|   |      | 1.1.3 Processor allocation (virtualization)     | . 4  |

|   | 1.2  | Thesis organization                             | . 4  |

|   | 1.3  | Publications                                    | . 4  |

| 2 | Inte | connection networks                             | 7    |

|   | 2.1  | Topology                                        | . 9  |

|   | 2.2  | Flow control and switching                      | . 13 |

|   |      | 2.2.1 Switching mechanisms                      | . 14 |

|   |      | 2.2.2 Flow control mechanisms                   | . 14 |

|   | 2.3  | Channel dependency and deadlock                 | . 15 |

|   | 2.4  | Fault models                                    |      |

|   | 2.5  | Routing                                         | . 19 |

|   |      | 2.5.1 Selected algorithms for meshes and tori   | . 23 |

|   | 2.6  | Reconfiguration                                 | . 23 |

|   | 2.7  | Processor allocation and virtualization         | . 25 |

|   |      | 2.7.1 Selected strategies for meshes and tori   | . 29 |

|   | 2.8  | Topology agnostic methods                       | . 32 |

|   |      | 2.8.1 Selected routing algorithms               | . 34 |

|   |      | 2.8.2 Selected reconfiguration methods          |      |

|   |      | 2.8.3 Selected processor allocation strategies  | . 38 |

| 3 | Rese | arch methods                                    | 41   |

|   | 3.1  | The simulator models                            | . 42 |

|   |      | 3.1.1 The communication simulator               | . 42 |

|   |      | 3.1.2 The allocation simulator                  | . 44 |

|   |      | 3.1.3 Validation and verification of the models | . 45 |

| 4 | Rou  | ing                                             | 49   |

|   | 4.1  | Requirements to a routing algorithm for ASI     | . 50 |

|   |      | 4.1.1 No assumptions on topology                |      |

|   |      | 4.1.2 Deadlock-freedom                          | 50   |

|   |      | 4.1.3 Shortest path routing                                      | 51 |

|---|------|------------------------------------------------------------------|----|

|   |      | 4.1.4 No transitions from one virtual layer to another           | 51 |

|   |      | 4.1.5 High e ciency for regular topologies                       | 52 |

|   | 4.2  | Realization of LASH in ASI                                       | 52 |

|   |      | 4.2.1 Complexity                                                 | 54 |

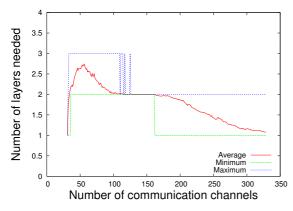

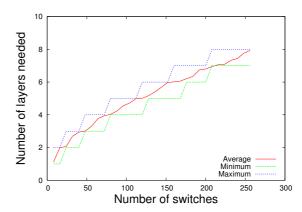

|   |      | 4.2.2 Need for virtual layers                                    | 54 |

|   |      | 4.2.3 Deadlock-freedom and quality of service                    | 55 |

|   |      | 4.2.4 Static fault tolerance                                     | 56 |

|   |      | 4.2.5 Route optimization for mesh                                | 56 |

|   | 4.3  | Relevance for InfiniBand                                         | 57 |

|   |      | 4.3.1 Guidelines for selecting a routing algorithm               | 57 |

|   |      |                                                                  | 58 |

|   | 4.4  | Experiment setup                                                 | 59 |

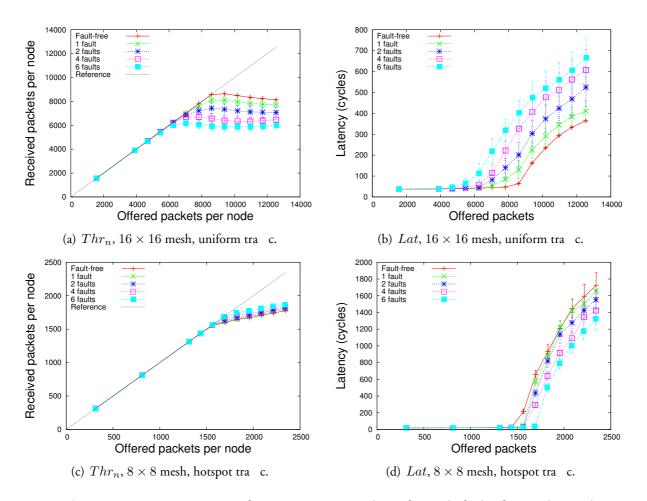

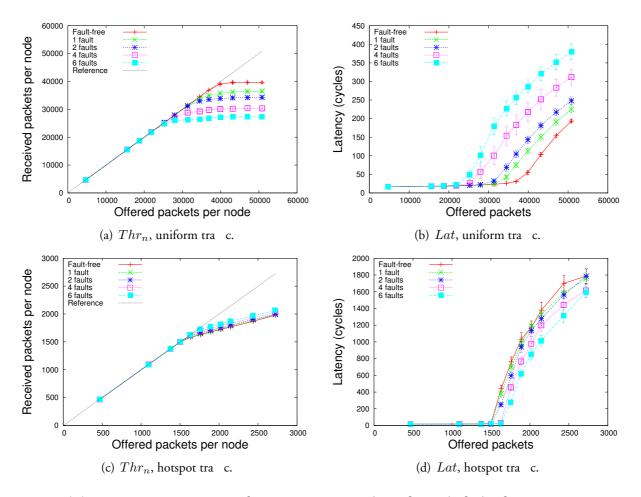

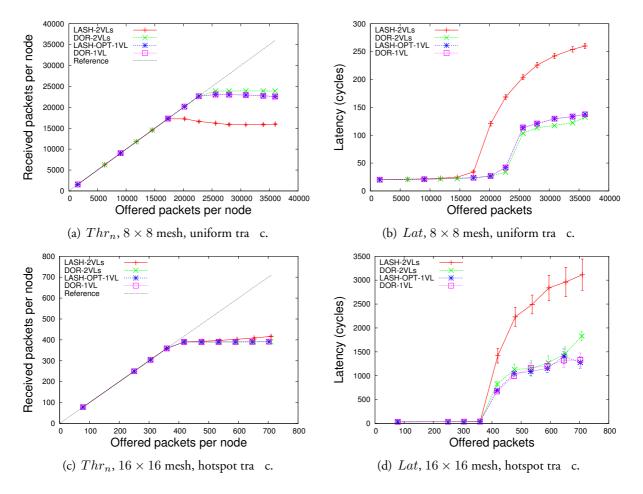

|   | 4.5  | Results                                                          | 51 |

|   |      |                                                                  | 61 |

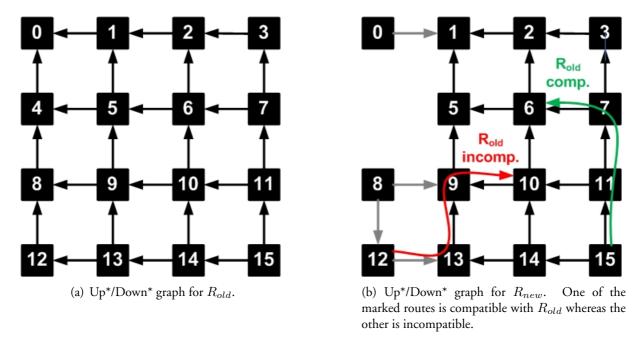

|   |      | 4.5.2 Route optimization                                         | 63 |

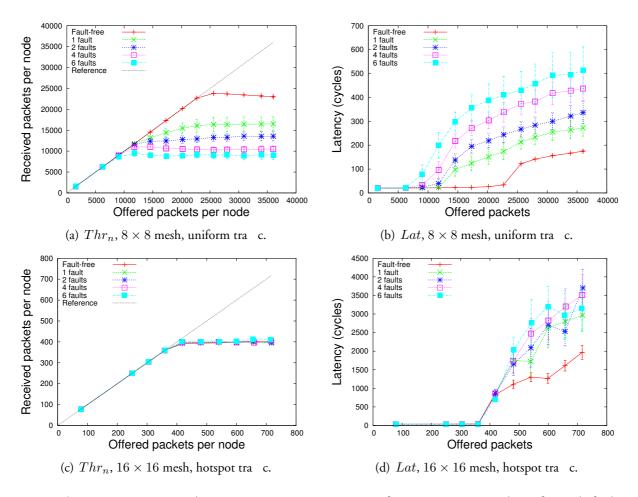

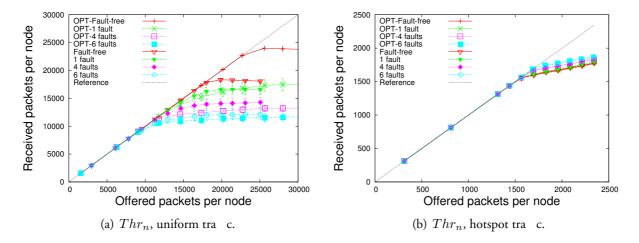

|   |      | 4.5.3 Static fault tolerance when using route optimization       | 65 |

|   | 4.6  |                                                                  | 66 |

|   | 4.7  | Critique                                                         | 59 |

|   | 4.8  | Future work                                                      | 70 |

| 5 | Reco | onfiguration 7                                                   | 71 |

| _ | 5.1  | OR for source routing environments                               |    |

|   | J    | 5.1.1 The original OR algorithm                                  |    |

|   |      | 5.1.2 Adaptations for use in source routing systems              |    |

|   |      | 5.1.3 A performance optimization                                 |    |

|   |      | •                                                                | 31 |

|   |      | ,                                                                | 33 |

|   |      | 1                                                                | 35 |

|   | 5.2  |                                                                  | )2 |

|   |      |                                                                  | )4 |

|   |      |                                                                  | 96 |

|   |      | •                                                                | 9  |

|   | 5.3  | Related work and our contribution                                | )3 |

|   | 5.4  | Critique                                                         |    |

|   | 5.5  | Future work                                                      | )7 |

| 6 | Proc | essor allocation 10                                              | 19 |

| - | 6.1  | Tra c-contained allocation in an Up*/Down* routed system         |    |

|   | ~    | 6.1.1 The UDFlex algorithm                                       |    |

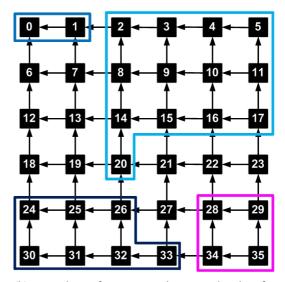

|   |      | 6.1.2 An example implementation                                  |    |

|   |      | 6.1.3 Experiment setup                                           |    |

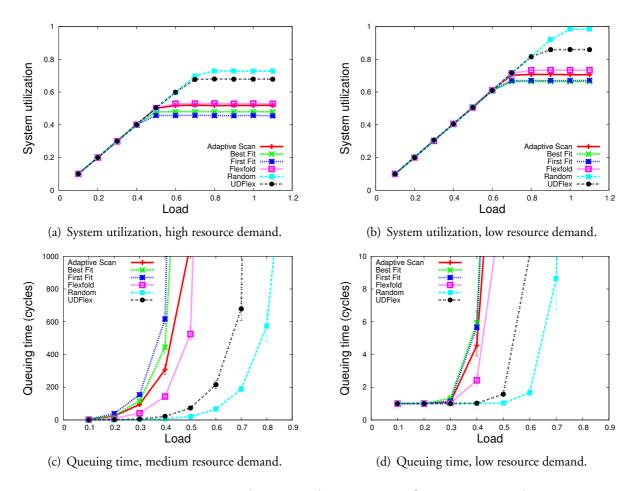

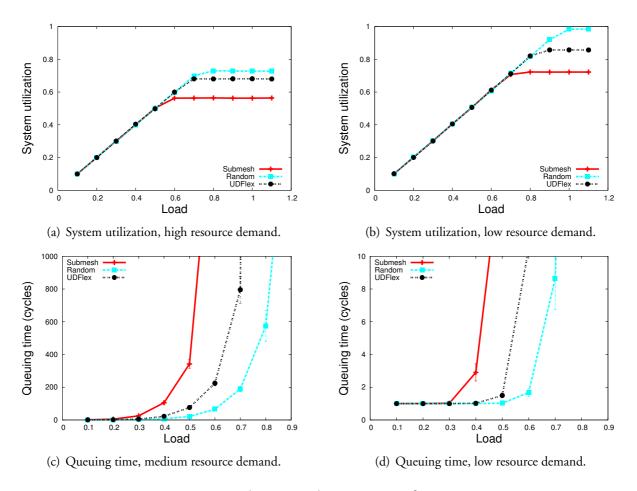

|   |      | 6.1.4 Results                                                    |    |

|   | 6.2  | A framework for developing trace-contained allocation strategies |    |

|    |        | 6.2.1 The framework                   | 123 |

|----|--------|---------------------------------------|-----|

|    |        | 6.2.2 An example configuration        | 127 |

|    |        | 6.2.3 Experiment setup                | 128 |

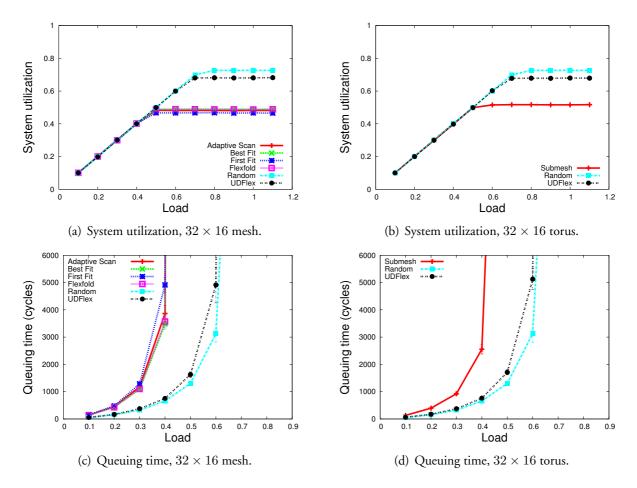

|    |        | 6.2.4 Results                         | 131 |

|    |        | 6.2.5 An alternative approach         | 138 |

|    | 6.3    | Related work and our contribution     | 140 |

|    | 6.4    | Critique                              | 145 |

|    | 6.5    | Future work                           | 148 |

| 7  | Con    | clusion                               | 151 |

|    | 7.1    | Routing                               | 151 |

|    | 7.2    | Reconfiguration                       | 152 |

|    | 7.3    | Processor allocation (virtualization) | 153 |

|    | 7.4    | Future work                           | 154 |

| Bi | bliogr | raphy                                 | 157 |

# Chapter 1

# Introduction

Modern computing systems, such as supercomputers, data centers and multicore processor integrated circuit chips, generally require e cient communication between their di erent system units; tolerance towards component faults; flexibility to expand or merge; and a high utilization of their resources. Interconnection networks are used in a variety of such computing systems in order to enable communication between their diverse system units. Supercomputers, such as those ranked by the Top500 list [237], typically host traditional high performance computing applications, examples of which include simulations of medical, meteorological and geological processes. Important tasks for an interconnection network of a supercomputer include the provisioning of low latency and high throughput communication between a set of computing nodes that cooperate in executing a parallel application. Data centers, such as those operated by Google [85] and Amazon [9], are often large facilities which include huge collections of computing and storage resources. Such systems face a number of challenges, some of which are related to reliability, resource utilization and energy-e ciency. This set of challenges is also highly relevant for a multicore (also known as manycore) processor environment, where an interconnection network embedded in the integrated circuit chip links cores to each other as well as to other units such as cache memory. (An example of a multicore chip is Intel's [106] terascale prototype processor [100, 244] which has 80 cores.) In general, the various units of a computing system can be connected in a number of ways, and interconnection networks can thus assume many di erent structures (topologies).

Most traditional routing algorithms are relatively simple mechanisms designed for a specific regular network structure. A main topic of this thesis is topology agnostic routing, which does not assume a particular network structure. Topology agnostic routing algorithms were initially motivated by interconnection network technologies – such as Autonet [204] and Myrinet [31] – that allowed the units of a computing system to be connected in an arbitrary (irregular) manner. When compared to routing algorithms tailored to specific topologies, early topology agnostic routing algorithms (such as the one proposed in [204]) typically achieved an inferior performance. More recent topology agnostic routing algorithms perform significantly better than their predecessors, however.

Topology agnostic routing algorithms are essential for the operation of systems that include interconnection networks with irregular topologies. Furthermore, such algorithms play an important part in the provisioning of fault tolerance in systems that include interconnection networks with regular topologies. As no particular network structure is assumed, topology agnostic routing algorithms are also usable for the non-regular topologies that may result from faults in originally regular topologies.

For a single network component (such as a switch or communication channel) the expected time between failures may be relatively long. Nevertheless, the risk of a faulty network component increases when computing systems grow larger. A faulty network component could be present at the start-up of a computing system, or occur while the system is in operation. The former situation requires static fault handling, whereas the latter situation requires dynamic fault handling and is in general more challenging. An attractive quality of topology agnostic routing algorithms is their inherent static fault tolerance. Unplanned topology changes, such as network component faults, are not the only type of topology change that may occur over the lifetime of a computing system. Topology agnostic routing algorithms also provide flexibility with respect to planned topology changes, such as extensions of existing interconnection networks or mergers of computing systems with di erent interconnection network solutions.

Unplanned or planned changes in the topology of an interconnection network could disrupt communication between the various units of a computing system. A new routing function is needed if – as a result of a topology change – an existing routing function can no longer provide connectivity between the communicating system units. The change-over from one routing function to another is referred to as reconfiguration, and is a main topic of this thesis. An e-cient reconfiguration strategy is important for the maintenance of a predictable network service after the occurrence of a topology change.

Due to strict requirements on high system throughput and low packet latency, interconnection networks in modern communication systems must in general support lossless communication. Thus, in order to avoid packet loss due to a lack of bu er space, flow control is exercised over each communication channel. Such a flow control mechanism entails a risk of packet deadlock. (In a deadlocked set of packets none of the packets can advance until another packet in the set advances.) A deadlock generally has a devastating e ect on the performance of a computing system. Deadlock recovery methods, such as [13, 116], aim to resolve an established deadlock. Unfortunately, for many applications deadlock recovery methods may cause a system to stall for an unacceptably long period of time. Thus, a deadlock must in general be avoided. The requirement of deadlock avoidance is a major challenge in the design of routing and reconfiguration algorithms for interconnection networks. On the purpose to avoid deadlock, routing and reconfiguration algorithms typically enforce restrictions on packet transmission, and some of these restrictions may significantly reduce the performance of a computing system.

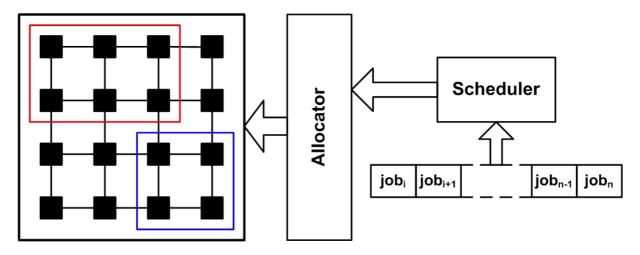

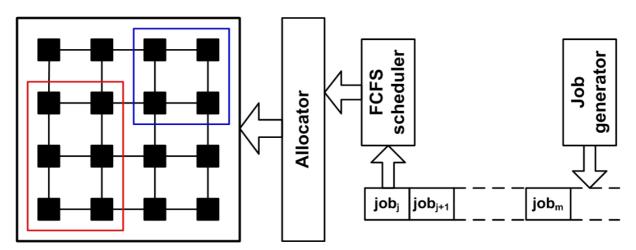

Applications running in multiprocessor systems such as supercomputers, data centers or multicore processor integrated circuit chips are typically parallel, which means that separate tasks are executed concurrently on a set of di erent computing nodes. Such a set of computing nodes – often referred to as a partition – is selected and assigned by a processor allocation algorithm. As processor allocation involves aggregation of a set of physical computing nodes into a virtual processor that is assigned to execute a parallel application, it is a kind of virtualization. It is also a main topic of this thesis. E cient processor allocation is an important challenge for multiprocessor systems that host a number of di erent parallel applications at a time. A high utilization of a system's computing resources; short queuing times and running times for applications; as well as isolation of tra c between partitions (tra c-containment) are examples of desirable qualities of a processor allocation algorithm. Some of these qualities are hard to combine. In particular, many processor allocation algorithms achieve tra c-containment only at the cost of a significantly reduced utilization of a system's computing resources.

### 1.1 Contributions

Investigation and proposal of new or improved solutions to topology agnostic routing and reconfiguration of interconnection networks are main objectives of this thesis. In addition, topology agnostic routing and reconfiguration algorithms are utilized in the development of new and flexible approaches to processor allocation. We aim to present versatile solutions that can be used for the interconnection networks of a number of di erent computing systems, including supercomputers, data centers and multicore processor integrated circuit chips.

The main focus of this thesis is on performance issues. Nevertheless, e cient methods for routing, reconfiguration and processor allocation are also important for the realization of energy-e cient computing systems. A manifestation of the overall increased awareness of environmental challenges in high performance computing is the emergence of the Green500 list [88] which ranks supercomputers according to their energy-e ciency.

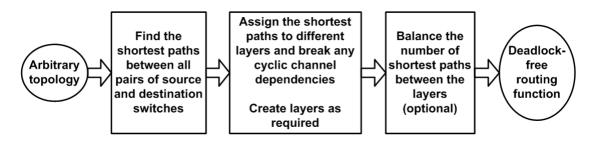

### 1.1.1 Routing

The Advanced Switching Interconnect (ASI) specification [17] did not prescribe a particular routing algorithm. On the purpose to select a suitable routing algorithm for the ASI technology [150], we perform a systematic evaluation of a number of existing routing algorithms. We state a set of criteria that a routing algorithm for ASI should comply with, and show that one of the existing topology agnostic routing algorithms fulfils all of the criteria. This routing algorithm – Layered Shortest Path (LASH) [144,218] – is recommended to be used with ASI. We demonstrate the abilities of LASH as a static fault tolerance mechanism for mesh and torus topologies. Moreover, we introduce an optimization which allows LASH to achieve as high performance for mesh topologies as one of the established routing algorithms tailored for mesh topologies achieves. In addition, we demonstrate how the optimization allows LASH to maintain its qualities as a static fault tolerance mechanism. After our study was conducted, the ASI specification process was discontinued. Nevertheless, the ASI technology is now incorporated in Dolphin Express [122], and the results of our study are thus still of interest for this technology. In addition, we explain how most of our considerations regarding routing in ASI are also relevant for routing in InfiniBand [105].

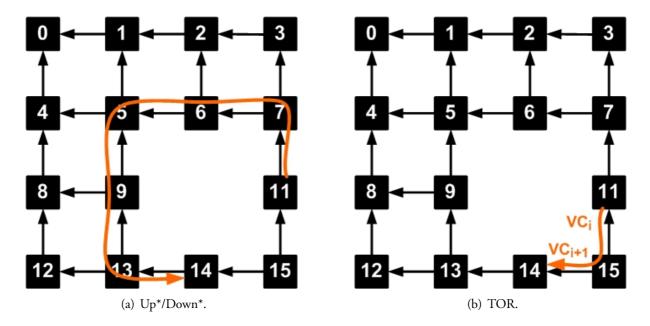

## 1.1.2 Reconfiguration

Reconfiguration is a deadlock prone process, and some existing reconfiguration strategies include deadlock avoidance mechanisms that significantly reduce the network service o ered to running applications. We propose a new dynamic reconfiguration algorithm, RecTOR, which supports a replacement of the routing function without causing performance penalties. RecTOR is conceptually simple, and targets systems that apply the flexible and topology agnostic Transition-Oriented Routing (TOR) algorithm [200]. As RecTOR does not require complex network switches, it is also simple to realize.

Overlapping Reconfiguration (OR) [139, 140] is a versatile and highly e cient reconfiguration algorithm that was previously only usable in distributed routing systems. We introduce an adaptation that allows using OR also in source routing systems (such as Dolphin Express). Furthermore, we investigate how the performance of OR is influenced by di erent levels of synchronization of the initiation of a reconfiguration process. In addition, we propose an optimization of OR which,

during a reconfiguration of a source routing system, aims to provide a better network service to the running applications.

### 1.1.3 Processor allocation (virtualization)

Processor allocation strategies that guarantee tra c-containment commonly pose strict requirements on the shape of partitions, and thus achieve only a limited utilization of a system's computing resources. We introduce two new approaches to tra c-contained processor allocation which are more flexible, and which are also conceptually simple. Our first approach is a new processor allocation algorithm – UDFlex – for systems that use the Up\*/Down\* routing algorithm [204]. Our second approach is a framework for developing new processor allocation algorithms. Both approaches utilize the properties of a topology agnostic routing algorithm in order to enforce tra c-containment within arbitrarily shaped partitions. Consequently, our approaches achieve a high resource utilization as well as isolation of tra c between di erent applications. To di erent degrees, both of our approaches depend on reconfiguration. When compared to the use of a traditional processor allocation strategy (such as one that allocates sub-mesh shaped partitions in a mesh or torus topology) the use of either UDFlex or our framework is expected to entail a certain amount of allocation and communication overhead. We assess the amount of such overhead that can be tolerated before the advantages of UDFlex over sub-mesh allocating strategies are neutralized. In addition, for a large set of arbitrarily shaped partitions, each executing a communication intensive application, we investigate costs and benefits of tra c-containment (as prescribed by our framework) versus non-tra c-containment.

## 1.2 Thesis organization

Chapter 2 provides background information on various topics within the area of interconnection networks that are relevant to this thesis. Examples include topology, flow control, deadlock, fault models, routing, reconfiguration and topology agnosticism. In addition, processor allocation and virtualization are introduced in Chapter 2. Chapter 3 presents the research methods used in our studies and provides a general description of our simulator models. (The particular setups of our simulation experiments are explained in Chapters 4, 5 and 6 for each of the individual studies.) Chapter 4 presents our endeavours to realize e cient routing for the ASI/Dolphin Express technology. Our contributions to the field of reconfiguration are found in Chapter 5, whereas Chapter 6 presents our studies on processor allocation. Each of Chapters 4, 5 and 6 also includes a discussion on related work and our contribution; a critical view on our own research; and possible paths for future research. Finally, Chapter 7 summarizes our conclusions and plans for future research.

### 1.3 Publications

The research results presented in Chapters 4, 5 and 6 of this thesis are mainly based on the following publications.

• Å. G. Solheim, O. Lysne, T. Skeie, T. Sødring, I. Theiss, and I. Johnson. Routing for the ASI Fabric Manager. *IEEE Communications Magazine*, 44(7):39–44, July 2006.

- Å. G. Solheim, O. Lysne, A. Bermúdez, R. Casado, T. Sødring, T. Skeie, and A. Robles-Gómez. E cient and deadlock-free reconfiguration for source routed networks. In 9th Workshop on Communication Architecture for Clusters, 2009.

- Å. G. Solheim, O. Lysne, and T. Skeie. RecTOR: A new and e cient method for dynamic network reconfiguration. In *15th International Euro-Par Conference*, pages 1052–1064, 2009.

- Å. G. Solheim, O. Lysne, T. Sødring, T. Skeie, and J. A. Libak. Routing-contained virtualization based on Up\*/Down\* forwarding. In *14th International Conference on High Performance Computing*, pages 500–513, 2007.

- Å. G. Solheim, O. Lysne, T. Skeie, T. Sødring, and S.-A. Reinemo. A framework for routing and resource allocation in network virtualization. In *16th International Conference on High Performance Computing*, pages 129–139, 2009.

- O. Lysne, S.-A. Reinemo, T. Skeie, Å. G. Solheim, T. Sødring, L. P. Huse, and B. D. Johnsen. Interconnection networks: Architectural challenges for utility computing data centers. *IEEE Computer*, 41(9):62–69, September 2008.

# Chapter 2

# Interconnection networks

This chapter provides background information on various topics within the area of interconnection networks that are of relevance to this thesis. The term *interconnection network* normally refers to a high capacity communication network of limited physical extent that provides high throughput, low latency and lossless communication. This is also the definition assumed in this thesis (although the two main textbooks on interconnection networks [57,68] do not distinguish between interconnection networks and computer networks in general).

Interconnection networks are used in a variety of computing systems in order to enable communication between their diverse system units. For instance, such networks are used to interconnect computing nodes in a cluster or supercomputer; processing units, memory modules and input/output devices within a computer; ports and processing elements within a router or switch; cores and caches on a multicore chip; and computing nodes, storage devices and gateways towards external networks in a data center. For simplicity, we collectively refer to the diverse communicating system units as *processing nodes*.

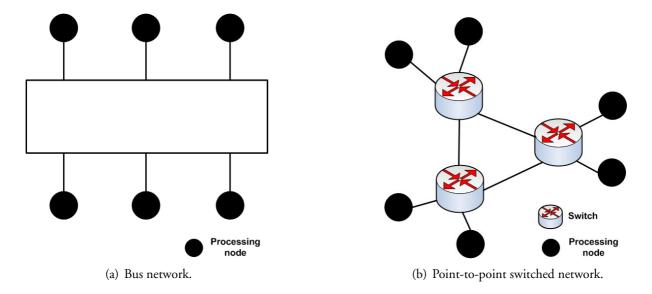

The extent of interconnection networks typically spans from small networks on integrated circuit chips (NoCs) up to networks as large as local-area networks. Often, interconnection networks are classified according to their structure, and the main categories used by [68] are shared-medium, direct, indirect and hybrid networks. Shared-medium networks share a common multidrop bus; both direct and indirect networks are point-to-point switched structures; whereas hybrid networks contain elements both from the shared-medium and point-to-point switched networks. A multidrop bus is a common but simple interconnection network where all the processing nodes share a single communication medium, the bus. Only one processing node at a time can utilize the bus for message transmission, and a message is broadcast to all the processing nodes connected to the bus. Thus, a bus interconnection network prohibits parallel transmission of messages. This limits performance as the size of computing systems increases. A point-to-point switched interconnection network, on the other hand, encourages parallel transmission of messages, and thereby supports scalability and higher performance. In such a network, a physical communication channel connects two nodes, where a node is either a processing node, a switch, or a combined node (which contains both processing and switching elements). A message may traverse one or more intermediate nodes on its path from a source to destination node. Figures 2.1(a) and 2.1(b) illustrate a bus and a point-to-point switched interconnection network, respectively.

Historically, most interconnection networks used a shared communication medium. Nowadays, however, point-to-point switched networks are widespread. The focus of this thesis is on

Figure 2.1: Examples of a bus and point-to-point switched interconnection network.

point-to-point switched networks, not on shared-medium or hybrid networks. A number of different network technologies exist that support the construction of point-to-point switched interconnection networks, including Ethernet [102,206], InfiniBand [105] and Dolphin Express [122]. Point-to-point switched networks can be assembled in a number of different manners, and a variety of strategies exist for transportation of data through such networks. An interconnection network's structure, flow control and switching strategy, as well as its routing algorithm, are factors which may have a significant influence on the performance of a computing system. Sections 2.1, 2.2 and 2.5 provide background information on each of these issues.

The risk of packet deadlock is an important challenge for interconnection networks that provide lossless communication. Section 2.3 discusses how the deadlock risk arises from dependencies between the bu ers of di erent communication channels in such networks.

Reliable interconnection networks are essential for the operation of current high-performance computing systems. The ability to e ciently reconfigure an interconnection network is an important challenge in the e ort to support a reliable network service. A reconfiguration is needed in order to restore a connected routing function when changes in the structure of an interconnection network have caused a disconnection of the present routing function. Such changes could be the result of component faults, and Section 2.4 gives an overview of the most relevant fault models for interconnection networks. Furthermore, Section 2.6 introduces the concept of reconfiguration, which is one of the main topics of this thesis.

Another main topic of this thesis – processor allocation (virtualization) – is presented in Section 2.7. Processor allocation involves assignment of sets of processing nodes to execute parallel jobs that run concurrently in a multiprocessor system such as a supercomputer, multicore chip or data center. The processor allocation strategy has impact on the running and queuing times of individual jobs, as well as on the utilization of resources and throughput of jobs in a system. Processing nodes are connected by an interconnection network; many existing processor allocation strategies are conscious of network issues such as topology and routing (see e.g. [251,255]); and the methods developed in this thesis are routing aware (but topology agnostic). Therefore, we chose to include the background information on processor allocation into this chapter on interconnection networks.

The main objective of this thesis is to investigate and propose methods for routing, reconfiguration and processor allocation that do not assume a particular topology for the interconnection network. Therefore, Section 2.8 provides a discussion on topology agnostic methods, including an overview of existing strategies.

A large part of this chapter is based on information found in [57,68]. In addition, information has been derived from [171].

## 2.1 Topology

The nodes and communication channels of a point-to-point switched interconnection network can be connected in a variety of patterns, and the structure of a network is referred to as the network's *topology*. A node is either a switch, a processing node or a combined node, where a combined node comprises a switching element and one or more processing elements.

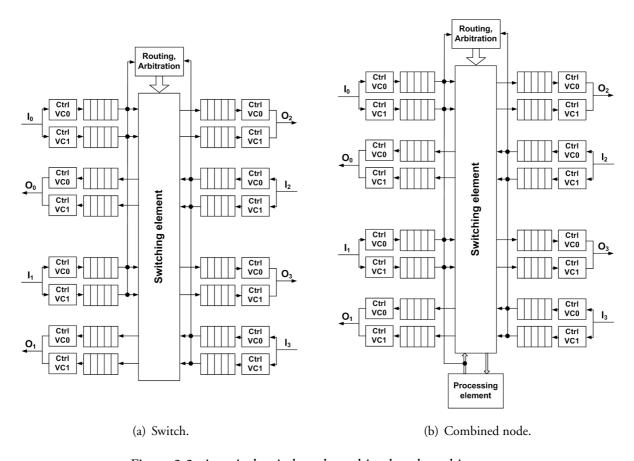

Figure 2.2: A typical switch and combined node architecture.

Figure 2.2(a) gives an example of a switch architecture. Switches may either be input bu ered, output bu ered or both. In this thesis, unless otherwise stated, we assume that switches contain both input (ingress) bu ers and output (egress) bu ers. Figure 2.2(b) illustrates a corresponding combined node with one processing element (details regarding bu ering and control between the processing and switching elements are not shown). Both the switch and combined node have four bidirectional ports, where the input physical channels are labelled  $I_0 - I_3$  and the output physical channels are labelled  $O_0 - O_3$ . Each physical channel has two virtual channels (VCs) [54], labelled VC0 and VC1, with a separate control unit (Ctrl). The routing and arbitration unit decides

which ingress to egress connections are set up by the switching element. Some switches implement *virtual output queuing*, which means that an input bu er is organized in such a way that packets bound for di erent output channels are enqueued separately. The purpose of such a bu er organization is to avoid *head-of-line blocking*. Head-of-line blocking occurs when a packet bound for one output channel blocks subsequent packets bound for other vacant output channels. (Virtual output queuing is not illustrated in Figure 2.2.)

The topology of an interconnection network is often visualized as a graph. The mapping of an interconnection network I onto a graph G is then expressed formally as I = G(N, C), where the vertexes N and the edges C of the graph represent, respectively, the network's switching elements and the communication channels that connect these switching elements. The graph may be directed or undirected, depending on whether the communication channels are unidirectional or bidirectional. The graph representation eases the reasoning about various issues related to the topology of an interconnection network, such as connectivity, path lengths, path diversity and bisection bandwidth (all of which will be discussed in this section). Furthermore, the graph representation is advantageous as it enables the use of graph theory in the development of solutions to many of the challenges faced by interconnection networks – such as deadlock avoidance, routing and reconfiguration (all of which will be discussed in later sections).

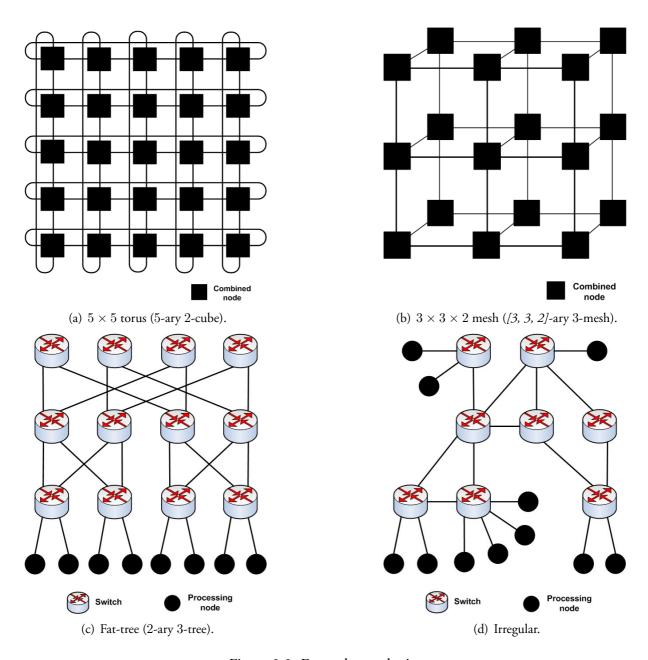

Interconnection networks can assume a number of di erent topologies, and Figure 2.3 illustrates a few of the alternatives. Torus topologies are often called k-ary n-cubes (sometimes a mesh is also referred to as a k-ary n-cube or k-ary n-mesh). Such topologies consist of n dimensions with k switching elements in each dimension, where the radix, k, can be di erent for each dimension. Figures 2.3(a) and 2.3(b) depict a  $5 \times 5$  torus (5-ary 2-cube) and  $3 \times 3 \times 2$  mesh ([3, 3, 2]-ary 3-mesh), respectively. Meshes and tori are described in [68] as *strictly orthogonal* topologies, as the switching elements are arranged in an n-dimensional grid with k nodes in each dimension, and every switching element is an intersection between all dimensions. Assume that in each dimension each switching element is assigned a coordinate i, where  $0 \le i \le k-1$ . Then, a mesh is assembled by connecting switching element number i with the switching elements numbered i-1 and i+1, for each value of i and for each dimension. These connections are also used for the torus topology. In addition, a torus utilizes so called wraparound channels, which means that, in each dimension, the switching elements numbered 0 and k-1 are also interconnected. The wraparound channels e ectively make a torus topology a set of interconnected rings.

Multistage interconnection networks are a group of networks that consist of several stages of switches where processing nodes are connected only to the first and final stages of switches (possibly only on one side of the network if it is bidirectional). Examples of multistage interconnection networks include fat-trees [126], Clos [48], Benês [24] and Delta [169] networks. Some of these subgroups of multistage interconnection networks overlap. For instance, according to [176], a k-ary n-tree [176] is both a class of fat-trees and a Delta network. A k-ary n-tree is constructed by interconnecting n stages of switches such that, except in the first and final stage, each switch connects to k switches in the previous stage and k switches in the next stage of the tree. A 2-ary 3-tree is depicted in Figure 2.3(c).

Multistage interconnection networks are often used for large high capacity systems, and, in general, they are expensive due to the high number of switches relative to the number of processing nodes. In addition, long cables are in general required. Expansion of such topologies either requires switches with a higher number of ports or a large number of additional switches. Torus and mesh

Figure 2.3: Example topologies.

topologies, on the other hand, can be expanded without the requirement of larger switches. Furthermore, cable lengths can be kept short, and simple routing algorithms can be implemented in hardware (without the need for routing tables). The Top500 list of supercomputers [237] shows that, for the most powerful supercomputers, fat-trees and tori are common interconnection network topologies. Currently, many data centers are based on Ethernet [206], and, as this technology by default uses a spanning tree protocol for routing, tree topologies are frequently used for the interconnection network. Arguments for fat-trees as an appropriate topology for data centers based on Ethernet are presented in [8]. For on-chip interconnection networks, two-dimensional meshes and tori have been suggested as suitable topologies (see e.g. [56, 124]), and those were evaluated in [167] together with a few other candidate topologies.

In the interconnection network literature, network topologies with nodes and communication channels arranged according to one of a set of standard structures are commonly denoted *regular*.

Network topologies with no such standard structure, on the other hand, are commonly denoted *irregular*. We adopt this convention.<sup>1</sup> Examples of regular network topologies include meshes, tori, hypercubes (2-ary *n*-cubes), fat-trees, Delta, Clos and Benês networks.

A network of workstations [12] is a computer cluster consisting of a set of commodity computers interconnected by a number of switches and communication channels. The switches and communication channels are typically arranged in an arbitrary pattern. Thus, a network of workstations commonly has an irregular topology. Typically, for an irregular network topology, some of the switches have one or more processing nodes attached, whereas others are solely connected to other switches. Irregular network topologies are easily expandable as no particular structure must be maintained. Some issues, such as routing which is described in more detail in Section 2.5, are in general more challenging for an irregular topology than for a regular topology. Figure 2.3(d) gives an example of an irregular network topology. A non-regular (or semi-irregular) topology may also be the result of faults in switching elements or communication channels of an initially regular network topology.

Point-to-point switched interconnection networks are commonly categorized as either *direct* or *indirect* networks. All the nodes of a direct network are combined nodes (see Figure 2.2(b)) which include both switching and processing elements. In an indirect network, on the other hand, a switch and processing node are separate entities connected by a communication channel. Typical examples of indirect networks are multistage interconnection networks (where processing nodes are connected only to the first and final stages of switches) and networks of workstations (where individual computers are connected by switches). Torus, mesh, ring and hypercube topologies, on the other hand, are often realized using combined nodes, and are thus often direct networks. However, all direct networks can be implemented as indirect networks by replacing each combined node with a switch node and a processing node [57]. Thus, this thesis will not further emphasize the distinction between direct and indirect networks, and in the following a "switch" could also refer to the switching element of a combined node.

A topology is *connected* if at least one path exists from every source to every destination processing node. Faults in switches or communication channels could disconnect a previously connected topology. *Path diversity*, which quantifies the existence of alternative paths between sources and destinations in a network, is an important characteristic of a topology for several reasons, e.g. for trace balancing and fault tolerance. Assume that m disjoint paths exist from a source processing node s to a destination processing node s. Then, if a flexible routing strategy is used and in-order packet delivery is not required, trace balancing could be achieved by distributing messages across the s paths. Congestion might result if several dierent sources and destinations share a section of their paths. Such congestion could be prevented if alternative paths were used such that fewer sources and destinations shared sections of the paths. Assume that a fault in a switch or communication channel destroys a path s0 from s1 to s0. Then, if s0 was the only available path from s1 to s0, the topology has been disconnected by the fault, and s2 and s3 and s4 can no longer communicate. If, on the other hand, s2 disjoint paths existed from s3 to s3 before the fault, another path s4 could be taken into use after the destruction of s5.

The minimum length of a path from s to d is another important property of a network's topology. Path lengths are decided by the number of intermediate switches that must be traversed, and

<sup>&</sup>lt;sup>1</sup>Even though according to the strict definition given in [68] a network topology is regular only if every switch has the same number of neighbours – which e.g. includes tori but excludes meshes.

the diameter of a topology is the length of the longest minimal path.

The number of communication channels that connect a switch to other switches is referred to as the *node degree*. A fully connected topology of a significant size, where each switch is connected to all other switches, is an example of a topology with a high node degree. A ring, on the other hand, is an example of a topology with a low node degree, as each switch is connected to only two other switches. When comparing two equally large network topologies where one has a high node degree and the other has a low node degree, the former most likely has a shorter diameter than the latter.

A bisection of the topology results from a supposed removal of the smallest set  $S_{min}$  of communication channels that would cut the topology into two equally large halves. The *bisection bandwidth* is the aggregated transmission capacity of the communication channels in  $S_{min}$ , and quantifies the amount of data that can be transferred from one part of the topology to the other within a certain time frame. As opposed to the bisection bandwidth, the *e ective bisection bandwidth* introduced in [97] takes the routing function into consideration.

Physically, interconnection networks can be implemented in a number of di erent ways, ranging from small networks on a silicon die, via larger networks spanning a number of circuit boards, to large networks interconnecting racks or containers of processing nodes and switches in a data center. Numerous restrictions and tradeo s apply for the physical implementation of an interconnection network. A few of them are related to issues such as the quality of the silicon chip manufacturing process, the pin count of a chip, the length and width of the communication channels on a circuit board, and the selection of the optical or electrical cables for connecting racks or containers. The physical layout of an interconnection network is an important challenge. It is, however, not within the scope of this thesis.

## 2.2 Flow control and switching

Due to strict requirements on high system throughput and low packet latency, packet loss and subsequent retransmission are in general not acceptable for an interconnection network.

Thus, flow control mechanisms are needed in order to ensure that data transfer is not started unless su cient bu er space is available at the receiving end. Such mechanisms are needed both for the transfer of data through a single switch and for the transfer of data from one switching/processing node to another.

This thesis refers to the mechanisms used for controlling data transfer from an ingress to an egress bu er within a switch as *switching* mechanisms (recall that we assume input and output bu ered switches), whereas the mechanisms used between two separate nodes are referred to as *flow control* mechanisms.

Switching and flow control are closely intertwined, which is illustrated by the di erent approaches taken to explain these concepts by the two main textbooks on interconnection networks [57, 68]. Whereas [57] refers to both the intra and inter node mechanisms as flow control (and does not even include the word "switching" in its index), switching is an emphasized term in [68].

A *message* is the unit of information input from a source processing node for transportation through the interconnection network and delivery to a destination processing node. The interconnection network segments a message into several *packets* if it is longer than the maximum allowed

packet size. A packet may be further segmented into several flow control units (*flits*<sup>2</sup>), which, as the name implies, is the unit of information on which flow control is enforced. A flit can be segmented into several physical units (*phits*), where one phit represents the width of a physical communication channel – that is, the amount of information that can be transmitted on a physical communication channel per clock cycle.

### 2.2.1 Switching mechanisms

Virtual cut-through [114] and wormhole [54] switching are common switching mechanisms for current interconnection networks. Like store-and-forward switching, and unlike circuit switching, virtual cut-through and wormhole switching do not reserve resources in advance of the data transmission.<sup>3</sup> On its path from a source to destination processing node, a packet must share the available bu er space of an intermediate switch with other packets that traverse the same switch. However, the virtual cut-through, wormhole and store-and-forward switching mechanisms di er with respect to the point in time when data transmission from an ingress to egress bu er of a switch can be started. Each packet carries the routing information in its header. Nevertheless, with store-and-forward switching the entire packet must have been received by an ingress bu er before the decision on which egress bu er to forward the packet to is taken. Virtual cut-through and wormhole switching, on the other hand, support reduced latency by making the routing decision as soon as the routing information contained in the packet header has been received. Thus, provided that su cient egress bu er space is available and that the packet is selected by the arbitration algorithm, the head of the packet can be forwarded through the switch before the tail of the packet has reached the ingress bu er.

Virtual cut-through, wormhole and store-and-forward switching also di er with respect to the flit size. Both virtual-cut through and store-and-forward switching require that the flit size equals the packet size. Then, when the head of a packet is blocked, the tail catches up and the entire packet is stored in the same bu er. Wormhole switching (which supports small and cheap bu ers and is currently a popular choice for on-chip networks), on the other hand, does not assume a maximum packet size, and each bu er typically does not have space for an entire packet. Thus, while the head of a packet is blocked, the packet may span several switches. Due to these di erent characteristics, ensuring deadlock-freedom is more challenging for wormhole switching than for virtual cut-through and store-and-forward switching. The deadlock issue will be further discussed in Section 2.3.

#### 2.2.2 Flow control mechanisms

The most commonly used flow control mechanisms for interconnection networks ensure that an upstream switch or processing node defers transmission of flits until a su cient amount of bu er space is available to store the flits in a downstream node. This requires that a downstream node informs an upstream node about bu er space availability. The two most common flow control mechanisms for interconnection networks are called *credit-based* and *onlo* flow control [57].

With credit-based flow control the upstream node maintains a credit counter which indicates the amount of free bu er space in the downstream node, and thus the number of flits that can

<sup>&</sup>lt;sup>2</sup>Also known as flow control digits.

<sup>&</sup>lt;sup>3</sup>See e.g. [68] for a description of store-and-forward and circuit switching.

currently be transmitted. The credit counter is decremented according to the number of flits transmitted from the upstream node to the downstream node. The credit counter is incremented upon reception of credit updates from the downstream node, which are sent in order to communicate to the upstream node that bu er space has become available. Thus, with credit-based flow control, a significant amount of information is normally transmitted merely to update the credit counter.

On/o flow control is a simpler mechanism that reduces the transmitted amount of control information concerning available bu er space in the downstream node. The upstream node maintains a flag to indicate whether or not flits can currently be transmitted. If the value of the flag is on the upstream node can transmit flits, whereas transmission must be deferred if the value of the flag is o. The downstream node need only inform the upstream node when the value of the flag must be changed. The flag must be turned o if the amount of available bu er space decreases below a certain threshold. Likewise, the flag must be turned on if the amount of available bu er space increases above a certain threshold. The threshold values that decide when data transmission is switched on and o respectively, are not necessarily the same.

A number of VCs may share a single physical communication channel. In that case, all VCs transmit packets over the same physical communication channel, whereas each VC has a separate set of bu ers and a separate flow control mechanism [52] (as illustrated in Figure 2.2). This means that the upstream node keeps state information (a credit counter or flag) for each VC, and the downstream node transmits updates with regard to bu er availability for each VC. Thus, VCs enable other packets to bypass a blocked packet, and are useful e.g. for implementation of deadlock avoidance and service di erentiation mechanisms.

In this thesis, a *virtual layer* is a virtual network that consists of all the switches and processing nodes of the physical network. In addition, the virtual layer includes a subset of the VCs such that, for each physical communication channel, one VC in each direction belongs to the virtual layer. (A virtual layer is sometimes referred to as a *layer* for short.)

The flow control mechanism has an important impact on the performance of the interconnection network. A bad flow control mechanism could keep a communication channel idle for part of the time, and thus cause increased packet latency and decreased system throughput. In order to support a constant flow of data on a communication channel, the bu er size – and, for on/o flow control, the on/o threshold values – must be carefully set, considering such parameters as channel bandwidth, round-trip time and flit length.

Optimistic flow control mechanisms, such as ACK/NACK (acknowledgement/negative acknowledgement), are not commonly used for interconnection networks due to ine cient use of bu ers and communication channels. With ACK/NACK the upstream node does not keep track of free bu er space in the downstream node, and simply transmits a flit at any time. When bu er space is not available, the downstream node discards the flit and returns a NACK. Such a mechanism requires retransmission of the discarded flits and, as flits may be received out of order, reordering of the received flits in the downstream node.

## 2.3 Channel dependency and deadlock

The flow control mechanism enforced on each communication channel in order to support lossless communication prevents a packet from moving until su cient bu er space is available on the receiving end of a communication channel. This causes a risk of deadlock as several packets may

be mutually waiting for each other to move. In a deadlocked set of packets none of the packets in the set can advance until another packet in the set advances. All the packets in the set are thus blocked forever, and the blockage spreads as packets in the deadlocked set block subsequently arriving packets. Such a situation is not consistent with a successful operation of an interconnection network.

Another potential problem caused by lossless flow control arises in the case of congestion. As the flow control mechanism does not allow a packet to advance until free bu er space is available on the receiving end of a communication channel, saturation trees [178] may form. That is, the congestion spreads out in the network, possibly also a ecting tra c not heading towards the original point of congestion. Congestion management mechanisms are studied e.g. in [66, 87, 92]. Although congestion control is an important topic for interconnection networks, it is not a main topic of this thesis.

In the following, we first give an introduction to the theory concerning deadlock, before two alternative approaches to handling this problem are presented. In this thesis, we do not focus on high-level deadlocks that may result from a lack of bu er management for request-reply protocols used e.g. for memory read or write operations.

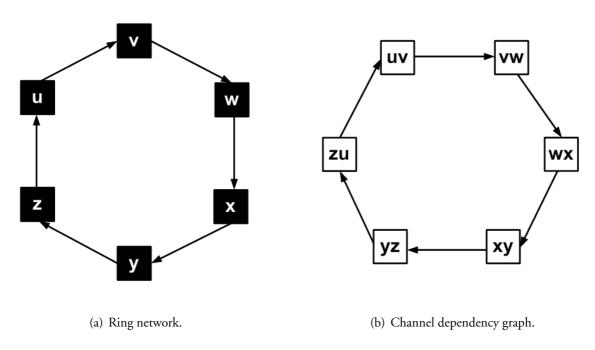

Figure 2.4: A 6-node unidirectional ring network and the corresponding channel dependency graph.

If a flit can use a communication channel  $c_b$  immediately after a communication channel  $c_a$  there is a direct *channel dependency* [55] from  $c_a$  to  $c_b$ . A channel dependency expresses that the advancement of a flit from  $c_a$  to the next channel  $c_b$  depends on available bu er space in  $c_b$ . A *channel dependency graph* [55], which visualizes all the direct channel dependencies of an interconnection network, is a useful aid for reasoning about deadlock-freedom. The vertexes and edges of this directed graph represent the communication channels of the interconnection network and the dependencies between these channels, respectively. For wormhole switching, a blocked packet might spread out over the bu ers of several consecutive switches. Thus, strictly speaking, there are

also direct dependencies between non-adjacent channels. These are normally not included in the channel dependency graph, however, as they do not provide new information for reasoning about deadlock.

Figure 2.4(a) shows an interconnection network with six combined nodes labelled u through z connected in a ring topology. The communication channels are unidirectional, packets are routed in the clockwise direction, and VCs are not supported. The corresponding channel dependency graph is shown in Figure 2.4(b), where each communication channel is labelled according to its source and sink nodes. Deadlock-freedom cannot be guaranteed for this interconnection network. Let us consider a situation where all the bu-ers of the network are full. Assume that the first packet in the input bu-er of node u, v, w, x, y, and z is destined for node v, w, x, y, z, and u, respectively. In this set of packets none of the packets can advance before one of the other packets advances. Thus, this example illustrates an established deadlock.

We will discuss various aspects of routing in Section 2.5. For now, we briefly mention two definitions. First, for *deterministic routing*, as opposed to *adaptive routing*, only one path is provided from a source to destination processing node. Second, a routing function is *connected* if it provides at least one path between every pair of source and destination processing nodes.

For deterministic routing, [55] showed that a necessary and su cient condition for deadlockfreedom is that the channel dependency graph is free of cycles. This also follows as a corollary of the theorems provided for adaptive routing in [64] for wormhole switched networks and in [65] for virtual cut-through and store-and-forward switched networks. These theorems state that an adaptive routing function R is deadlock-free given that a connected routing subfunction  $R' \subseteq R$ exists that does not have cycles in its extended channel dependency graph [64]. For virtual cutthrough and store-and-forward switching, an extended channel dependency graph may include both direct dependencies and direct cross dependencies. For a wormhole switched network, where a blocked packet can occupy several bu ers, indirect dependencies and indirect cross dependencies may be present in addition to direct dependencies and direct cross dependencies. Let us refer to the channels  $c_e \in R'$  as escape channels, and the channels  $c_{ne} \in R''$ , where R'' = R - R', as nonescape channels. Then, an indirect dependency [63] from one escape channel to another occurs when a packet holds one or more non-escape channels in between two escape channels. Indirect dependencies can be avoided by prohibiting subsequent use of a non-escape channel for a packet that has already used an escape channel. Cross dependencies [64] occur when the set of escape channels overlaps with the set of non-escape channels. According to [57], such overlap is rare in real networks, however. In summary, the theorems provided in [64, 65] express that the channel dependency graph for an adaptive routing function may contain cycles as long as escape channels, which are not part of any cycle, enable dissolution of potential deadlocks.

Two di erent groups of mechanisms are used to prevent a deadlock from ruining the performance of an interconnection network. *Deadlock avoidance* mechanisms, which are most commonly used, ensure that deadlocks cannot occur, whereas *deadlock recovery* mechanisms detect and resolve a deadlock as it occurs. (In addition, a third group of mechanisms – referred to as *deadlock prevention* – allocates the resources to be used in advance. This may significantly limit the utilization of a network's resources [68].)

In order to break cycles of channel dependencies, most deadlock avoidance mechanisms either use VCs or restrict the set of physical paths included in a routing function. Each of these approaches has possible drawbacks, and for both approaches load imbalance may be an issue. For the former

approach the number of VCs required in each switch may be prohibitive. The latter approach causes a reduced path diversity and may thus also cause reduced fault tolerance. Furthermore, for simple routing strategies, restrictions on physical paths alone may not be su cient to avoid deadlock for topologies that include cycles. (This is further explained in Section 2.5.1 for torus topologies.) These drawbacks may be alleviated by using combined mechanisms that apply both VCs and a restricted routing function in order to achieve deadlock-freedom. Section 2.8.1 presents a number of existing topology agnostic routing algorithms, including their deadlock avoidance mechanisms. In addition, Section 2.5.1 provides examples of routing algorithms for meshes and tori, the topologies used in the performance evaluation experiments of this thesis.

Bubble flow control [35] takes a different approach to avoid deadlocks in k-ary n-cube topologies. It assumes that virtual cut-through switching is used and that each buser has space for at least two packets. Exectively, k-ary n-cube topologies consist of a set of rings. Bubble flow control ensures that a packet is inserted into a ring only if, after the insertion, the ring will have buser space for at least one more packet. This ensures that at any time the ring has at least one free buser – a "bubble". Thus, at least one of the packets in the ring is always allowed to advance, which means that deadlock cannot occur. (Starvation is a challenge that should be addressed, however.)

Another approach is proposed in [72] for source routing networks. In order to avoid cycles of channel dependencies, the path of a packet may be split such that the packet is ejected from – and subsequently re-injected into – the network at an intermediate switch. The so-called in-transit bu ers, where ejected packets are temporarily stored, are located in processing nodes. Thus, all switches must have one or more processing nodes attached.

Deadlock recovery mechanisms (such as [13, 116]) are only useful if deadlocks rarely occur. Moreover, running applications must be able to endure a deadlock. A deadlock can be detected by searching for a cycle of blocked packets. Simpler, but less precise, methods based on timeouts have also been proposed. A detected deadlock must be resolved, for instance by discarding one or more packets. This thesis assumes that deadlock must be avoided, and does not focus on deadlock recovery.

### 2.4 Fault models

A variety of component faults can occur in an interconnection network, and the faults can have a number of di erent reasons. In order to simplify the reasoning about faults in an interconnection network, a few categories or models of faults have been introduced [57,68].

One of the categories is referred to as *transient faults*, and includes temporary faults such as bit errors on a physical channel. A metric commonly used to quantify the frequency of such errors is the bit-error rate. Bit errors can be detected and corrected, e.g. by cyclic redundancy checking [175] and forward error correction [94] schemes, respectively.

Another category of faults is the *permanent faults*, which, as the name implies, includes faults that are not temporary. An example of a permanent fault is a switch with a lasting error in the logic of one of its central units, such as the unit responsible for routing and arbitration illustrated in Figure 2.2. The frequency of permanent faults is commonly quantified by the metric mean-time between failures.

Byzantine faults [125] represent a category of faults which is normally discult to handle. A Byzantine fault implies that the failing component does not halt or shut down. On the contrary, in

an erroneous and arbitrary way it proceeds operation.

This thesis addresses challenges related to routing and reconfiguration after the occurrence of faults. In particular, we focus on deadlock avoidance and performance issues. Our interest in faults is restricted to permanent failures of the physical communication channels and switches of an interconnection network. Faults may also occur in other components of a computing system, however, such as in processing nodes, power supplies, clocks and fans. We assume that transient faults, such as bit errors on a physical communication channel, are corrected locally and do not focus on this type of faults. If a specific network component produces transient faults more frequently than acceptable, the component may be shut down and the fault can then be considered permanent [57]. Our attention is restricted to permanent faults that can be described as *fail-stop* [203]. Basically, a fail-stop fault implies that some internal or external supervisory module detects the failure of a network component and subsequently informs neighbouring components. Furthermore, we assume the presence of robust fault detection systems which are able to detect a Byzantine fault, shut down the faulty network component, inform the neighbours, and thereby reduce the Byzantine fault to a fail-stop. In this thesis, we focus on both *static* and *dynamic* faults. The former category includes faults that are present at the start-up of a computing system, whereas the latter category includes faults that occur while a system is in operation. In general, handling dynamic faults is more challenging than handling static faults.

## 2.5 Routing

A routing algorithm is responsible for providing the path that a packet is to take from its source to destination processing node. Existing routing algorithms vary in a number of di erent respects – such as in the following: where the routing decision is taken; number of destinations for each packet; input parameters; deadlock avoidance mechanism; implementation (by programmable routing tables or hardware logic circuits); whether several alternative paths are provided (and how one of them is selected); whether a specific network topology is assumed; whether the paths provided correspond to the shortest paths in the physical topology; and whether in-order delivery of packets, load balancing and fault tolerance are supported.

Two separate units, a *routing function* and a *selection function*, constitute the routing algorithm. A routing function must be *connected*, that is, it must provide at least one path between every pair of source and destination processing nodes in the network. Otherwise, the routing function is *disconnected*, which means that some of the system's processing nodes cannot communicate. As input some routing functions accept a pair of nodes (either the source and destination processing nodes, or the current switch and the destination processing node). Others accept the current input channel of a switch and the destination processing node as input. As output some routing functions return a set of alternative paths that the packet could follow from its source to destination processing node, whereas others return a set of alternative output channels from the current switch. The selection function chooses one of the alternative paths or output channels, and thus decides the exact route of the packet.

This thesis is only concerned with unicast routing, where a packet is transmitted from one source to one destination, and not with multicast routing, where a packet can be transmitted from one source to several destinations.

A routing decision may be taken either once at the source processing node or incrementally

at each intermediate switch. Using the former approach, referred to as *source routing*, the entire path of a packet is set at the source processing node and included in the header of the packet. Using the latter approach, referred to as *distributed routing*, a packet merely carries the address of its destination processing node. Upon arrival at an input channel of an intermediate switch, this switch decides the output channel on which to forward the packet. For the switch illustrated in Figure 2.2, this decision would be taken by the routing and arbitration module.

Source and distributed routing have their own advantages and disadvantages. In general, the total amount of routing table information is higher in a source routing system than in a distributed routing system. In addition, with source routing, the overhead in each packet is normally larger as the entire path is included in the packet header. On the other hand, a source routing switch may be simpler and faster than a distributing routing switch. A packet may be forwarded more quickly by a source routing switch as the output channel is included in the packet header. A distributed routing switch must perform a lookup in its routing table, and possibly select one of several alternative output channels. As the path of a source routed packet cannot be changed at an intermediate switch, source routing is in some respects less flexible than distributed routing is. In other respects, source routing provides more flexibility than distributed routing does: Assume that two source processing nodes,  $s_0$  and  $s_1$ , transmit packets towards a common destination processing node, d, and that these packets arrive on the same input channel of an intermediate switch i. Then, with distributed routing, the packets from  $s_0$  and  $s_1$  are bound to share the same set of paths from i to d. With source routing, on the other hand, the set of paths from  $s_0$  to d is independent of the set of paths from  $s_1$  to d. Dolphin Express [122] and InfiniBand [105] are examples of source and distributed routing interconnection network technologies, respectively.

Routing tables, included in either source processing nodes or intermediate switches, are flexible since they are programmable. At the cost of flexibility, some simple routing algorithms for regular network topologies can be implemented in hardware. Such an approach can provide fast routing without requiring storage space for routing information, and is often referred to as *algorithmic routing*. Dimension-Order Routing (DOR) [231] for mesh and torus topologies is an example of a routing algorithm that can be implemented in hardware. At the expense of some additional logic per switch port, Logic-Based Distributed Routing (LBDR) [73] enables hardware implementations of more flexible routing algorithms than DOR. LBDR targets on-chip networks that conform to a defined set of regular and semi-irregular mesh-based topologies. Flexible DOR (FDOR) [219] is another algorithmic routing method designed for on-chip networks. When compared to DOR, FDOR only requires a single additional configuration bit in each switch. Thus, FDOR has lower implementation costs, but in some respects also less flexibility, than LBDR has. Recently, [209] added multicast capability to FDOR as well as an increased flexibility with respect to the supported shapes of mesh-based topologies. These extensions entail a higher implementation cost, however.

A routing algorithm may be either *deterministic*, *oblivious* or *adaptive*. A deterministic algorithm (see e.g. [231]) provides only one path from a source to destination processing node. That is, the routing function returns only one path or output channel, and a selection function is not needed. The set of deterministic algorithms is a subset of the set of oblivious algorithms. Oblivious algorithms (see e.g. [160]) may support more than one path from a source to a destination, and for each packet one of the alternative paths is selected without consideration of network state. The selection function may for instance randomly choose one path/channel from the set of paths/channels returned by the routing function. Like oblivious algorithms, adaptive algorithms (see e.g. [53])

provide more than one possible path from a source to a destination. As opposed to oblivious algorithms, however, adaptive algorithms take network state into account when selecting one of the alternative paths. For instance are the alternative output channels' queue lengths – which represent the output channels' load – commonly used in the routing decision [57].

For some applications it is important that packets are delivered at the destination in the same order as they were sent from the source. The packets that must be delivered in order constitute a flow, and a flow identifier can be included in each packet. A deterministic routing algorithm delivers all packets in order as all packets take the same path from a source to a destination. Oblivious routing algorithms can ensure in-order delivery of packets that belong to the same flow by letting the selection function base its choice of path on the flow identifier instead of randomly choosing a path [57]. Adaptive routing algorithms which base the selection of the paths of individual packets on network state do not support in-order delivery of packets.

A routing algorithm may be shortest path, minimal, or non-minimal. This thesis di erentiates between shortest path routing and minimal routing, although in the literature the two terms are sometimes used as synonyms. A shortest path routing algorithm provides a set of paths which are the shortest possible according to the physical topology. A minimal routing algorithm, on the other hand, provides a set of paths which are the shortest possible according to some routing restriction. An example of such a routing restriction is a prohibited down-link to up-link *turn* according to the Up\*/Down\* routing algorithm [204] described in Section 2.8.1. (A "turn" denotes a traversal from one communication channel to another, and for a switch with both input and output bu ering this means a traversal from one of its input bu ers to one of its output bu ers.) A non-minimal routing algorithm is not restricted to providing shortest or minimal paths but may also provide longer paths. The motivation for non-minimal routing may be to better load balancing or to bypass congested communication channels.

Deadlock avoidance is an important concern for most of the routing algorithms proposed for interconnection networks. Section 2.3 explained that, in order to avoid deadlocks, routing restrictions are commonly applied, sometimes in combination with network resources such as VCs. Sections 2.5.1 and 2.8.1 present some of the most important routing algorithms proposed in the literature and their mechanisms for achieving deadlock-freedom.

For routing algorithms that allow *misrouting* (see e.g. [53]), another important issue is the avoidance of *livelock*. Misrouting is a routing decision that brings a packet further away from its destination processing node, for instance in order to stay away from a congested communication channel. A packet is livelocked if it moves around in the network indefinitely without reaching its destination. Livelock is not an issue in source routing systems as the entire path of a packet is decided at the source processing node. For a distributed routing system, a possible approach to livelock avoidance is to limit the number of times a packet can be misrouted in intermediate switches. This thesis is not concerned with the livelock issue, and the routing algorithms in focus do not use misrouting.

Load balancing is important for the performance of an interconnection network, as an imbalance may cause network congestion, increased packet latency and decreased system throughput. As only a single path is supported from a source to a destination, deterministic routing algorithms do not take advantage of any path diversity that the topology might of er in order to balance trade cload throughout the network. Thus, for non-uniform trade patterns, deterministic routing can cause severe performance degradation. Oblivious routing algorithms, on the other hand, may achieve

load balancing by spreading tra c over the available paths, possibly according to some probability distribution. Examples of randomized oblivious routing algorithms that address load balancing include [215, 243]. Adaptive routing algorithms do not necessarily achieve better load balancing than oblivious routing algorithms do. Their path selection, which is often solely based on local knowledge of network state, may not favour global load balancing.

During the operation of an interconnection network, faults may occur in its communication channels and switches. Such faults may disconnect the routing function and disable communication between some of the processing nodes. As only one possible path is provided from a source to a destination, a deterministic routing algorithm, such as [231], is not fault-tolerant in its basic version. Oblivious or adaptive algorithms, on the other hand, may select an alternative path which is not a ected by a fault (if such a path exists).

Some fault-tolerant routing algorithms, such as [84, 95], are only able to handle faults statically – that is, they can handle faults that are present at the start-up of the system. Other algorithms, such as [33, 162, 258], can handle faults dynamically, which means that they support continued operation of the system without requiring a restart.

A semi-irregular network topology may be the result of faults in the switches and communication channels of an originally regular network topology. Such faults could occur while a system is in operation, or they could be present at the start-up of the system. For instance, for an on-chip network, which commonly uses strictly orthogonal topologies such as two-dimensional meshes, a semi-irregular topology could result from faults introduced during the production process. Many routing algorithms assume a specific topology or group of topologies. These algorithms are referred to as *topology specific* routing algorithms, and some of them are described in Section 2.5.1. For semi-irregular topologies that result from faults in regular topologies, such algorithms may not be able to calculate a connected routing function. A number of extensions have been proposed in order to introduce fault tolerance into topology specific routing algorithms, however. Such fault-tolerant algorithms (see e.g. [81, 162]) have the ability to route around a faulty area, and thereby maintain a connected routing function after the failure of some of the communication channels or switches of a network.

When routing around faulty regions, care must be taken in order to ensure deadlock-freedom, as new channel dependencies may be introduced. Deadlock may result if these new channel dependencies cause the formation of a cycle in the channel dependency graph of the routing function. A number of solutions, such as [33, 37, 39] depend on VCs for deadlock avoidance. Most of the fault-tolerant routing algorithms designed for a specific topology are limited with respect to the combinations of component failures that are supported. Requirements for successful operation may include the shape of faulty regions – such as for [33] (which handles convex faults in mesh topologies) and for [37,39] (which in addition handle some types of non-convex faults). In order to represent one of the supported fault-combinations, healthy switches and communication channels could be turned o [37].

Topology agnostic routing algorithms constitute a category of routing algorithms that do not assume a specific interconnection network topology. Such a routing algorithm can be used for any network topology, and is thus an obvious choice for a network with an irregular topology. Perhaps more importantly, topology agnostic routing algorithms also support fault tolerance in networks with regular topologies. Topology agnosticism is further discussed in Section 2.8.

A vast number of routing algorithms are available in the literature, and Section 2.5.1 provides

an overview of a few important algorithms for mesh and torus topologies (the topologies used in the performance evaluation experiments of this thesis). Section 2.8.1 presents some of the most important topology agnostic routing algorithms. In general, our focus is on the algorithms' approach to deadlock avoidance.

### 2.5.1 Selected algorithms for meshes and tori