# Softcore HDL processor for implementation in FPGA and ASIC

**Bartas Venckus**

Thesis submitted for the degree of Master in Informatics: Nanoelectronics and Robotics 60 credits

Department of Informatics Faculty of mathematics and natural sciences

**UNIVERSITY OF OSLO**

August 2019

# Softcore HDL processor for implementation in FPGA and ASIC

**Bartas Venckus**

© 2019 Bartas Venckus

Softcore HDL processor for implementation in FPGA and ASIC

http://www.duo.uio.no/

Printed: Reprosentralen, University of Oslo

### **Abstract**

The focus of this thesis is on finding a softcore processor that is capable of performing scientific calculations for applications such as the 4DSpace project. The required softcore processor should have an easy and well-documented development process, as well as usefull customization options. The portability of a softcore processor to application-specific integrated circuits (ASIC) is also an important requirement. An open-source LEON3 softcore processor was chosen for this purpose and tested for the multi-needle Langmuir probe (m-NLP) application. The test was conducted with the source code from an m-NLP project, which calculates plasma parameters. LEON3 was configured to meet the time requirements for the m-NLP project. Results for the performance, resource utilization and power consumption of each configurations are presented. The results conclude that a LEON3 configuration with a lite version of a floating-point unit (FPU) is required to meet the set requirements. Estimates for an ASIC implementation of LEON3 demonstrate that LEON3 is a viable option for a softcore processor for the intended use in the 4DSpace project.

### Acknowledgments

I would like to thank my supervisor Joar Martin Østby for the motivation, patience and help throughout my whole master thesis. I also would like to thank my supervisor Philipp Dominik Häfliger for providing me with inspiration for this thesis, and for his guidance during the thesis. A big appreciation goes to some of my fellow students at UiO, for helping me out with particular programming problems faced during this thesis.

### **Nomenclature**

**ADC** Analog-to-Digital Converter

**AHB** Advanced High-Performance Bus

**AMBA** Advanced Microcontroller Bus Architecture

**ARM** Advanced Reduced Instruction-Set Computer Machine

**ASICs** Application-Specific Integrated Circuits

**BCC** Bare-C Cross Compilation

**CFI** Common Flash Interface

**CISC** Complex Instruction-Set Computer

**CLB** Configurable Logic Block

**CLPD** Complex Programmable Logic Device

**CPU** Central Process Unit

**DDR** Double Data Rate

**DMA** Direct Memory Access

**DSP** Digital Signal Processing

**DSU** Debug Support Unit

**ESA** European Space Agency

**FPGA** Field-Programmable Gate Array

**FPU** Floating-Point Unit

**FSL** Fast Simplex Link

**FT** Fault Tolerant

**GP** General Purpose

**GPIO** General-Purpose Input/Output

**GPL** General Public License

**GRFPU** Gaisler Research Floating Point Unit

**GRLIB** Gaisler Research IP Library

**HP** High Performance

**I2C** Inter-Integrated Circuit

IC Integrated Chip

**ICI** Investigation of Cusp Irregularities

**ISA** Instruction-Set Architecture

**LGPL** Lesser General Public License

**LMB** Local Memory Bus

**LRR** Least-Recently Replaced

LRU Least-Recently Used

**LUT** Look-Up Tables

MAC Multiply and Accumulate

MC Minimum Configuration

MCGL Minimum Configuration with GRFPU-Lite

MIPS Microprocessor without Interlocked Pipeline Stages

**m-NLP** Multi-Needle Langmuir Probe

**MPU** Memory Protection Unit

**MWP** Multi-Project Wafer

**P&P** Plug and Play

**PCI** Peripheral Component Interconnect

**PMU** Power Management Unit

**PS** Processor System

**RAM** Random Memory Access

**RISC** Reduced Instruction-Set Computer

**ROM** Read-Only Memory

**SEU** Single-Event Upset

**SIMDs** Single Instructions, Multiple Data

**SMP** Symmetric Multi-Processor

**SoC** System-on-Chip

**SPARC** Scalable Processor Architecture

**TSMC** Taiwan Semiconductor Manufacturing Company

UART Universal Asynchronous Receiver-Transmitter

**UMC** United Microelectronics Corporation

### **Table of Contents**

| 1 | Inti | rodu   | ction                                                       | 1  |

|---|------|--------|-------------------------------------------------------------|----|

|   | 1.1  | Mo     | tivation                                                    | 2  |

|   | 1.2  | Goa    | als                                                         | 3  |

|   | 1.3  | The    | esis Outline                                                | 3  |

| 2 | Da   | ta Ac  | equisition and Signal Processing for Lower Data Rates       | 4  |

|   | 2.1  | Fix    | ed-point vs. Floating-point                                 | 4  |

|   | 2.2  | Fiel   | ld-Programmable Gate Array vs Digital Signal Processors     | 5  |

|   | 2.3  | Sof    | tcore Processor Requirements for 4D Module Application      | 6  |

| 3 | Sof  | ftcore | e Processor                                                 | 8  |

|   | 3.1  | Sys    | stem-on-chip                                                | 8  |

|   | 3.2  | Mic    | croprocessor                                                | 8  |

|   | 3.3  | Sof    | tcore Processor Definition                                  | 9  |

|   | 3.4  | Mic    | croprocessor Architecture and Instruction Set Architecture  | 10 |

|   | 3.4  | .1     | Harvard Architecture                                        | 10 |

|   | 3.4  | .2     | Complex Instruction Set Computer                            | 10 |

|   | 3.4  | .3     | Reduced Instruction Set Computer                            | 10 |

|   | 3.4  | .4     | Advanced RISC Machines                                      | 11 |

|   | 3.4  | .5     | Microprocessor without Interlocked Pipeline Stages          |    |

|   | 3.4  | .6     | Scalable Processor Architecture                             | 11 |

|   | 3.5  | Cor    | mmercial Softcore Processors                                | 12 |

|   | 3.5  | .1     | NIOS II                                                     | 12 |

|   | 3.5  | .2     | MicroBlaze                                                  |    |

|   | 3.5  |        | The MIPS Warrior M-Class M5100                              |    |

|   | 3.6  | •      | en-Source Softcore Processors                               |    |

|   | 3.6  |        | OpenRISC1200                                                |    |

|   | 3.6  |        | The Lattice Semiconductor LM32                              |    |

|   | 3.6  |        | LEON3                                                       |    |

|   | 3.7  |        | mparison                                                    |    |

|   | 3.7  |        | Comparison of MicroBlaze and LEON3(FT)                      |    |

|   | 3.7  |        | Comparison of LEON3, MicroBlaze, OpenRisc1200 and Cortex-MO |    |

|   | 3.8  | Cor    | aclusion to Chapter 3                                       | 22 |

| 4 | LEON3   | B                                                     | 23 |

|---|---------|-------------------------------------------------------|----|

|   | 4.1 The | e Gaisler Research IP Library                         | 23 |

|   | 4.1.1   | LEON3/FT - High-performance SPARC V8 32-bit Processor | 23 |

|   | 4.1.2   | Integer Unit                                          | 23 |

|   | 4.1.3   | The MUL32                                             | 24 |

|   | 4.1.4   | The DIV32                                             | 24 |

|   | 4.1.5   | High-Performance IEEE-754 Floating-point Unit         | 24 |

|   | 4.1.6   | The IEE-754 Floating-Point Lite Unit                  | 25 |

|   | 4.1.7   | Cache Sub-system                                      | 25 |

|   | 4.1.8   | Memory Management Unit                                | 25 |

|   | 4.1.9   | Interrupt Interface                                   | 25 |

|   | 4.1.10  | Advanced Microcontroller Bus Architecture             | 25 |

|   | 4.1.11  | Advanced High-Performance Bus                         | 26 |

|   | 4.1.12  | Advanced Peripheral Bus                               | 26 |

|   | 4.1.13  | The AHB and APB Interfaces, Bridges and Controllers   | 26 |

|   | 4.1.14  | General-purpose I/O Port                              | 27 |

|   | 4.1.15  | The GRLIB Directory Structure                         | 27 |

|   | 4.2 LE  | ON3 Tools                                             | 28 |

|   | 4.2.1   | Cobham Gaisler Monitor                                | 28 |

|   | 4.2.2   | GRMON2                                                | 28 |

|   | 4.2.3   | GRMON 3                                               | 29 |

|   | 4.2.4   | LEON C/C++ IDE for Eclipse                            | 29 |

|   | 4.2.5   | The TSIM                                              | 29 |

|   | 4.2.6   | LEON Bare-C Cross Compilation System                  | 29 |

|   | 4.2.7   | Other Types of Compilers and Toolchains               | 30 |

|   | 4.2.8   | Xconfig                                               | 30 |

|   | 4.2.9   | Online Support                                        | 30 |

| 5 | Implem  | entation                                              | 31 |

|   | 5.1 Hai | dware                                                 | 31 |

|   | 5.1.1   | ZedBoard                                              | 31 |

|   | 5.1.2   | Computer                                              | 32 |

|   | 5.2 Sof | tware                                                 | 32 |

|   | 5.2.1   | Vivado Design Suite 2013.4                            | 32 |

|   | 5.2.2   | Xilinx Microprocessor Debugger 2013.4                       | 33 |

|---|---------|-------------------------------------------------------------|----|

|   | 5.2.3   | Cygwin                                                      | 33 |

|   | 5.2.4   | Cygwin-X                                                    | 33 |

|   | 5.2.5   | GR Tools                                                    | 33 |

|   | 5.3 LE  | ON3 Implementation on ZedBoard                              | 33 |

|   | 5.3.1   | Synthesis                                                   | 34 |

|   | 5.3.2   | Zedboard Programming                                        | 36 |

|   | 5.3.3   | Debugging with GRMON                                        | 36 |

| 6 | LEON:   | 3 Testing                                                   | 37 |

|   | 6.1 The | e 4D Module                                                 | 37 |

|   | 6.2 The | e m-NLP System                                              | 37 |

|   | 6.2.1   | The Microcontroller Unit                                    | 38 |

|   | 6.2.2   | The ARM Cortex-R4F                                          | 38 |

|   | 6.2.3   | The Science Routine                                         | 38 |

|   | 6.3 Tes | st Setup                                                    | 40 |

|   | 6.3.1   | Science Code                                                | 40 |

|   | 6.3.2   | Xconfig Configurations                                      | 41 |

|   | 6.4 LE  | ON3 Configurations                                          | 41 |

|   | 6.4.1   | Minimum Configuration (MC)                                  | 42 |

|   | 6.4.2   | Minimum Configuration with V8 SPARC Instructions (MCV8)     | 43 |

|   | 6.4.3   | Minimum Configuration with GRFPU-Lite (MCGL)                | 44 |

|   | 6.4.4   | Minimum Configuration with GRFPU-Lite and SPARC V8 (MCV8GL) | 44 |

|   | 6.4.5   | Minimum Configuration with GRFPU (MCG)                      | 45 |

|   | 6.4.6   | LEON3 Performance Summary                                   | 45 |

|   | 6.5 Res | source Utilization                                          | 45 |

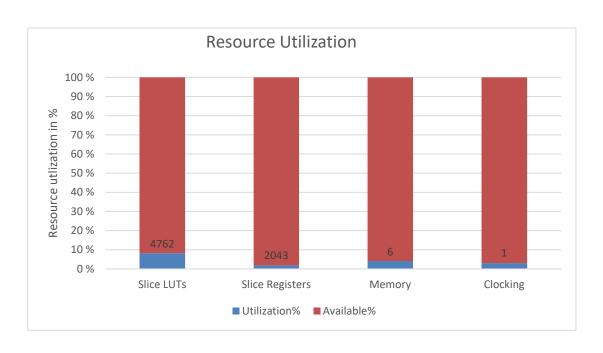

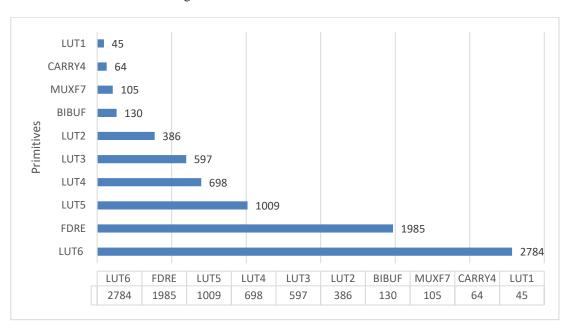

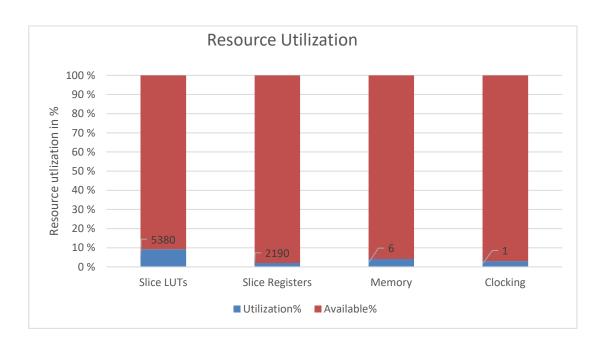

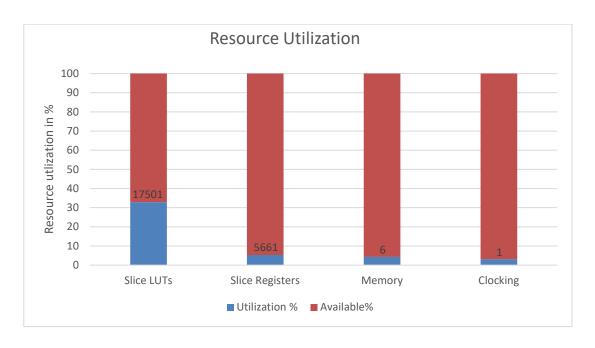

|   | 6.5.1   | Minimum Configuration Resource Utilization                  | 46 |

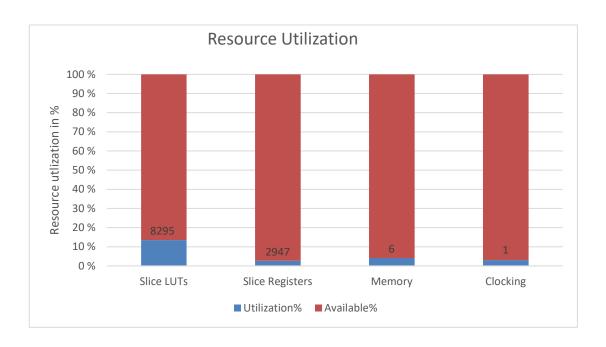

|   | 6.5.2   | Resource Utilization for MCV8                               | 47 |

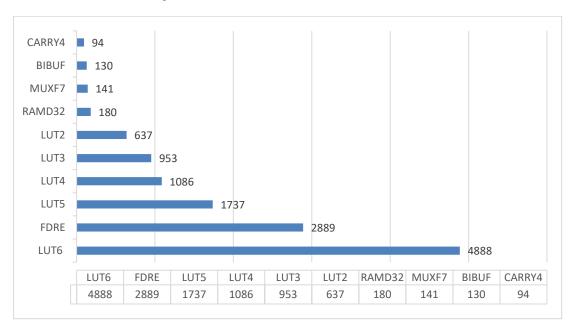

|   | 6.5.3   | Resource Utilization for MCGL                               | 48 |

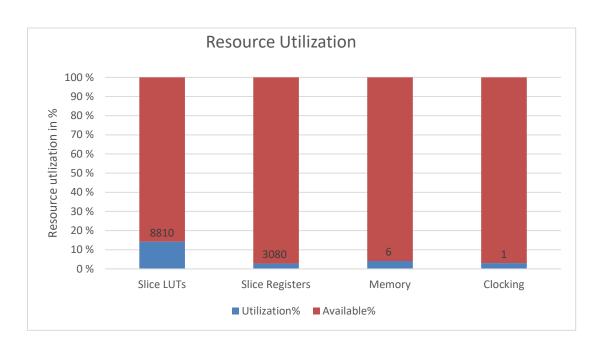

|   | 6.5.4   | Resource Utilization for MCGLV8                             | 49 |

|   | 6.5.5   | Resource Utilization for MCG                                | 50 |

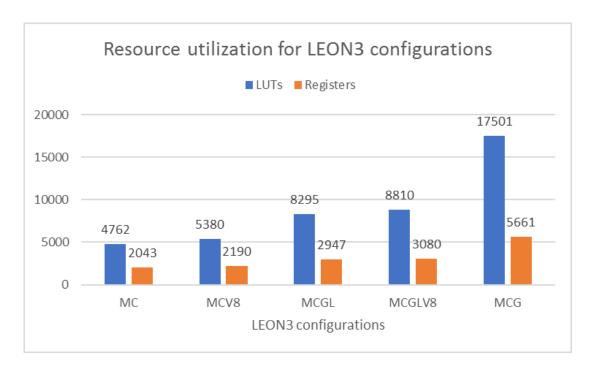

|   | 6.5.6   | Resource Utilization Summary                                | 52 |

|   | 6.6 Po  | wer Consumption Analysis                                    | 53 |

|   | 661     | Minimum Configuration Power Consumption                     | 54 |

|     | 6.6   | .2    | Power Consumption for MCV8                    | . 55 |

|-----|-------|-------|-----------------------------------------------|------|

|     | 6.6   | .3    | Power Consumption for MCGL                    | 56   |

|     | 6.6   | .4    | Power Consumption MCGLV8                      | 57   |

|     | 6.6   | .5    | Power Consumption for MCG                     | 58   |

|     | 6.6   | .6    | Power Consumption Summary                     | .59  |

| 6   | 5.7   | LEC   | DN3 Test Summary                              | 60   |

| 7   | LE    | ON3   | ASIC Implementation                           | 62   |

| 7   | '.1   | ASI   | C Implementation                              | 62   |

| 7   | .2    | LEC   | DN3 ASIC Implementation Estimates             | 62   |

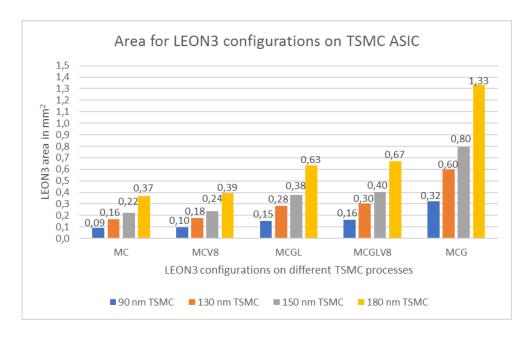

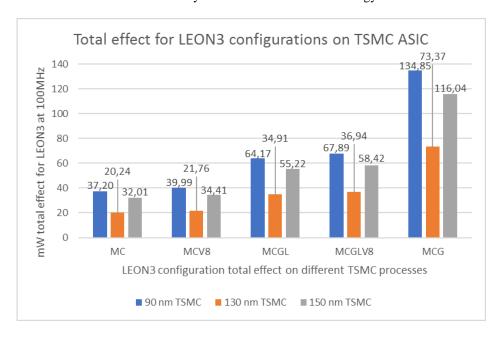

|     | 7.2   | .1    | Taiwan Semiconductor Manufacturing Company    | 63   |

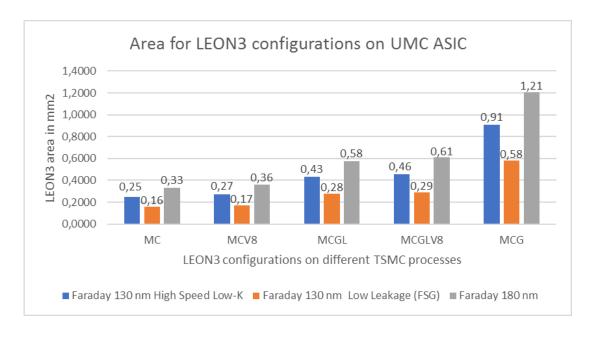

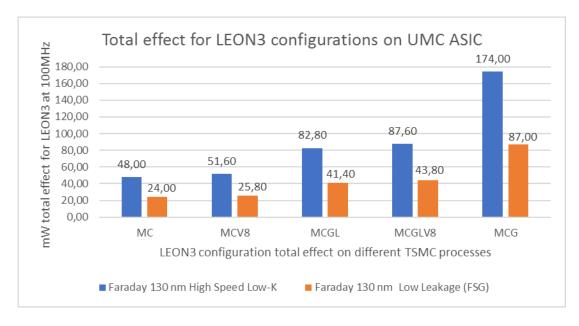

|     | 7.2   | .2    | United Microelectronics Corporation           | 65   |

|     | 7.2   | .3    | X-FAB                                         | 66   |

|     | 7.2   | .4    | Price Estimates for LEON3 ASIC Implementation | 67   |

|     | 7.2   | .5    | Summary                                       | 68   |

| 8   | Co    | nclus | ion                                           | .70  |

| 8   | 3.1   | Futı  | ıre Work                                      | 71   |

| Bib | liogr | aphy  |                                               | .72  |

### List of figures

| Figure 1: NIOS II Processor Core                                              | 12 |

|-------------------------------------------------------------------------------|----|

| Figure 2: Block diagram of MicroBlaze core                                    | 13 |

| Figure 3: Block diagram of M5100                                              | 14 |

| Figure 4: Block Diagram of OpenRISC1200                                       | 15 |

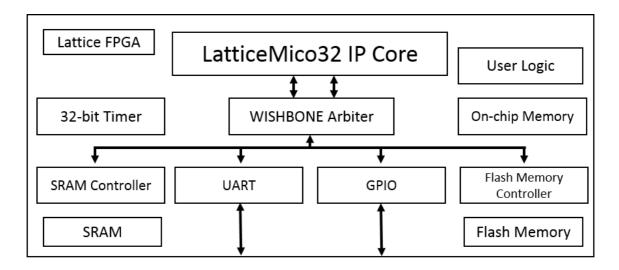

| Figure 5: Block diagram for LatticeMicro 32                                   |    |

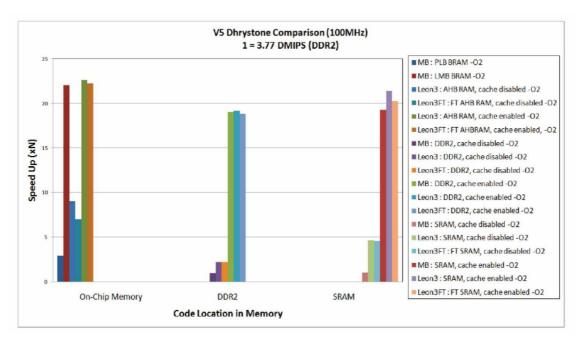

| Figure 6: Virtex-5 Dhrystone comparison                                       | 18 |

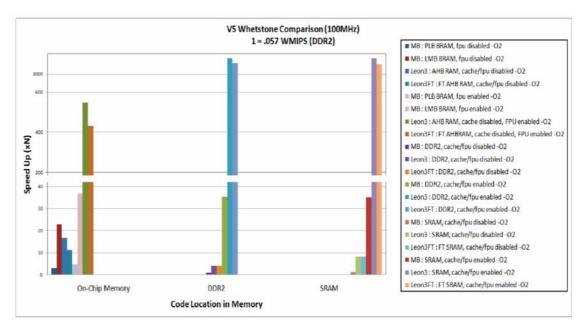

| Figure 7: Virtex-5 Whetstone comparison.                                      | 19 |

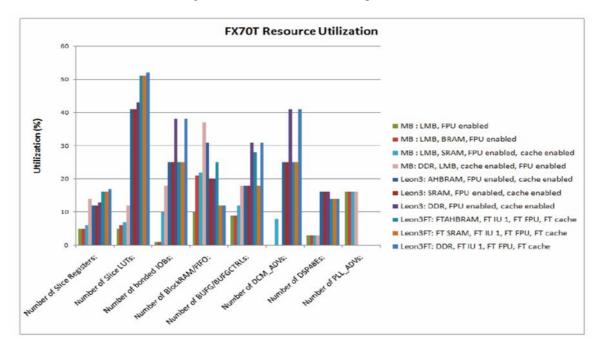

| Figure 8: Processor resource utilization                                      | 19 |

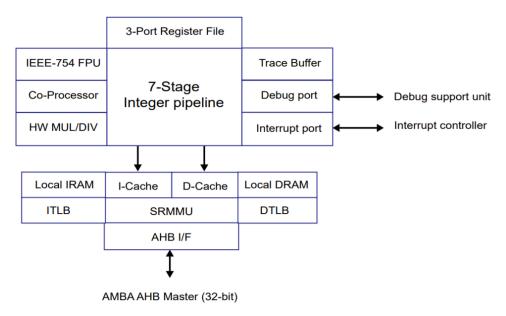

| Figure 9: Block diagram of LEON3                                              | 24 |

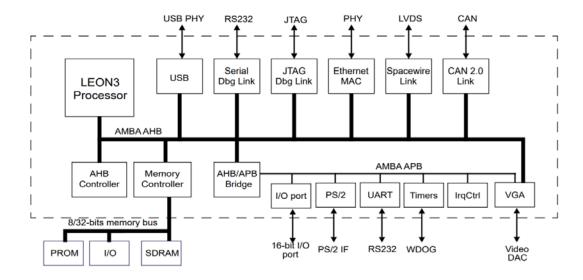

| Figure 10: A typical LEON/GRLIB design centered around one AMBA AHB bus and a |    |

| AMBA APB bus that connects some peripherals cores via an AHB/APB bridge       | 27 |

| Figure 11: LEON3 custom configuration setup with Xconfig                      | 41 |

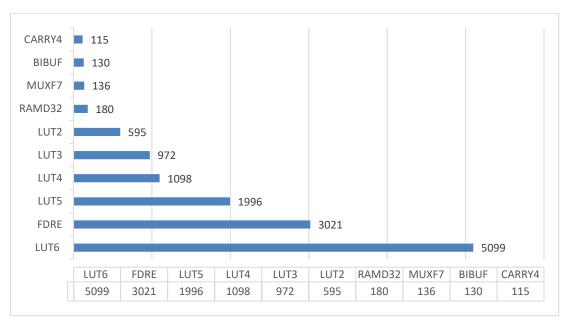

| Figure 12: MC resource utilization                                            | 47 |

| Figure 13: Primitive resource utilization in MC                               | 47 |

| Figure 14: Resource utilization for MCV8                                      | 48 |

| Figure 15: Primitives' resource utilization for MCV8                          | 48 |

| Figure 16: Resource utilization for MCGL                                      | 49 |

| Figure 17: Primitives' utilization for MCGL                                   | 49 |

| Figure 18: resource utilization for MCGLV8                                    | 50 |

| Figure 19: Primitives' utilization for MCGLV8                                 | 50 |

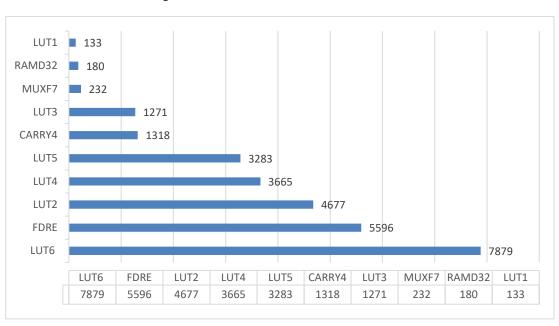

| Figure 20: Resource utilization for MCG                                       | 51 |

| Figure 21: Primitives' utilization for MCG                                    | 51 |

| Figure 22: Resource utilization for LEON3 configurations                      | 52 |

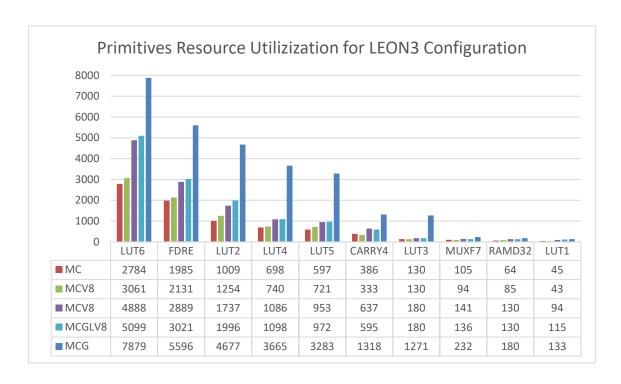

| Figure 23: Primitives' resource utilization for LEON3 configurations          | 53 |

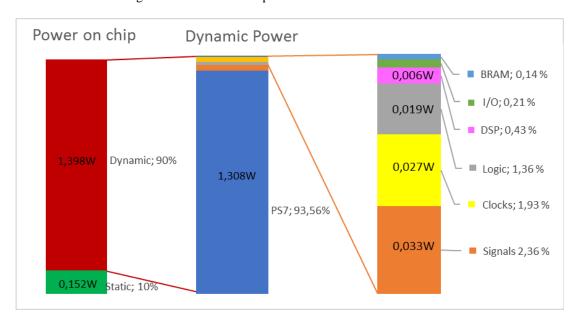

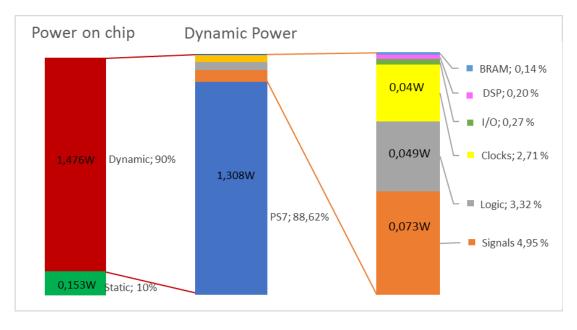

| Figure 24: Minimum configuration power consumption at 100 MHz                 | 54 |

| Figure 25: Minimum configuration power consumption at 160 MHz                 | 55 |

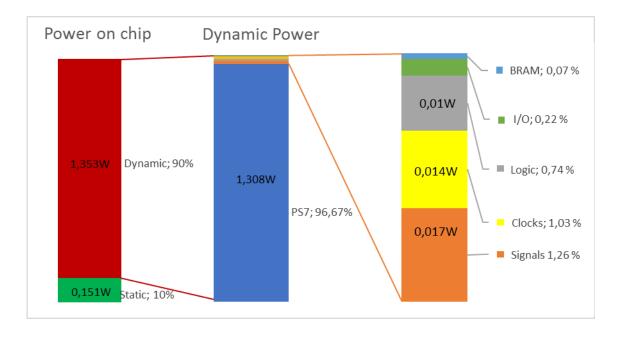

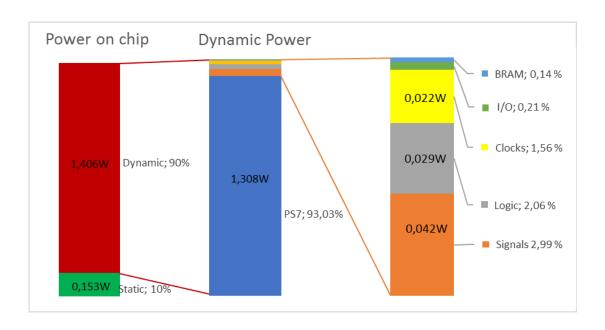

| Figure 26: Power consumption for MCV8 at 100 MHz                              | 56 |

| Figure 27: Power consumption for MCV8 at 160 MHz                              | 56 |

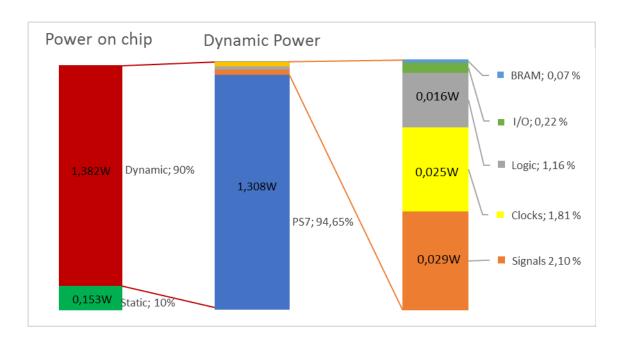

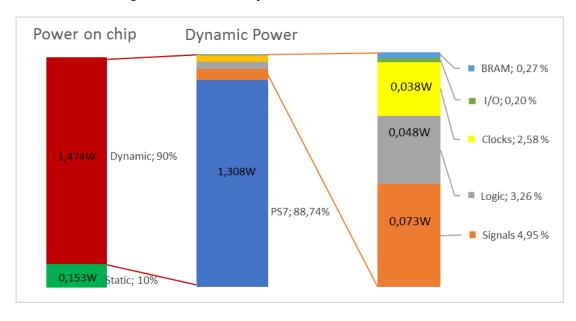

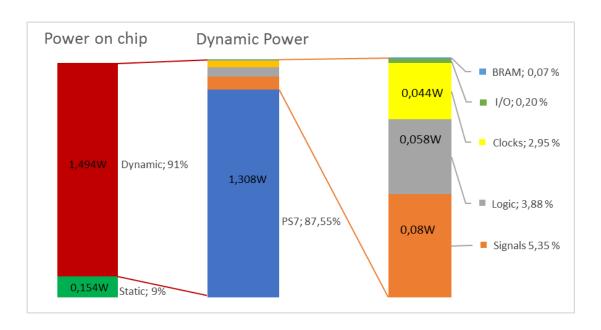

| Figure 28: Power consumption for MCGL at 100 MHz                              | 57 |

| Figure 29: Power consumption for MCGL at 160 MHz                              | 57 |

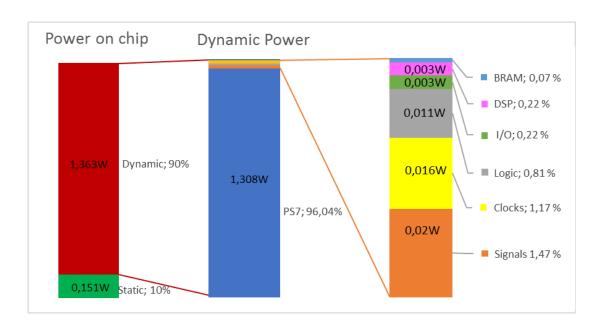

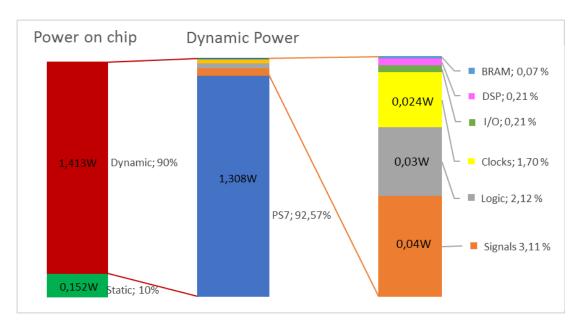

| Figure 30: Power consumption for MCGLV8 at 100 MHz                            | 58 |

| Figure 31: Power consumption for MCGLV8 at 160 MHz                            | 58 |

| Figure 32: Power consumption for MCG at 100 MHz                               | 59 |

| Figure 33: Power consumption for MCG at 160 MHz                               | 59 |

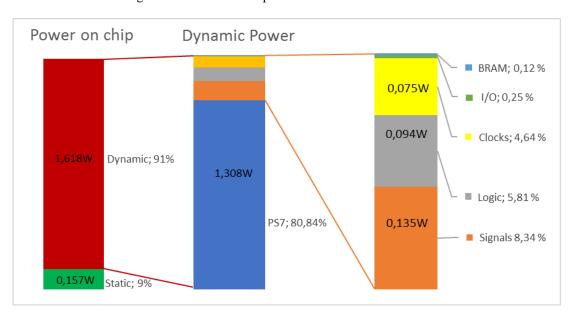

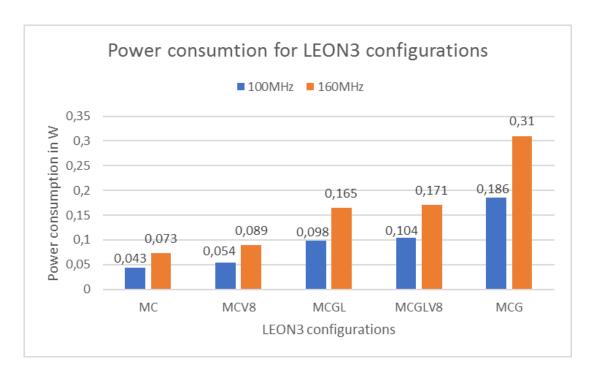

| Figure 34: Power consumption for LEON3 configurations                         | 60 |

| Figure 35: LEON3 configuration area on TSMC ASIC                              | 63 |

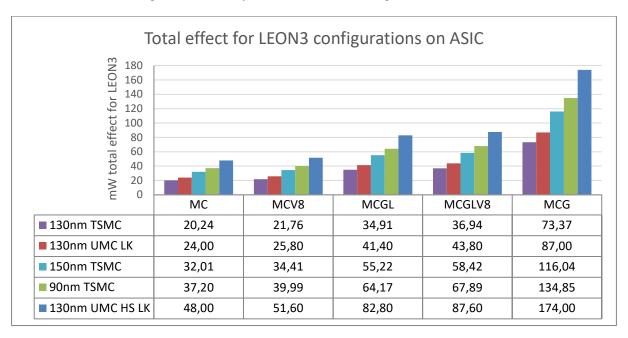

| Figure 36: Total Effect for LEON3 configurations on TSMC ASIC                 | 64 |

| Figure 37: LEON3 configuration area on a UMC ASIC                             | 65 |

| Figure 38: Total Effect for LEON3 configurations on UMC ASIC                  | 66 |

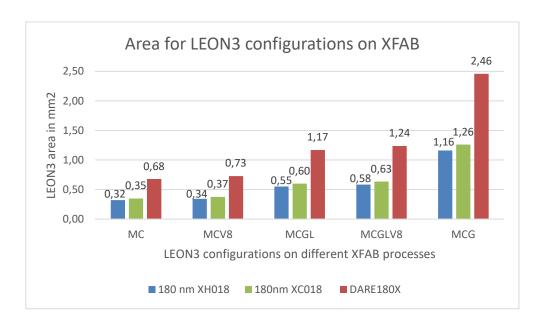

| Figure 39:LEON3 configuration area on a XFAB ASIC                             | 67 |

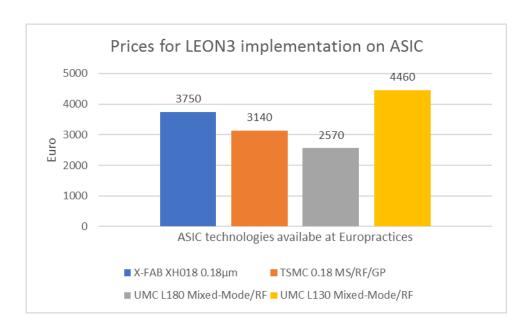

| Figure 40: Prices for LEON3 implementation on different technology processes  | 68 |

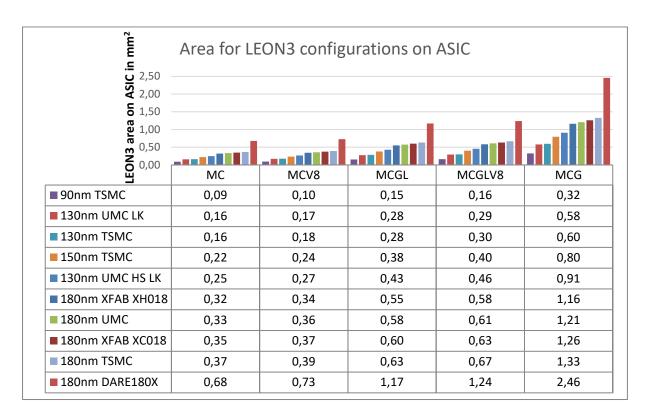

| List of Tables  Table 1: Properties of different DSP implementation technologies                                                                                                                                                  | Figure 41: Summary of area for LEON3 configurations on ASICs                           |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|

| Table 2: Speed and flexibility tradeoffs                                                                                                                                                                                          | List of Tables                                                                         |      |

| Table 3: Feature overview of softcore processors                                                                                                                                                                                  | Table 1: Properties of different DSP implementation technologies                       | 6    |

| Table 4: Highest integer benchmark scores and corresponding designs for each processor implemented in the LX110T                                                                                                                  | Table 2: Speed and flexibility tradeoffs                                               | 9    |

| implemented in the LX110T                                                                                                                                                                                                         | Table 3: Feature overview of softcore processors                                       | . 17 |

| Table 5: Highest floating-point benchmark scores (with FPUs enabled) and corresponding designs for each processor implemented in the LX110T                                                                                       | Table 4: Highest integer benchmark scores and corresponding designs for each processor |      |

| designs for each processor implemented in the LX110T                                                                                                                                                                              | implemented in the LX110T                                                              | . 21 |

| Table 6: Floating-point performance per MHz for each processor (with FPUs enabled) implemented in the LX110T                                                                                                                      | Table 5: Highest floating-point benchmark scores (with FPUs enabled) and corresponding |      |

| implemented in the LX110T                                                                                                                                                                                                         | designs for each processor implemented in the LX110T                                   | . 21 |

| Table 7: Average measured time of the science routine on the 4D module                                                                                                                                                            | Table 6: Floating-point performance per MHz for each processor (with FPUs enabled)     |      |

| Table 8: LEON3 system IP cores                                                                                                                                                                                                    | implemented in the LX110T                                                              | . 21 |

| Table 9: LEON3 minimal configuration times                                                                                                                                                                                        | Table 7: Average measured time of the science routine on the 4D module                 | . 40 |

| Table 10: Configurations for multiplier                                                                                                                                                                                           | Table 8: LEON3 system IP cores                                                         | . 42 |

| Table 11: LEON3 minimum configuration with V8 instructions 2-clock multiplier times43 Table 12: LEON3 minimum configuration with V8 instructions 5-clock multiplier times44 Table 13: Minimum configuration with GRFPU-Lite times | Table 9: LEON3 minimal configuration times                                             | . 43 |

| Table 12: LEON3 minimum configuration with V8 instructions 5-clock multiplier times                                                                                                                                               | Table 10: Configurations for multiplier                                                | . 43 |

| Table 13: Minimum configuration with GRFPU-Lite times44Table 14: Minimum configuration with GRFPU-Lite and SPARC V8 times44Table 15: Minimum configuration with GRFPU times45Table 16: LEON3 test result summary61                | Table 11: LEON3 minimum configuration with V8 instructions 2-clock multiplier times    | . 43 |

| Table 14: Minimum configuration with GRFPU-Lite and SPARC V8 times44Table 15: Minimum configuration with GRFPU times45Table 16: LEON3 test result summary61                                                                       | Table 12: LEON3 minimum configuration with V8 instructions 5-clock multiplier times    | . 44 |

| Table 15: Minimum configuration with GRFPU times                                                                                                                                                                                  | Table 13: Minimum configuration with GRFPU-Lite times                                  | . 44 |

| Table 16: LEON3 test result summary                                                                                                                                                                                               | Table 14: Minimum configuration with GRFPU-Lite and SPARC V8 times                     | . 44 |

| •                                                                                                                                                                                                                                 | Table 15: Minimum configuration with GRFPU times                                       | . 45 |

| Table 17: Gate density and effect for TSMC technology                                                                                                                                                                             |                                                                                        |      |

|                                                                                                                                                                                                                                   | Table 17: Gate density and effect for TSMC technology                                  | . 64 |

### 1 Introduction

The Nanoelectronics Group at the Institute of Informatics (IFI) develops application-specific integrated circuits (ASICs) for application areas such as medical, space, biology, health, and high-quality measurements. The group's intent is to have its own small general processor that could be synthesized on a field programmable gate array (FPGA) and on an ASIC. The softcore processor should be described in hardware description language or very-high-speed integrated circuit hardware language (VHDL).

The departments of Physics, Informatics, and Mathematics at the University of Oslo (UiO) are currently working with the 4DSpace strategic research initiative. The main goal of this initiative is to identify an integrated approach for understanding ionospheric plasma instabilities and turbulence and their role in space weather.

The multi-needle Langmuir probe (m-NLP) project is one part of that integrated approach. An instrument with four needle probes is placed in an Investigation of Cusp Irregularities (ICI) sounding rocket[1] or satellite, where it measures and collects the *in-situ* current from the individual needle probes [2]. On a satellite, for example NORSAT-1, the collected data is converted to voltage, then filtered and digitized. The plasma parameters are then calculated and sent to the central telemetry system for downlink to the ground stations. For a sounding rocket system, the data is collected, processed, and sent to the ground stations without calculating the plasma parameters. This is because of mission time limitations and onboard processing times. In the thesis written by Erik Nobuki Kosaka the possibility of doing plasma parameter calculation on the sub-payloads of the ICI sounding rocket's 4DSpace module was proven to be realistic. Onboard processing is considered because of the bandwidth limitations which does not allow for all of the raw data to be sent to ground.

In this thesis, softcore processor options will be explored and tested for possible use in the m-NLP project. There are many open-source softcore processors that are at different developmental and confirmation stages, as well as many commercial softcores for sale in a broad price range.

### 1.1 Motivation

One of the main reasons for using a softcore processor instead of a hardcore processor is that the development, testing, and redesigning times are exceedingly faster because of a simpler design cycle, a more predictable project cycle, field reprogrammability, rapid prototyping, and a feasibility study.

The advantage of a softcore processor is its simple customizability, processor parts can be added or removed in a relatively short amount of time. A softcore is also advantageous because of the relatively easy portability to ASICs. The test of a softcore processor on an FPGA takes less time because of multiple test patterns can be tested faster on an FPGA board than the protracted simulations for an ASIC design.

When the softcore processor is tailored, tested, and meets the application requirements, it can be ported to ASIC technologies, where it can support higher speeds, lower power consumption, lower or higher temperatures, and more radiation. The latter is possible to counter with mitigation propagation processes of single event upsets (SEUs) and radiation-hardened technology processes. The SEUs are caused by ionized particles that strike a micro-electronic device and can change the state of a logic element. Once ported to an ASIC, a softcore processor will have a lower unit price and a smaller size, and it may include other parts such as random memory access (RAM), microelectromechanical systems (MEMS), an image sensor, and power regulators.

The plasma parameter calculations for the m-NLP project are currently tested with a microcontroller unit (MCU) (TMS570ls1224), which possesses an advanced reduced instruction-set computer machine (ARM) Cortex-R4F central processing unit (CPU). These test results are used in the present thesis as benchmarks to determine wether the chosen softcore processor is capable of performing those calculations within the given time specifications.

The potential future use of the chosen softcore processor in this project is only one of many possible utilizations. Since softcore processors can be tailored to practically any extent, many possibilities exist for their utilization in other projects, both at the physics department and in the Nanoelectronics Group.

### 1.2 Goals

The objective of this thesis can be divided into three different main goals. The first goal is to understand the principles of softcore processors, identify the available softcore processors, analyze and compare them, and then draw a conclusion about which is the most suitable for use in this study. Since a significant amount of in-depth research has already been conducted by other researchers, the analysis and comparison herein are done based on the results reported in those studies.

The second goal of this thesis is to further analyze the chosen processor; describe its features and development tools; implement it on an FPGA; and test it against the Cortex-R4F processor, used in a 4D module, with the science routine for plasma parameter calculations. The third goal of this thesis is to determine the resource utilization, power consumption, and predictions for future implementation of the chosen softcore processor on an ASIC.

### 1.3 Thesis Outline

The remainder of this thesis is outlined as follows: Chapter 2 presents the data acquisition techniques and explains the main differences between hardcore processors, digital signal processors, and softcore processors. Then, Chapter 3 describes what a softcore processor is and discusses the processor architectures. It also presents an overview, analysis, and comparison of different softcore processors. In Chapter 4 in-depth information is provided about the chosen softcore processor and its development tools and Chapter 5 addresses the implementation processes of the chosen softcore processor on an FPGA. Thereafter, Chapter 6 discusses the testing, resource, and power consumption characterization of the softcore processor implementation, and in Chapter 7 the challenges for ASIC implementation of a softcore processor are presented followed by discussion about the rough estimates for its power, area, and price. Finally Chapter 8 concludes this thesis.

# 2 Data Acquisition and Signal Processing for Lower Data Rates

Most of the sensor data acquisition and digital signal processing (DSP) can be done using simple CPUs with specific techniques. Those techniques and possible CPU solutions are discussed in this chapter.

### 2.1 Fixed-point vs. Floating-point

Digital signal processing can be categorized as: fixed-point DSP or floating-point DSP. This essentially means that the processing is conducted with positive and negative whole numbers for fixed-point DSP via minimum bits, yielding  $2^{16}$  (65,536) bit patterns. In contrast, floating-point DSP uses rational numbers via a minimum of 32 bits, which leads to  $2^{32}$  bit patterns, where both large and small numbers can be represented. The latter is mostly used for a dynamic range, in which large data sets need to be processed and where they can also be unpredictable.

Floating-point DSP units cost more area and power than fixed-point DSP units. It is easier to develop a floating-point algorithm than a fixed-point algorithm, since the latter requires greater manipulation to quantize noise. Greater performance efficiency can be achieved with a fixed-point processor, since it uses less area and consumes less power than a floating-point processor for the task that must be accomplished [3].

For the IFI's Nanoelectronics group applications that require the use of a processor, the fixed-point calculations are the primary choice. However, the possible applications of floating-point calculations are still considered as options for some projects and is covered in this thesis.

## 2.2 Field-Programmable Gate Array vs Digital Signal Processors

With the recent advances in FPGA technology, VHDL development, and testing tools, a designer can implement complex integrated functionality on a single die. This can be further extended to a complete microcomputer system. An FPGA consists of three main components: logic blocks, I/O blocks, and interconnection wires. Logic blocks are composed of several inputs and one output, look-up-tables (LUT), small RAM, flip-flops (FFs), and special arithmetic logic support. These programmable blocks are connected with wires and programmable switches used to set up desired connections between the logic blocks [4, p. 100].

The development life-cycle of an FPGA technology processor-based system can be significantly reduced by providing the ability to incorporate several digital cores as reconfigurable, embedded processors in a single die. Using an FPGA approach to implement a DSP processor can drastically reduce the time to market compared to ICs or ASICs. An FPGA's flexibility reduces the long design time associated with ASICs, so that the delay in prototyping can be eliminated with FPGAs. By an using FPGA as one of the platforms for ASIC prototyping and testing, the development and verification of an ASIC processor can be achieved rapidly.

Field programming allows one to bridge flexibility and performance gaps between general-purpose processors and ASICs. Hardcore DSP processors can be programmed with software; however, their architecture is not flexible, since they are constrained by factory settings such as bus width, certain numbers of multiply and accumulate (MAC) blocks, and limited data widths. Field-programmable gate arrays can provide complete hardware customization for any DSP application requirement; they have been used in many DSP embedded systems, and some comparisons of different DSP implementation technologies are represented in Table 1 [5, p. 5].

| Feature                 | ASIC                             | Structured<br>ASIC               | FPGA                            | Reconfigura<br>ble<br>Hybrid | DSP<br>processor            | General-<br>purpose µP      |

|-------------------------|----------------------------------|----------------------------------|---------------------------------|------------------------------|-----------------------------|-----------------------------|

| Operating freq. (MHz)   | > 1,000                          | > 1,000                          | 100–400                         | 50–300                       | 100–60                      | 100-1,000                   |

| Power consumption       | Moderate                         | Moderate                         | High                            | Moderate                     | Very High                   | Very High                   |

| Parallel execution      | Maximum                          | Maximum                          | Maximum (flexible)              | Moderate                     | Serial (ILP)                | Serial<br>(no spec.<br>FUs) |

| Complexity of design    | Very high<br>(50–100-M<br>gates) | Very high                        | Very high                       | Moderate                     | Very<br>complex<br>programs | Very<br>complex<br>programs |

| Size/are                | Large                            | Large                            | Very Large                      | Moderate to high             | Moderate to high            | Moderate to high            |

| Migration/<br>evolution | None                             | Low                              | Very high                       | Moderate to high             | High (performance limited)  | High (performance limited)  |

| Customizati on          | Difficult                        | Moderate                         | Easy                            | Easy to moderate             | Easy                        | Easy                        |

| Design<br>verification  | Very difficult                   | Moderate                         | Moderate                        | Moderate to difficult        | Moderate                    | Moderate                    |

| Design tools            | Good, very expensive             | Good,<br>moderately<br>expensive | Very good,<br>less<br>expensive | Very poor                    | Good, inexpensive           | Very good, inexpensive      |

Table 1: Properties of different DSP implementation technologies

An FPGA permits the simultaneous execution of the algorithm's subfunctions. The FPGA can outperform a DSP processor by as much as 1,000:1, although it depends on, for example, clock rates and the degree of parallelism. The typical gains lie between 10:1 and 1,000:1 [6].

In conclusion, an FPGA provides faster development cycle than that of an ASIC or DSP processor, reconfigurability, embedded resources integration, and the development tool efficiency as well as device cost. All these advantages come at the cost of a higher power consumption and higher per-unit cost when compared to other ASIC processors, which can be addressed by porting a VHDL softcore processor design into an ASIC.

## 2.3 Softcore Processor Requirements for 4D Module Application

Current 4Dspace modules use a Cortex-R4F processor. Considering it as the baseline for softcore processors, some basic requirements can be outlined.

The first requirement is an integer and floating-point performance. A softcore processor should be able to perform, to a certain degree, as well as the hardcore processor. The leeway here is because a softcore implementation on an FPGA will always perform slower than an equal implementation on an ASIC or than a dedicated hardcore processor.

The second requirement is a broad spectrum of alternatives for communication interfaces. These alternatives should support basic interfaces such as Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I2C), Universal Asynchronous Receiver-Transmitter (UART) among others. These interfaces are necessary for an easy integration of the chosen softcore processor in the existing 4D module.

The third criteria for the softcore processor are power consumption and area. These should be within reasonable numbers, which were abstracted after consultation with the Nanoelectronics group and physics department.

The fourth requirement is a possibility to configure the softcore processor against SEUs, which are caused by hard radiation. The SEU mitigation is mostly considered for the use of a softcore processor in 4DSpace modules placed on satellites, where it is exposed to hard radiation over a prolonged mission time.

### **3 Softcore Processor**

In this chapter, necessary information is presented to provide an understanding and definition of a softcore processor. An overview of different processor architectures and their roles is also presented. Three commercial and three open-source softcore processor are presented and explained, and five of them are compared against each other based on multiple study results. Finally, the most suited softcore processor is chosen as the main contender based on multiple aspects and criteria set earlier in this thesis.

### 3.1 System-on-chip

A system-on-chip (SoC) is a system containing multiple computer components or non-computational components in a single, integrated chip (IC). In contrast to a circuit board, where components are assembled on-to it, an SoC fabricates the components into one unit. Most SoCs include components such as CPU and system memory like RAM or read-only-memory (ROM) [7, p. 1]. An SoC may also include, but may not be limited to the following:

- Real-time clocks, counters and timers.

- Digital Signal Processor

- External interfaces such as USB, Ethernet, or SPI

- Radio frequency (RF) interfaces

- Analog frontends towards sensors

### 3.2 Microprocessor

A microprocessor ( $\mu P$ ) is the CPU of a single IC or at most a few integrated circuits. A  $\mu P$  works mostly in the same way as a CPU does, where it is driven by clocks, which are based on registers where it accepts binary data as an input and processes it according to instructions stored in its memory.

The main difference is that integrating a whole CPU onto single or a few ICs greatly reduces the cost of the processing power, and the price of a  $\mu P$  is lower than that of a CPU, since the former is produced in high numbers by highly automated processes.

Microprocessors are also used in many applications that are not computation related: mostly control systems. A  $\mu P$  in an embedded system controls and processes sensor inputs and outputs as well as other related processes.

### 3.3 Softcore Processor Definition

A soft  $\mu P$  or a softcore processor is a  $\mu P$  core that is described in an HDL and is implemented in an FPGA, an ASIC, or a complex programmable logic device (CPLD). Since most of softcores on FPGA have low gate utilization and rely on memory technology and LUTs, FPGAs tend to have higher power usage. This can be fixed by porting them to ASIC.

The FPGA implementation also causes lower speeds than compared to hardcore processors, the typical softcore processor has speeds from 200MHz up to 500MHz, whereas a hardcore processor will have speeds anywhere from 100MHz up to 4GHz. This is often addressed by the use of multi-softcore processors and parallel programming. Table 2 [8, p. 4] presents an overview of flexibility and speed tradeoffs for processors in different technologies; the flexibility decreases from the ASIC down to generic technology, while the speed increases from generic up to ASIC technology.

|                | Technology                                 | Performance/<br>Cost | Time until<br>running | Time to high performance | Time to change code functionality |                      |

|----------------|--------------------------------------------|----------------------|-----------------------|--------------------------|-----------------------------------|----------------------|

|                | ASIC                                       | Very High            | Very Long             | Very Long                | Impossible                        | F                    |

| Speed increase | Custom<br>Processor or<br>DSP<br>Processor | Medium               | Long                  | Long                     | Long                              | Flexibility decrease |

| Spee           | FPGA                                       | Low to<br>Medium     | Short                 | Short                    | Short                             | ecrease              |

|                | Generic                                    | Low to<br>Medium     | Short                 | Not Attainable           | Short                             |                      |

Table 2: Speed and flexibility tradeoffs

## 3.4 Microprocessor Architecture and Instruction Set Architecture

This section covers the necessary background for a  $\mu P$  architecture and instruction-set architecture. A number of different  $\mu P$  architecture types are available; the most used types for both softcore and hardcore  $\mu P$  are described in this section.

#### 3.4.1 Harvard Architecture

The Harvard architecture is a computer architecture that stores machine instructions and data in separate memory units that are connected by different buses. This architecture allows a processor to run a program and access data independently and therefore simultaneously.

### 3.4.2 Complex Instruction Set Computer

Complex instruction set computer (CISC) [9, p. 39] is a computer architecture family that incorporates multi-clock complex instructions where one instruction can execute several low-level operations. These operations include loading and storing from or to memory and arithmetic operations. Most of the later instruction sets evolved from CISCs.

### 3.4.3 Reduced Instruction Set Computer

A RISC [10, p. 11] is a type of  $\mu P$  architecture that was optimized from CISCs, where it shifted the analytical process of a computational task from the execution (run-time) to the preparation (compile time). The optimization allows a RISC to have much lower cycles per instruction than a CISC. A RISC generally utilizes a small, highly-optimized set of instructions, rather than a more specialized set of instructions often found in other types of architectures. This does not mean that it has a small amount of instructions; later versions of RISCs have a larger instruction set than most CISC CPUs. Furthermore, a RISC is a forerunner for the major architectures today, such as ARC, ARM, Atmel AVR, MIPS, RISC-V, SuperH and SPARC, some of which are discussed below.

### 3.4.4 Advanced RISC Machines

An advanced RISC Machine (ARM) is a RISC type of  $\mu P$ , that has been enhanced with an optimized instruction set and pathways, thereby requiring fewer transistors; this enables a smaller die size for IC and lower power consumption then the other type of RISC  $\mu P$ . The ARM processor's smaller size, reduced complexity and lower power consumption make it suitable for increasingly miniaturized devices. The processors of ARMs possess the same features as a RISC, (load/store architecture, single-cycle execution), which includes but is not limited to an orthogonal instruction set and an enhanced power-saving design [11, p. 2].

### 3.4.5 Microprocessor without Interlocked Pipeline Stages

A Microprocessor without Interlocked Pipeline Stages (MIPS) is a RISC-type  $\mu P$  architecture based on a 34/64-bit instruction set, and it uses a load/store data model, which is also known as register-register architecture. The architecture is streamlined to support the optimized execution of high-level languages. To further increase efficiency of instructions processing, MIPSs use a technique called pipelining, and since all instructions are 32 bits long, these  $\mu P$  simplify the accessing and decoding instructions [12].

The MIPS is now well developed, tested, and used in many devices around the world. It is a prime architecture for becoming acquainted with how CPUs work, and the guides and support for this architecture are numerous.

#### 3.4.6 Scalable Processor Architecture

Scalable processor architecture (SPARC) [13] is heavily based on early RISC processors (I and II), with minimal operation codes and instruction execution rate at almost one instruction per clock cycle. This makes it a similar architecture to that of MIPS, although it lacks instructions like multiply and divide in the early versions. One primary feature of SPARC is that it is a scalable processor that is implemented with the use of 3 to 32 register windows. By implementing a chosen number of windows, there is a possibility to have maximum call-stack efficiency or reduced cost and complexity if needed.

### 3.5 Commercial Softcore Processors

Various commercial softcore processors exist. However, in this section only, the most popular ones are discussed.

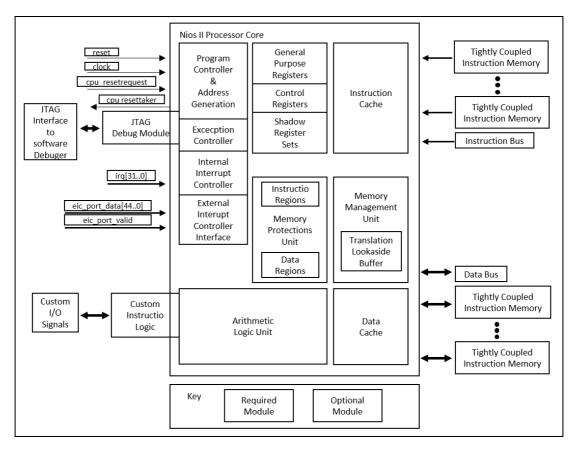

### 3.5.1 **NIOS II**

The NIOS II processor [14] is Altera Corporation's flagship softcore general purpose RISC processor; it features a Harvard memory architecture and is one of the most widely used softcore processors in the FPGA industry. The processor features a 32-bit ISA, 32 general-purpose registers, single-instruction 32x32 multiply and divide operations, and dedicated instructions for 64-bit and 128-bit products of multiplication. NIOS II comes in three versions: economy, standard, and fast. Each core varies in size, register, and pipeline number, and it is possible to scale them for the desired performance, logic number, and power usage. Figure 1 [15, p. 10] illustrates a the standard NIOS II softcore processor block diagram.

Figure 1: NIOS II Processor Core

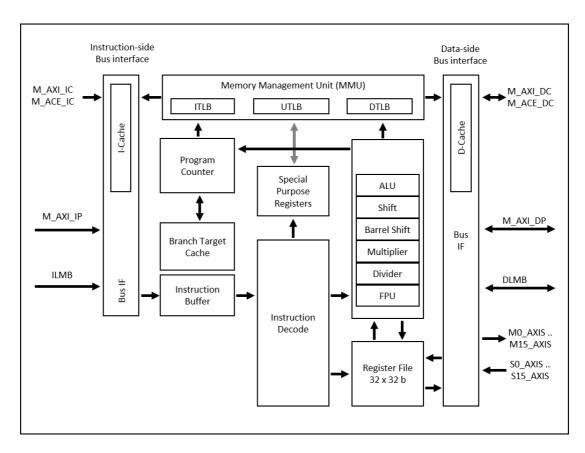

### 3.5.2 MicroBlaze

MicroBlaze [16] is a 32-bit Harvard architecture softcore processor developed by Xilinx. It possesses 32 fixed 32-bit general-purpose registers, a 32-bit instruction word with three operands and two addressing modes, and a 32-bit bus. It also has optional 3 to 5 pipeline depths, a hardware divider, a barrel shifter, and debug logic, as well as a floating-point unit (FPU) and the local memory bus (LMB). The fast simplex link (FSL) interface allows it to include up to eight dedicated, 32-bit input and output ports. MicroBlaze targets Virtex and Spartan families of FPGAs. Figure 2 [17, p. 7] depicts a MicroBlaze core block diagram with fixed and optional features.

Figure 2: Block diagram of MicroBlaze core

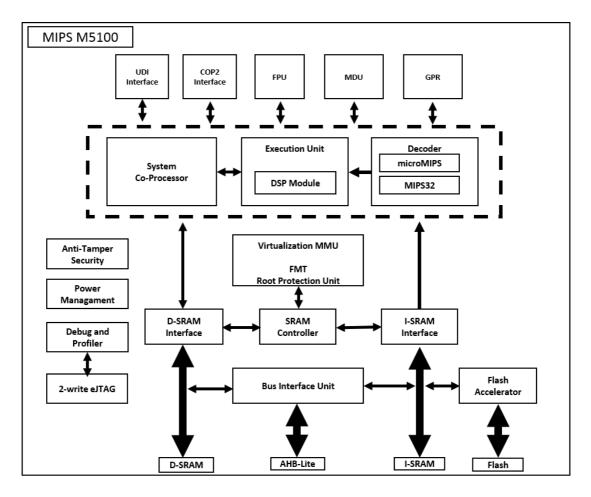

### 3.5.3 The MIPS Warrior M-Class M5100

The M5100 [18] is a relatively new 32-bit MIPS softcore processor developed by Imagination Technologies; it features state-of-the art power reduction and management, fast interrupt handling, an advanced debug or profile, and total hardware virtualization. The processor implements over 150 instructions, including 70 single instructions and multiple data (SIMD) and 38 multiply or MAC instructions, as well as a seven-stage pipeline, an FPU, and

a memory controller. Figure 3 [18] illustrates an M5100 softcore processor block diagram with included and optional features.

Figure 3: Block diagram of M5100

### 3.6 Open-Source Softcore Processors

A surprising number of open-source softcore processors exist. Since 1999 the open-source project called OpenCores [19] has published, collaborated, and shared almost 200 different softcore processors under the following licenses: The GNU General Public License (GPL), the Berkeley Software Distribution (BSD) license, and the GNU Lesser General Public License (LGPL) licenses. Although the number of softcore processors available at OpenCores is impressive, only a few are complete designs that have been tested on different FPGAs. Furthermore, not all projects provide the source code files, which made it difficult to study and understand them. Couple of the major ones, which have been utilized and developed by small groups as well as large organizations such as the European Space Agency (ESA) are discussed in the next subsection.

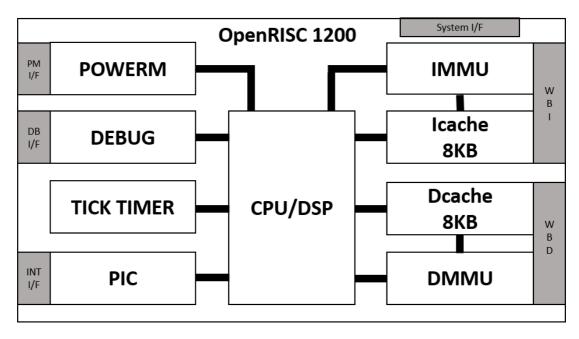

### 3.6.1 OpenRISC1200

OpenRISC1200 (OR1200) [20] comprises one of the most well-known and popular 32-bit and 64-bit RISC softcore processors found at the Open Core page. It features a five-stage pipeline, a virtual memory support memory management uinit (MMU), a power management unit (PMU), and an interrupt handler. Supplemental facilities include a debug unit for real-time debugging, a high-resolution tick timer, a hardware multiplier, and a divider available with the right configuration. Flextronics have also turned the processor design into an ASIC by Flextronics. The OR1200 is intended for embedded, portable, and networking applications. Figure 4 [21, p. 3] presents an OR1200 core block diagram.

Figure 4: Block Diagram of OpenRISC1200

#### 3.6.2 The Lattice Semiconductor LM32

The LM32 [22], similarly to most other processors described in this essay, is a 32-bit RISC Harvard architecture softcore processor with 32 32-bit general-purpose registers. It features a six-stage pipeline, with register-register arithmetic operations, although it does not possess an FPU. Three configurations are available to optimize area and performance, and several peripheral components might be integrated, for example memory controllers: parallel flash, DDR, DDR2, I/O DMA controller, and UART, among many others. Figure 5 [22] illustrates an LM32 block diagram.

Figure 5: Block diagram for LatticeMicro 32

### 3.6.3 **LEON3**

LEON3 [23] is a 32-bit SPARC-V8 open-source softcore processor developed by Cobham Gaisler. An early version of the LEON processor was developed by the ESA and was targeted to eliminate SEUs caused by hard radiation. The LEON2 fault tolerant (FT) version was created and used in many satellites, including the Intermediate eXperimental Vehicle (IXV) [24]. Later versions were contracted to Cobham Gaisler, where LEON3, LEON3-FT, LEON4 and LEON4-FT have been developed. The latter is one most powerful 64-bit softcore processors in the world. LEON3 features a seven-stage pipeline, a hardware multiplier, divider and MAC units, as well as an FPU, an MMU, symmetric multi-processor support (SMP), and power management capabilities. Both LEON4 and LEON4-FT are commercial softcore processors.

### 3.7 Comparison

The research on the processors portrayed in this chapter are found online. All of the benchmarks rely on research and articles done by several different entities. This might cause inconsistencies in test conditions, so the portrayed data in the benchmarks can only be used to form a basic understanding of the relations between the processors in question. Any further assumptions are confirmed with coinciding data from multiple researches. The final choice of softcore processor will mostly depend on specifications, appliances, community, support, and

the documentation around it. Nevertheless, some benchmarks are included to understand softcore processor performances. Table 3 lists the features of both the commercial and open-source softcore processors, only the most promising and best-documented processors are listed.

| Feature                 | NIOS II/f                                      | MicroBlaze                                  | OpenRISCSC<br>1200                              | LEON3                                                | M5100                                  |

|-------------------------|------------------------------------------------|---------------------------------------------|-------------------------------------------------|------------------------------------------------------|----------------------------------------|

| License                 | Altera IP core                                 | Ships with<br>Xilinx EDK                    | GNU<br>LGPL                                     | GNU LGPL                                             |                                        |

| Platform                | Altera FPGA,<br>ASIC                           | Xilinx FPGA                                 | FPGA,<br>ASIC                                   | FPGA, ASIC                                           | FPGA                                   |

| Architecture            | 32-bit RISC                                    | 32-bit RISC                                 | 32-bit RISC                                     | 32-bit RISC                                          | 32-bit MIPS                            |

| ISA                     | NIOS II-ISA                                    | MicroBlaze ISA                              | ORBIS32                                         | SPARC V-8                                            | MIPS32 Enhanced                        |

| Custom instructions     | Yes                                            | Yes                                         | Yes                                             | Yes                                                  | Yes                                    |

| Pipeline stages         | 6                                              | 3-5                                         | 5                                               | 7                                                    | 5                                      |

| Register file           | Flat                                           | Flat                                        | Flat                                            | Window                                               | Flat                                   |

| Nr. of global registers | 32                                             | 32                                          | 32                                              | 32                                                   | 32                                     |

| FPU support             | Yes                                            | Yes                                         | Yes                                             | Yes                                                  | Yes                                    |

| MMU                     | Yes                                            | Yes                                         | Yes                                             | Yes                                                  | Yes                                    |

| Mac                     | Yes                                            | N/A                                         | Yes                                             | Yes                                                  | Yes                                    |

| Cache hierarchy         | Harvard                                        | Harvard                                     | Harvard                                         | Harvard                                              | SRAM interface                         |

| Instruction cache size  | 512B to 64KB                                   | 64B to 64KB                                 | 512B to 8 KB                                    | 1B to 2MB                                            | N/A                                    |

| System interface        | Ethernet, JTAG,<br>RS232, SPI, PCI             | LMB, IBM<br>OPB, FSL,<br>PLB, ICL, XCL      | Wishbone<br>SoC rev. B<br>32-bit                | AMBA AHB,<br>RS232, JTAG,<br>PHY, LVDS,<br>CAN, UART | AMBA 3 AHB,<br>AMBA lite,<br>JTAG, UDI |

| Power management        | N/A                                            | Sleep mode                                  | Slow and idle<br>mode, sleep mode,<br>doze mode | Power down and idle mode.                            | Power down.                            |

| Memory interfaces       | SRAM,<br>SDRAM,<br>Flash, Memory<br>mapped I/O | DDR SDRAM,<br>SDRAM, SRAM<br>External Flash | SDRAM,<br>SRAM,<br>SSRAM,<br>FLASH              | SDRAM,<br>SRAM, PROM<br>Memory<br>mapped I/O         | SRAM, ISRAM,<br>DSRAM, FLASH           |

Table 3: Feature overview of softcore processors

### 3.7.1 Comparison of MicroBlaze and LEON3(FT)

In "The Evaluation of Soft-Core Processors on a Xilinx Virtex-5 Field Programmable Gate Array" [25], Mark W. Learn compared the MicroBlaze, LEON3, and LEON3FT softcore processors. All figures and diagrams shown in this section were taken from Learn's evaluation, and two performance benchmark applications were used to evaluate the different softcore processors. The first one was the Dhrystone benchmark, and the second was the Whetstone benchmark.

The Dhrystone [26, p. 4] is a synthetic general-performance benchmark developed by Reinhold P. Weicker in 1984. This benchmark contains no floating-point operations and is

intended to be representative of integer programming; furthermore, it is heavily influenced by hardware and software design. The output from the Dhrystone benchmark is the number of iterations of the main code loop per second, most commonly referred to as Dhrystone million instructions per second (DMIPS).

The Whetstone [26, p. 6] is a synthetic benchmark designed to measure the behavior of scientific programs. This benchmark test attempts to measure the speed and efficiency at which a computer performs floating-point operations. The output is usually given in units called kilo Whetstone instructions per second (KWIPS); however, in this thesis, it will be referred to as million Whetstone instructions per second or (MWIPS).

The results clearly demonstrated that all three processors were greatly improvement with an FPU enabled, although the utilized resources were higher than the without an FPU but still tolerable. With a cache and FPU enabled, the MicroBlaze performance increased by a factor of 40, while LEON3 increased its performance by a staggering factor of between 400 and 1,000. Without the FPU and cache, both processors utilized similar amounts of resources; Figure 6 [25, p. 24] and Figure 7 [25, p. 25] depict these results. LEON3 saw a larger increase in resource utilization in comparison to MicroBlaze once FPU was enabled as seen in Figure 8 [25, p. 26]. This larger increase accounts for the large performance increase when running the Whetstone benchmark test. It should be noted that the MicroBlaze softcore FPU unit can only perform single-precision, floating-point operations, where-as the LEON3 FPU provides the ability to use both single and double-precision floating-point operations.

Figure 6: Virtex-5 Dhrystone comparison

Figure 7: Virtex-5 Whetstone comparison.

Figure 8: Processor resource utilization

# 3.7.2 Comparison of LEON3, MicroBlaze, OpenRisc1200 and Cortex-MO

In "An Evaluation of Soft Processors as a Reliable Computing Platform" [27] by Michael Robert Gardiner, LEON3, MicroBlaze, OpeRisc1200, and Cortex-MO were tested and benchmarked against themselves and the radiation hardened processor RAD750. The tests in this evaluation were performed on two FPGA boards, the first one being LX110T [28], which is a generic Xilinx FPGA board, and the second being Virtex-5QV [29], which is a space grade FPGA board. The results demonstrated in the current thesis concentrate on the LX110T board.

The Gardiner's study used multiple benchmarks to determine the performance of the softcores. The benchmarks used in that study are the standard Whetstone and Dhrystone benchmarks; the CoreMark [30]; and ones such as basicmath, bitcount, dijsktra, fft and stringsearch from the MiBench suit [31]. For the purpose of this research, the results taken from Gardiner's study focus on the Whetstone and Dhrystone benchmarks; however, data from the rest of benchmarks are also displayed.

Although the study came to many interesting conclusions, only the benchmarks for softcores with enabled and disabled FPUs are discussed next. As concluded earlier, on the one hand, MicroBlaze has better integer performance than LEON3. This is also true when compared to the other two softcores, as indicated in Table 4 [27, p. 57]. On the other hand, LEON3 mostly outperforms other processors on the floating-point performance. As mentioned in the previous subsection, the LEON3 FPU has the capacity to perform double-precision, floating-point operations; this is reflected well in Table 5 [27, p. 62]. The MicroBlaze softcore processor performed over 10 times worse than LEON3 in the double-precision, Whetstone benchmark, but it performed better at single-precision Whetstone benchmark by a factor of less than two. In Table 6 [27, p. 64] the LEON3 demonstrates the best performance-scaling with frequency, and MicroBlaze coming in second.

|              |       | MicroBlaze |        | LEON3  |        | Cortex-M0<br>DesignStart | OpenRl | SC 1200 |

|--------------|-------|------------|--------|--------|--------|--------------------------|--------|---------|

| Benchmark    | Units | Design     | Score  | Design | Score  | Score (CB0)              | Design | Score   |

| Dhrystone    | DMIPS | MB0        | 192.22 | LB16   | 76.23  | 73.94                    | OB16   | 44.56   |

| CoreMark     | CM    | MB0        | 225.79 | LB16   | 122.43 | 92.81                    | OB16   | 92.65   |

| bitcount     | BPS   | MB0        | 3.20   | LB64   | 1.14   | N/A                      | OB16   | 0.77    |

| dijkstra     | BPS   | MB0        | 1.07   | LB64   | 0.53   | 0.46                     | OB16   | 0.30    |

| qsort        | BPS   | MB0        | 642.17 | LB64   | 295.73 | 148.94                   | OB16   | 140.30  |

| stringsearch | BPS   | MB0        | 52.96  | LB64   | 30.66  | 24.06                    | OB16   | 14.94   |

Table 4: Highest integer benchmark scores and corresponding designs for each processor implemented in the LX110T

|             |       | MicroBlaze |        | LEC    | N3     | Cortex-M0<br>DesignStart | OpenRIS | C 1200 |

|-------------|-------|------------|--------|--------|--------|--------------------------|---------|--------|

| Benchmark   | Units | Design     | Score  | Design | Score  | Score (CB0)              | Design  | Score  |

| WhetstoneDP | WMIPS | MB0        | 8.37   | LB16   | 93.40  | 1.89                     | OB16    | 3.12   |

| WhetstoneSP | WMIPS | MB0        | 175.15 | LB16   | 97.30  | 9.01                     | OB16    | 6.75   |

| basicmath   | BPS   | MB0        | 0.14   | LB16   | 3.70   | 0.08                     | OB16    | 0.04   |

| fft         | BPS   | MB0        | 4.40   | LB64   | 104.33 | 3.04                     | OB16    | 2.57   |

Table 5: Highest floating-point benchmark scores (with FPUs enabled) and corresponding designs for each processor implemented in the LX110T

|             |           | MicroBlaze |           | LEON3  |       | Cortex-M0<br>DesignStart | OpenR  | ISC 1200  |

|-------------|-----------|------------|-----------|--------|-------|--------------------------|--------|-----------|

| Benchmark   | Units     | Design     | Score     | Design | Score | Score (CB0)              | Design | Score     |

| WhetstoneDP | WMIPS/MHz | MB0        | 0.065     | LB16   | 1.215 | 0.025                    | OB16   | 0.049     |

| WhetstoneSP | WMIPS/MHz | MB0        | 1.365     | LB16   | 1.266 | 0.117                    | OB16   | 0.106     |

| basicmath   | BPS/MHz   | MB0        | 1.076E-03 | LB16   | 0.048 | 1.063E-03                | OB16   | 7.045E-04 |

| fft         | BPS/MHz   | MB0        | 0.034     | LB64   | 1.357 | 0.040                    | OB16   | 0.040     |

Table 6: Floating-point performance per MHz for each processor (with FPUs enabled) implemented in the LX110T

## 3.8 Conclusion to Chapter 3

After analysis and comparison of the available commercial and open-source softcore processors, it seemed safe to conclude that performance-wise, some more-than-capable open-source softcores exist. The major concern was the support and community around the open-source processors, compared to commercial ones, where one receives guaranteed support with an IP license. However, further investigation refuted that concern. OpenRISC1200 and LEON3 have been tested, developed and conformed for quite a while, although LEON3 is a clear winner in this case. The amount of research and written publications on LEON3 is extensive [32, 33, 34, 35, 36]. Moreover, the Yahoo group [37] on LEON3 is highly active today. The activities in the group have been monitored since October of 2017; it is suffice to say that most questions asked by users are addressed within one to two days.

The level of customization and scalability is the second aspect that makes LEON3 most the attractive of all the previously mentioned softcores. This is mainly because it has SPARC architecture. The third reason is that development tools are extensive, compared to other open-source softcores, and the possibility exists to further develop a free licensed LEON3 to FT version, which has already been done by Gaisler and some other researchers [38, 39, 40]. The fourth reason is the extent of documentation and guides on LEON3, which is second to none of the open-source softcore processors [41, 42, 43, 44, 45, 46, 47, 48].

# 4 LEON3

This chapter covers relevant parts of The Gaisler Research IP Library, its structure and IP cores. The IP cores are important parts of LEON3's customizability, and they are collectively an adaptability for future implementations. Necessary LEON3 tools for development and testing are discussed in section 4.2.

# 4.1 The Gaisler Research IP Library

The Gaisler Research IP Library (GRLIB) [49] is an integrated set of reusable IP cores, designed for SoC development and provided under the GNU GPL license. This library includes a LEON3 processor; an advanced microcontroller bus architecture (AMBA) AHP/APB control; an FPU; an SPI; a UART with first in first out (FIFO); a modular timer unit; an interrupt controller, a 32-bit GPIO port; and memory and pad generators for Virage, Xilinx, UMC, Atmel, Altera, Actel, eASIC and Lattice among others. Some of the said IP cores are discussed further in this section. The library can be obtained from the Gaisler download page [50].

## 4.1.1 LEON3/FT - High-performance SPARC V8 32-bit Processor

LEON3 is a 32-bit processor core conforming to the IEEE-1754 (SPARC V8) architecture. It is designed for embedded applications, combining high performance (HP) with low complexity and low power consumption. The LEON3 core has the following main features: a seven-stage pipeline with the Harvard architecture, separate instruction and data caches, an MMU, a hardware multiplier and divider, on-chip debug support, and multiprocessor extensions. The LEON3 core block diagram is depicted in Figure 9 [42, p. 1177].

## 4.1.2 Integer Unit

The integer unit includes a signed or an unsigned 32x32 multiplier module (MUL32), and a signed or an unsigned 64/32 divider module (DIV32), and it supports the collection of HP multipliers from the Arithmetic Module Generator at the Norwegian University of Science and Technology (MULTLIB).

Figure 9: Block diagram of LEON3

#### 4.1.3 **The MUL32**

The multiplier module takes two 32-bit signed or unsigned numbers and produces a 64-bit result. The MUL32's performance and latency is dependent on its configuration, which has many varieties. The module can be easily configured to perform DSP functions, with MAC operations.

#### 4.1.4 The DIV32

The divider module utilizes the radix-2, non-restoring, iterative division algorithm to perform 64-bit by 32-bit division. The division leaves no remainder and takes 36 clock cycles.

## 4.1.5 High-Performance IEEE-754 Floating-point Unit

The GRLIB includes HP floating unit (GRFPU), which implements floating-point operations as defined in the IEEE Standard for Binary Floating-Point Arithmetic (IEEE-754) and the SPARC V8 standard (IEEE-1754). The GRFPU supports single- and double-precision floating-point formats, and it can be configured to utilize a non-blocking unit for the execution of divide and square-root operations.

## 4.1.6 The IEE-754 Floating-Point Lite Unit

The GRFPU-Lite FPU implements the same operation standards as the GRFPU. The key differences between the units are that GRFPU-Lite is not pipelined, and executes one floating-point operation at a time. This results in the GRFPU-Lite utilizing fewer resources at the cost of performance.

#### 4.1.7 Cache Sub-system

LEON3 has a configurable cache system consisting of separate instruction and data caches. Both caches can be configured with one to four sets, 1-256 KiB/way, and 16 or 32 bytes per line. The cache system can be also configured to utilize least-recently-used (LRU), least-recently-replaced (LRR), or pseudo random replacement policies.

#### 4.1.8 Memory Management Unit

A SPARC V8 reference MMU (SRMMU) provides mapping between multiple 32-bit virtual address spaces and physical memory. The MMU can be configured to up to 64 fully associative translation lookaside buffer (TLB) entries per implemented TLB.

## 4.1.9 Interrupt Interface

LEON3 supports the SPARC V8 interrupt model with a total of 15 asynchronous interrupts. The interrupt interface provides the functionality to both generate and acknowledge interrupts.

#### 4.1.10 Advanced Microcontroller Bus Architecture

An AMBA is a bus architecture standard devised by ARMs. Three key points of this standard are technology independence, electrical characteristics, and timing specifications.

The GRLIB includes two cores with AMBA standards, an advanced HP bus (AHB) and AHP.

## 4.1.11 Advanced High-Performance Bus

An AHB is an HP SoC bus that can connect a maximum of 16 masters and 16 slaves. It has a plug-and-play (P&P) functionality and is provided with an interrupt controller. The LEON3 processor uses one AHB master interface for all data, instruction and MMU tablewalk accesses.

### 4.1.12 Advanced Peripheral Bus

An advanced peripheral bus (APB) is a peripheral bus designed for low bandwidth control accesses, such as register interfaces and on system peripherals. An AHP is the main peripheral bus system of the GRLIB, and it is connected through the AHB.

#### 4.1.13 The AHB and APB Interfaces, Bridges and Controllers

The GRLIB includes many IP cores with AHB and APB interfaces as well as bridges, which increase the accessibility to other types of components. Some of the more notable bridges are AHB to AXI, I2C to AHB, SPI to AHB, PCI to AHB, Uni, and bi-directional AHB/AHB bridges.

Some of the AHB and APB interfaces are the JTAG debug link with an AHB master interface, the single-port RAM/ROM with an AHB interface, the AMBA AHB serial debug interface, the APB UART serial interface, the on-chip SRAM with an EDAC and AHB interface.

The main AHB controller is an AHB controller with P&P support.

Figure 10: A typical LEON/GRLIB design centered around one AMBA AHB bus and a AMBA APB bus that connects some peripherals cores via an AHB/APB bridge

#### 4.1.14 General-purpose I/O Port

The GP I/O port (GRGPIO) is an I/O port that is scalable from a 2- to a 32-bit width with an optional interrupt support. Each bit in the GRGPIO can be individually set to input or output and can optionally generate an interrupt.

## 4.1.15 The GRLIB Directory Structure

The main GRLIB directory includes five subdirectories:

- The Bin directory contains all the files that are required for handling of the GRLIB. Graphical user interface for configuration and synthesis (xconfig) files are found in this directory.

- The Boards directory contains folders with timing constraints, pin definitions and placing for most of the common FPGA boards in the market.

- The Design directory contains folders with template designs of LEON3 for different FPGA boards. All the template designs include finished scripts for the synthesis, simulations and FPGA board programming. Scripts are available as single files or compiled through a Make function. The tailored LEON3 is configured according to FPGA constraints, and it is explained in a detailed README.txt for all the FPGA boards.

- The Doc directory contains documentation such as the GRLIB IP Library User's Manual, the GRLIB IP Core User's Manual, the Configuration and Development Guide, and the SPARC V8 manual.

- The Lib directory is the core of the GRLIB. It contains behavioral VHDL descriptions

for all the IP cores. Subdirectories are mainly divided into vendors and standards. The

tech and techmap subdirectories contain all the necessary packages and hardware

descriptions to ensure technology independence.

- The Software directory contains a few sample programs in C for LEON3 testing, GPIO interaction, and APB UART control.

- The additional Netlist directory needs to be downloaded and installed for LEON3 implementations on different FPGA boards.

### 4.2 LEON3 Tools

Cobham Gaisler provides several tools and utilities for LEON3 development, debugging, testing and simulation. Tools are also available from other vendors; they are important for monitoring, and simulation of LEON3.

#### 4.2.1 Cobham Gaisler Monitor

Cobham Gaisler provides two debug monitors (GRMON2 and GRMON3) for LEON3. GRMON provides a debug environment for real target hardware, and it is used with a LEON3 debug support unit (DSU). This DSU supports connection and communication through numerous interfaces by control through any AMBA AHB master.

#### 4.2.2 **GRMON2**

GRMON2 is a console-based debug monitor and provides (but is not limited to) the following basic features:

- Read/write access to all LEON registers and memory

- Download and execution of LEON applications

- Breakpoint and watchpoint management

- Remote connection to the GNU debugger (GDB)

- GRLIB P&P support

- Supported debug interfaces: PCI, USB, Ethernet, JTAG, UART, and SpaceWire

- Tcl interactive interpreter support

- Common Flash interface (CFI) compatible Flash PROM programming

- Auto-probing and initialization of LEON peripherals and memory settings

#### 4.2.3 **GRMON 3**

GRMON3 is a newer version of GRMON with new graphical user interface. Some of the newer features are as follow:

- Execution control with support for multiple CPUs and OS threads

- Context-based virtual memory handling

- Basic execution control such as single-stepping, continuing, and breaking

- An GRLIB SoC system hardware overview