# A radiation tolerance study of the ALICE TPC Readout Control Unit 2

# ZHAO Chengxin

Dissertation submitted for fulfilment of the degree of Doctor of Philosophy at the University of Oslo, Norway

August 2017

#### © Zhao Chengxin, 2017

Series of dissertations submitted to the Faculty of Mathematics and Natural Sciences, University of Oslo No. 1916

ISSN 1501-7710

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, without permission.

Cover: Hanne Baadsgaard Utigard.

Print production: Reprosentralen, University of Oslo.

# Acknowledgement

It has been almost five years since I started my PhD in August 2012. Lots of memories come to my mind while I am writing this page. I have met some gem-like personalities during my stay at Oslo, Bergen and Geneva. I am so grateful for your help and supports.

First of all, I want to thank my supervisors Ketil Røed and Johan Alme. If you hadn't supported and believed in me, I would not able to break the darkness of my PhD and make it alright. Thank you for bringing me back to correct path while I was feeling hopeless in 2014. Ketil has helped in all the aspects from academic to personal life. He told me that the process of PhD life is to create the path in a wild forest, sometimes I might be lost but I need to keep on going. The valuable advices that I got from him in the tons of discussions and e-mail exchanges will benefit my whole life. Johan is always willing to give me the positive comments. This makes me confident and it is very important for me to persist on my research. He is always answering my questions in a patient manner, even for the most basic and boring ones.

The same thanks also go to my supervisor Helge Balk and former supervisor Kjetil Ullaland. Helge helped me a lot in the administrative stuffs and solved the practical issues of my first days in Oslo. Kjetil's guidance and advice during our occasional discussions in Bergen has been quite helpful in electronic design.

Dear Toralf Bernhard Skaali, I have to show my special gratitude to you. Thanks for picking me up and this changed the track of my life. Thanks for introducing me to the Norwegian group and the support you have given to me during the past years. Many thanks always go to Dieter Rörich for the advice on how to proceed my PhD and helping me to involve into the Norwegian community. I want to thank Attiq Ur Rehman for spending so many days with me in the lab in Bergen and at CERN. The hands-on experience in electronics design is quite important for my further career. Also thank you for having patience with my faults.

A very special thank you to Lars Bratrud. Our friendship started from debugging the PHOS electronics and then goes to all the parts in our life.

I am thankful to the whole Norwegian group and the RCU2 community. Thanks to all the guys that I met in Oslo, Bergen, Geneva, Uppsala, Stockholm, Beijing, Wuhan and Changsha.

The last but the biggest gratitude is to my family. Thanks for your supports during last three decades. I am proud of you.

Chengxin

Oslo, May 2017

## **Abstract**

ALICE is a general-purpose detector that is designed to study the physics of quark-gluon plasma. The Time Projection Chamber (TPC) is one of the major detectors of ALICE. The TPC electronics consists of 4356 Front-end cards (FECs), which are controlled by 216 Readout Control Units (RCU). Each RCU connects to between 18 and 25 FECs using a multi-drop bus. In LHC Run1, the Readout Control Unit 1 (RCU1) performed even better than specification. However, in Run2 the energy of colliding beams is increased from 8 TeV to 14 TeV (maximum value) and higher luminosity, which leads to larger event size and higher radiation load on the electronics. As a solution, the Readout Control Unit 2 (RCU2) is designed to provide faster readout speed and improved radiation tolerance with respect to the RCU1.

The RCU2 is conceptually similar to the RCU1 and it reuses the existing infrastructure and readout architecture of the TPC electronics. However, the multi-drop bus is split into four branches from the two branches and the bandwidth of the Detector Data Link (DDL) is increased from 1.60 Gbps to 3.125 Gbps. Correspondingly, the firmware is designed to utilize the improved parallelism. These actions ensure that the readout speed of the RCU2 can be improved by a factor of ~2 with respect to the RCU1. The flash-based Microsemi Smartfusion2 FPGA SOC is used as the main FPGA instead of the SRAM based Xilinx Virtex 2 Pro FPGA that was used on the RCU1. Because its configuration cells are immune to Single Event Effects, the radiation tolerance of the RCU2 was expected to be improved.

The primary objective of this thesis has been to study the radiation tolerance of the RCU2. This is done through several irradiation tests, which are divided into two steps. To start with, the radiation sensitivity of the Smartfusion2 FPGA and all the hardware interface are characterized. Afterwards, a system-level irradiation test is performed. Actions have been taken against all the radiation related problems that were revealed during the irradiation tests. Running experience shows that radiation tolerance of the readout system based on RCU2 is about 10 times better as compared to the RCU1 for p-Pb collisions at similar energy level.

The second objective of this thesis was to develop the firmware modules that realizes the readout algorithms. Development of the firmware has gone through three versions, the first prototype, the

second prototype and the commissioning version, and important contributions were made to the first two versions.

The integration and testing of the RCU2 is also an important task covered in this thesis. Functional tests were performed for the mass production, the irradiation tests at and the final installation at the TPC. Readout performance of the RCU2 has been characterized and the solutions aiming to further increase the readout speed have been proposed and verified.

# **Table of Contents**

| l Introduc | tion                                     |

|------------|------------------------------------------|

| 1.1 The    | ALICE Experiment                         |

| 1.1.1      | ALICE sub-detectors                      |

| 1.1.2      | The Time Projection Chamber (TPC)4       |

| 1.2 The    | e TPC readout electronics in Run15       |

| 1.2.1      | The Front-end Card (FEC)6                |

| 1.2.2      | The Readout Control Unit (RCU)6          |

| 1.3 TPC    | C consolidation effort during LS18       |

| 1.3.1      | Motivation8                              |

| 1.3.2      | Solutions9                               |

| 1.4 Prin   | nary objective and main contribution     |

| 1.4.1      | Radiation Tolerance                      |

| 1.4.2      | Design, Integration and Test of the RCU2 |

| 1.5 Out    | line of the thesis                       |

| 2 Radiatio | n effects on the RCU2                    |

| 2.1 Inte   | eraction of particle with matters        |

| 2.1.1      | Charged particles                        |

| 2.1.2      | Neutral particles                        |

| 2.2 Ra   | adiation Effects related to the RCU2        | 18 |

|----------|---------------------------------------------|----|

| 2.2.1    | Radiation environment of the RCU2           | 19 |

| 2.2.2    | Single Event Effects (SEEs)                 | 20 |

| 2.2.3    | Total Ionizing Dose (TID) effect            | 23 |

| 2.2.4    | Summary                                     | 24 |

| 2.3 Irr  | radiation tests                             | 24 |

| 2.3.1    | Selection of test facilities                | 24 |

| 2.3.2    | Dose calculation                            | 27 |

| 2.3.3    | Predicating the rate of SEEs induced errors | 28 |

| 3 The RO | CU2                                         | 29 |

| 3.1 RO   | CU2 overview                                | 29 |

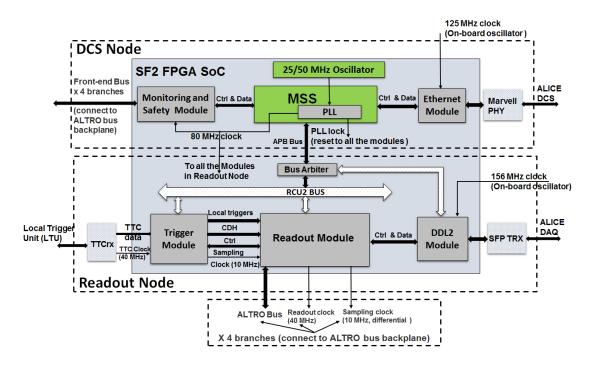

| 3.1.1    | The RCU2 main FPGA                          | 32 |

| 3.1.2    | TTC Interface                               | 34 |

| 3.1.3    | DCS Interface                               | 34 |

| 3.1.4    | DAQ Interface                               | 36 |

| 3.1.5    | Radiation Monitor (RadMon)                  | 36 |

| 3.1.6    | ALTRO bus backplane                         | 37 |

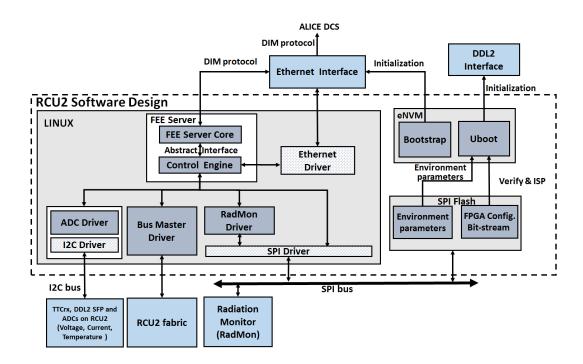

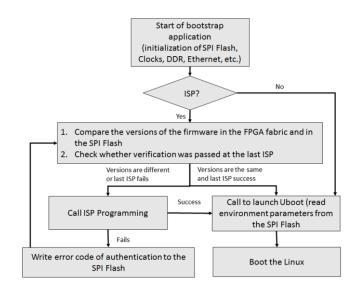

| 3.1.7    | Software design                             | 38 |

| 3.2 Sn   | nartfusion2 (SF2) firmware overview         | 41 |

|   | 3.2.1   | Clocking and reset scheme                 | 42 |

|---|---------|-------------------------------------------|----|

|   | 3.2.2   | Firmware versions                         | 43 |

|   | 3.2.3   | Trigger Module                            | 45 |

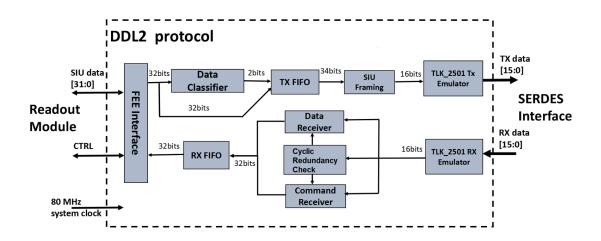

|   | 3.2.4   | DDL2 Module                               | 45 |

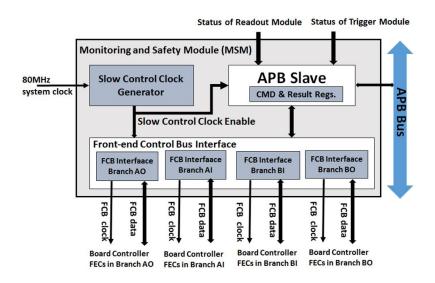

|   | 3.2.5   | Monitoring and Safety Module              | 46 |

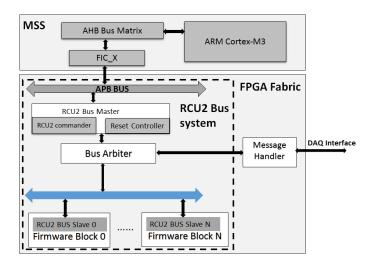

|   | 3.2.6   | RCU2 Bus                                  | 47 |

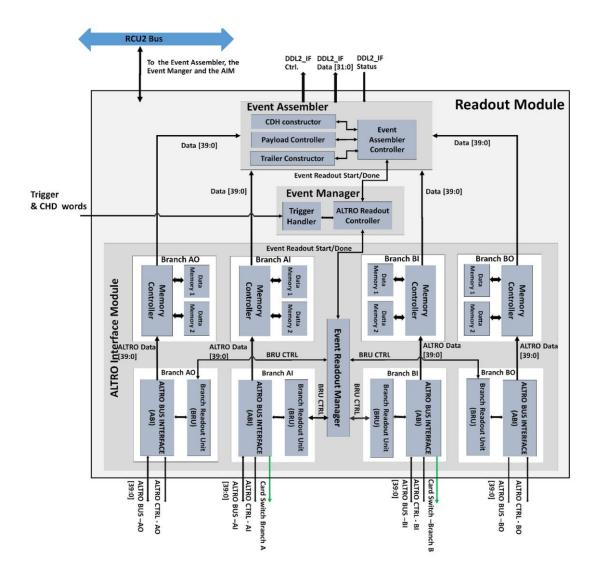

|   | 3.3 Re  | eadout Module                             | 48 |

|   | 3.3.1   | First prototype                           | 49 |

|   | 3.3.2   | Second prototype                          | 50 |

|   | 3.3.3   | Commissioning version                     | 59 |

|   | 3.4 Su  | mmary                                     | 63 |

| 4 | Radiati | on Tolerance of the RCU2                  | 65 |

|   | 4.1 Te  | sted devices                              | 66 |

|   | 4.2 Ch  | naracterization of the Smartfusion2 (SF2) | 68 |

|   | 4.2.1   | Single Event Latch-up (SEL) test          | 68 |

|   | 4.2.2   | Fabric SRAM test                          | 71 |

|   | 4.2.3   | Embedded SRAM test                        | 74 |

|   | 4.2.4   | Flip-flop test                            | 75 |

|   | 4.2.5   | PLL test                                  | 77 |

| 4.2.6   | Total Ionizing Dose (TID) effects test          |

|---------|-------------------------------------------------|

| 4.3     | Hardware Interface tests81                      |

| 4.3.1   | TTC interface test82                            |

| 4.3.2   | DAQ interface test85                            |

| 4.3.3   | DCS interface test                              |

| 4.4     | System level irradiation test                   |

| 4.4.1   | Readout stability90                             |

| 4.4.2   | DCS stability92                                 |

| 4.5     | Radiation Monitor test94                        |

| 4.6     | Summary and Conclusion96                        |

| 5 Testi | ng and integration99                            |

| 5.1     | Validation of the ALTRO Interface               |

| 5.1.1   | Test with simple ALTRO bus master               |

| 5.1.2   | Test with ALTRO Bus Interface Module            |

| 5.2     | Test with the second prototype of firmware      |

| 5.3     | Test with the commissioning version of firmware |

| 5.3.1   | DDL2 link at 2.125 Gbps                         |

| 5.3.2   | DDL2 link at 4.25 Gbps                          |

| 5.3.3   | DDL2 link at 3.125 Gbps                         |

| 5     | 5.3.4 Discussion on Radiation Mitigation   | 114 |

|-------|--------------------------------------------|-----|

| 5.4   | Summary                                    | 117 |

| 6 S   | Summary and conclusion                     | 119 |

| 6.1   | Main Contribution                          | 119 |

| 6.2   | Running experience                         | 120 |

| 6.3   | Outlook                                    | 121 |

| Refer | rence                                      | 123 |

| Appe  | endix A. List of publications              | 129 |

| A.1   | As main contributor                        | 129 |

| A.2   | As collaborator                            | 129 |

| Appe  | endix B. List of Abbreviations             | 130 |

| Appe  | endix C. Fluence calculation               | 133 |

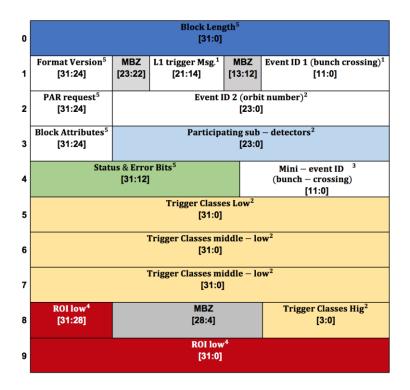

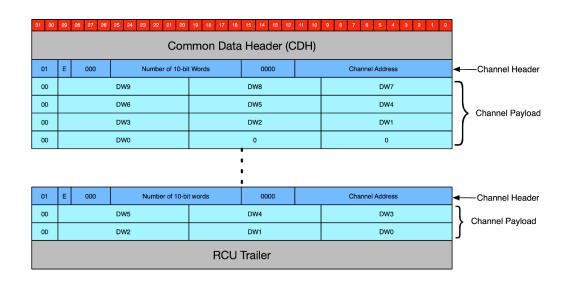

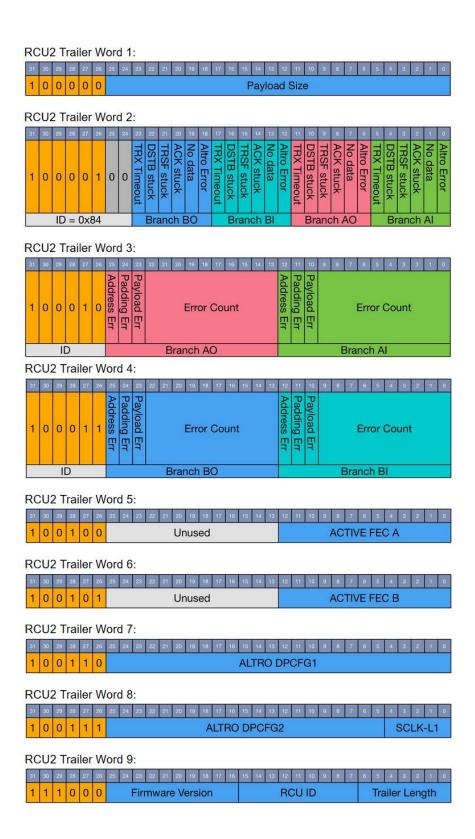

| Appe  | endix D. RCU2 Data Format                  | 134 |

| Appe  | endix E. Screenshots and test results      | 136 |

| E.1   | SEU counts of SRAM tests                   | 136 |

| E.2   | Screenshots of tests                       | 137 |

| E.3   | Readout speed benchmark                    | 138 |

| E.4   | Procedure of test prior to mass production | 139 |

| E.5   | Commissioning of the RCU2                  | 141 |

# **List of Figures**

| Figure 1-1 The LHC with four experiments                                                                | 1  |

|---------------------------------------------------------------------------------------------------------|----|

| Figure 1-2 Roadmap of LHC to its full potential                                                         | 1  |

| Figure 1-3 The ALICE detector                                                                           | 2  |

| Figure 1-4 Three-dimensional view of the TPC                                                            | 4  |

| Figure 1-5 Layout of the TPC readout electronics                                                        | 5  |

| Figure 1-6 Signal path in the TPC readout electronics                                                   | 6  |

| Figure 1-7 Front view of the RCU1                                                                       | 7  |

| Figure 1-8 Schematic layout of the RCU1                                                                 | 7  |

| Figure 1-9 Sketch of the RCU2 design [18]                                                               | 10 |

| Figure 1-10 Comparison of the readout time between RCU2 simulations and measurement of RCU1 in LHC Run1 |    |

| Figure 2-1 Mitigation of MBUs in memory cells in SF2                                                    | 21 |

| Figure 2-2 Structure of floating gate transistor in flash-based FPGA                                    | 23 |

| Figure 2-3 Test facility of the Oslo Cyclotron .                                                        | 25 |

| Figure 2-4 Test facility of the Svedberg Laboratory.                                                    | 26 |

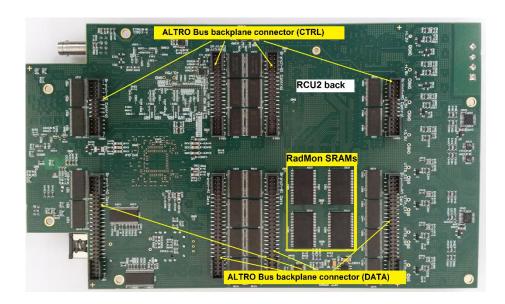

| Figure 3-1 Overview of the RCU2                                                                         | 30 |

| Figure 3-2 RCU2 Board (front side)                                                                      | 31 |

| Figure 3-3 RCU2 Board (back side)                                                                       | 32 |

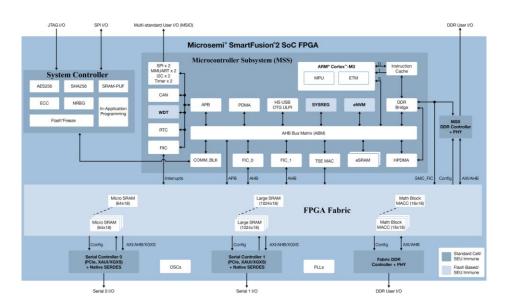

| Figure 3-4 Schematic layout of the SF2 FPGA SoC          | 33 |

|----------------------------------------------------------|----|

| Figure 3-5 Digital part of the DCS Interface             | 35 |

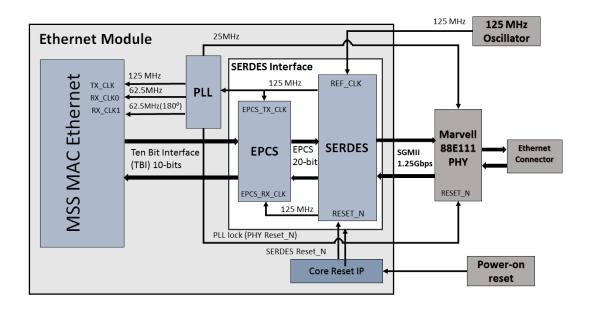

| Figure 3-6 The DAQ Interface                             | 36 |

| Figure 3-7 ALTRO bus backplane                           | 38 |

| Figure 3-8 Architecture of RCU2 Software Design          | 39 |

| Figure 3-9 Flowchart of the software booting process     | 40 |

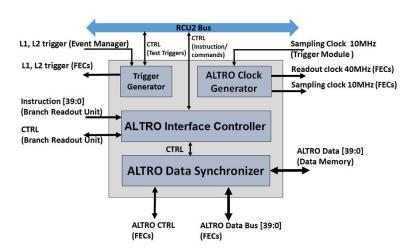

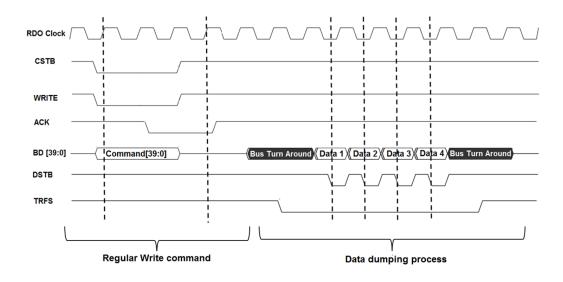

| Figure 3-10 Overview of the RCU2 firmware                | 42 |

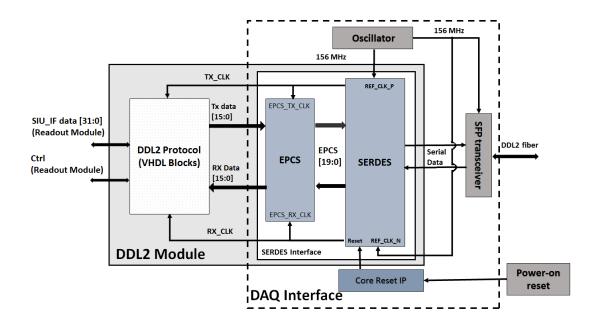

| Figure 3-11 DDL2 protocol blocks                         | 46 |

| Figure 3-12 Monitoring and Safety module sub-modules     | 47 |

| Figure 3-13 RCU2 bus structure topology                  | 48 |

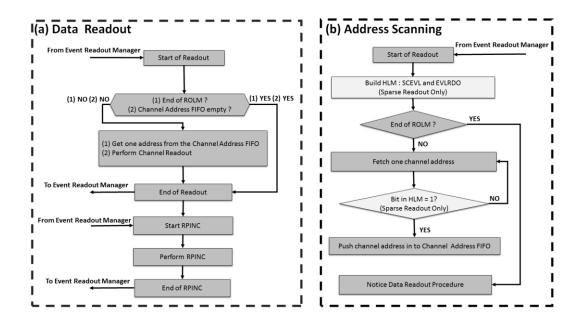

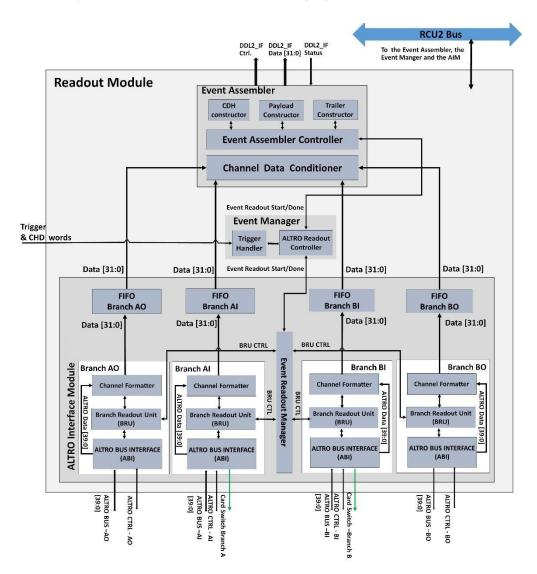

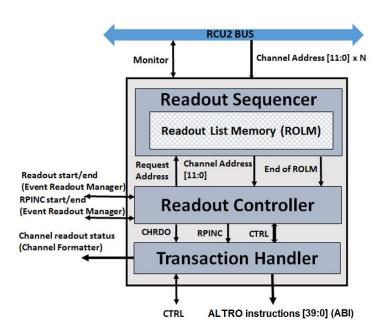

| Figure 3-14 Second prototype of Readout Module           | 51 |

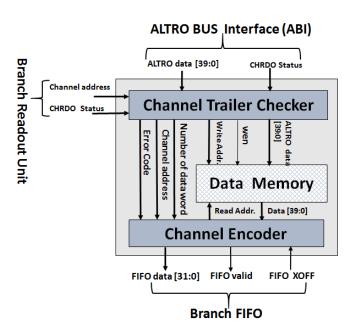

| Figure 3-15 ALTRO Bus Interface sub-module               | 52 |

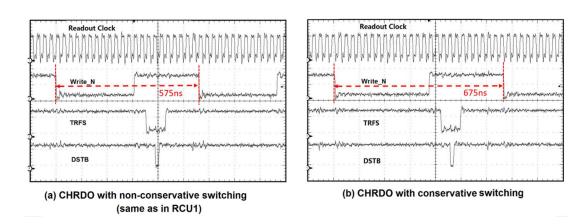

| Figure 3-16 Chronogram of the CHRDO command              | 53 |

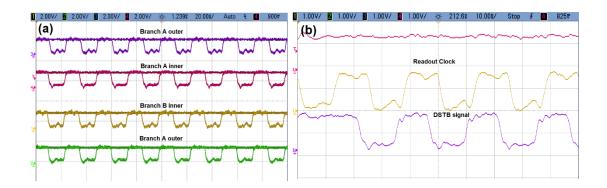

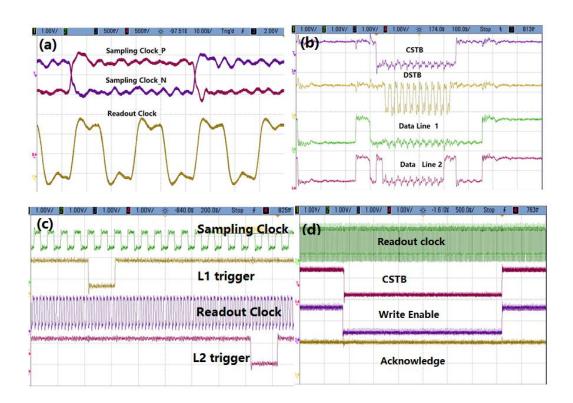

| Figure 3-17 Screenshot of CHRDO operations               | 54 |

| Figure 3-18 Branch Readout Unit sub-module               | 55 |

| Figure 3-19 Flow chart of the Branch Readout Unit        | 56 |

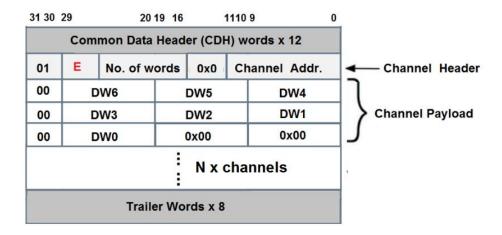

| Figure 3-20 RCU2 Data package structure                  | 58 |

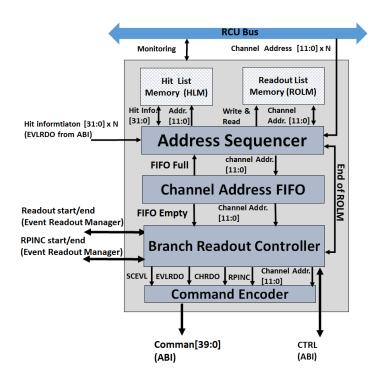

| Figure 3-21 Commissioning version of Readout Module      | 60 |

| Figure 3-22 Sub-module topology of the Channel Formatter | 61 |

| Figure 3-23 Sub-module topology of the Branch Readout Unit                         | .62 |

|------------------------------------------------------------------------------------|-----|

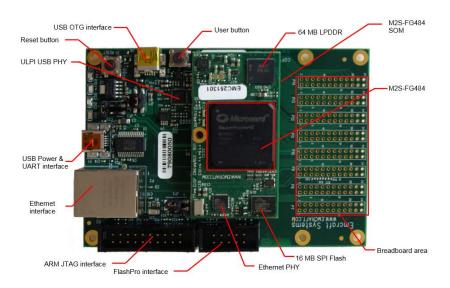

| Figure 4-1 Emcraft SF2 Starter-Kit                                                 | .67 |

| Figure 4-2 SEL test setup                                                          | .68 |

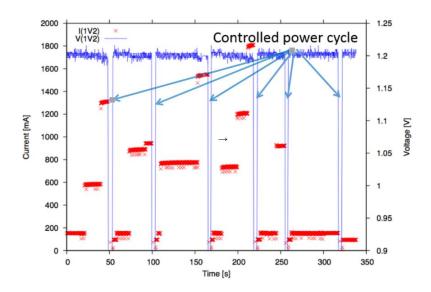

| Figure 4-3 Current consumption of the SF2 FPGA in first SEL test                   | .69 |

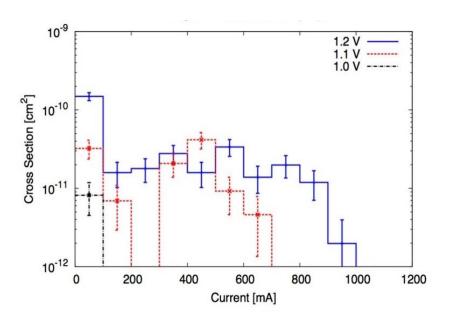

| Figure 4-4 Cross-section of current jumps vs. supply voltage in the first SEL test | .70 |

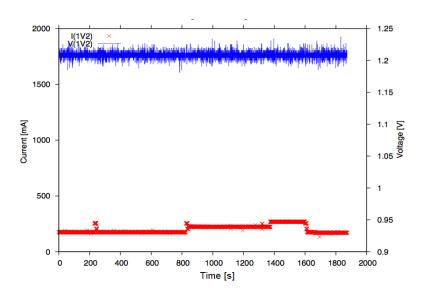

| Figure 4-5 Current consumption of the SF2 FPGA in second SEL test                  | .71 |

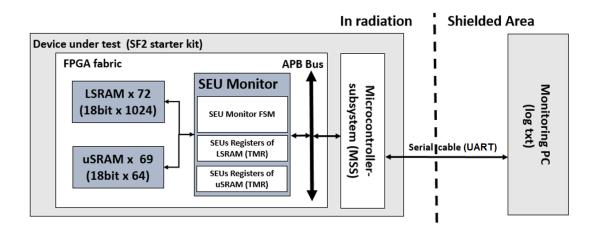

| Figure 4-6 SRAM irradiation test setup                                             | .72 |

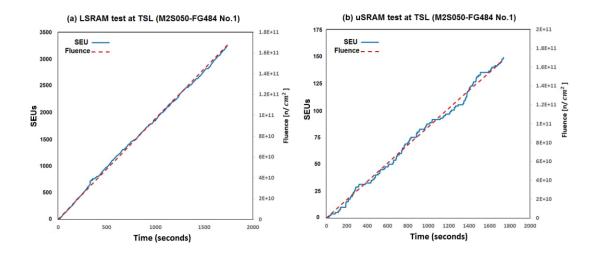

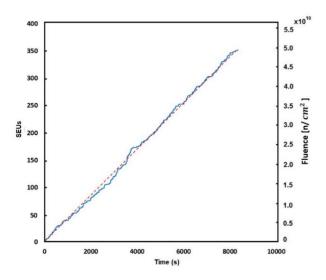

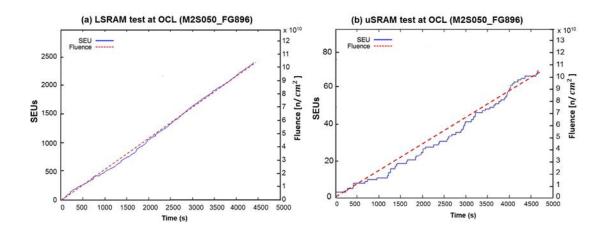

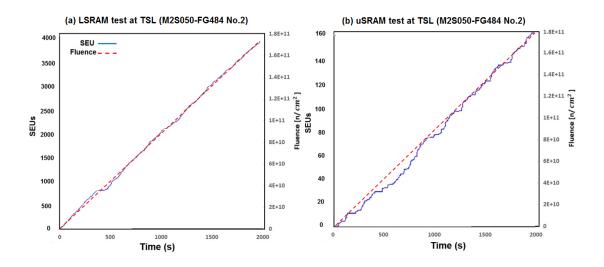

| Figure 4-7 SEUs and fluence for the SRAM test in campaign No.3                     | .72 |

| Figure 4-8 SEUs and fluence for the eSRAM test at campaign No.7                    | .74 |

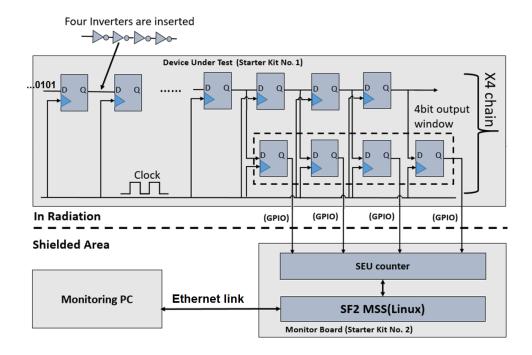

| Figure 4-9 Flip-flop test setup                                                    | .75 |

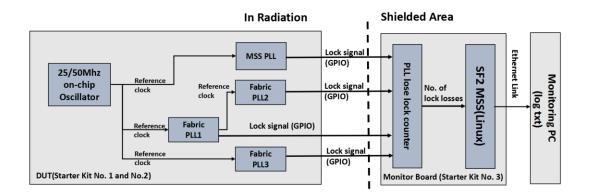

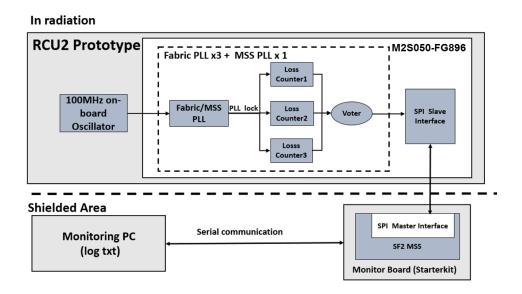

| Figure 4-10 First PLL test setup in campaign No.3                                  | .77 |

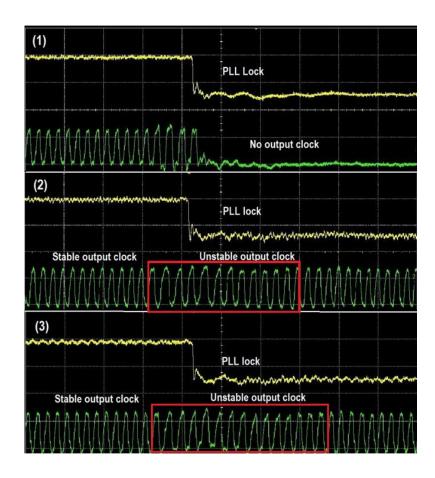

| Figure 4-11 Output clock of PLL with different configuration when it loses lock    | .78 |

| Figure 4-12 Second PLL test setup in campaign No.6                                 | .80 |

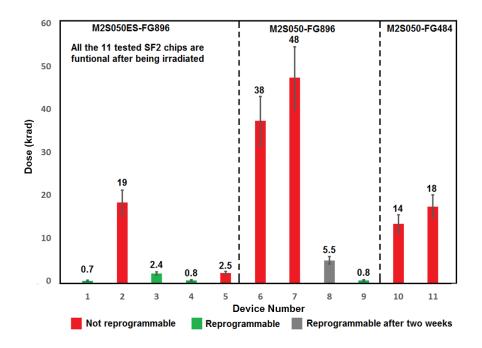

| Figure 4-13 TID effect on the SF2 chip                                             | .81 |

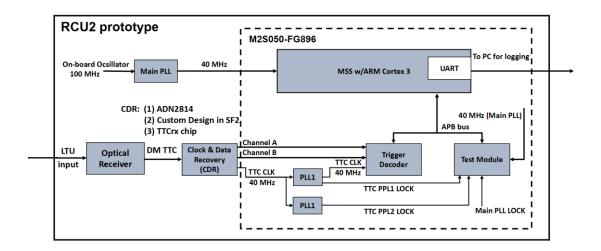

| Figure 4-14 Setup of the TTC interface test                                        | .82 |

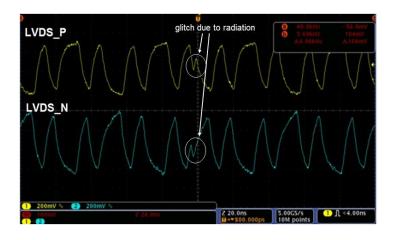

| Figure 4-15 Example of radiation effect in an optical receiver                     | .84 |

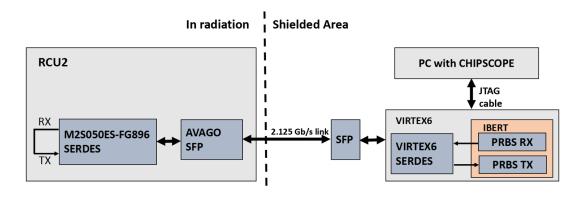

| Figure 4-16 Setup of the DAQ interface irradiation test                            | .86 |

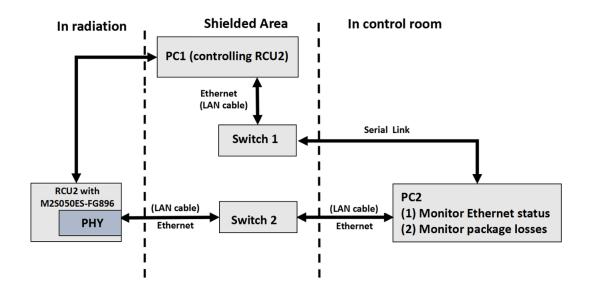

| Figure 4-17 Test setup of DCS Interface                                            | .86 |

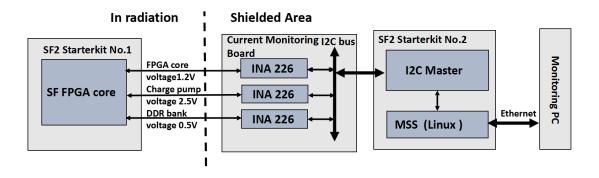

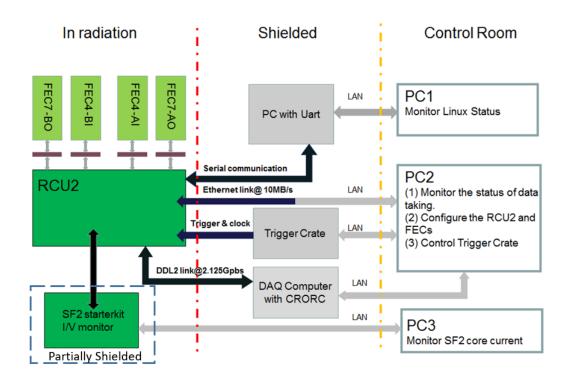

| Figure 4-18 Setup of system level irradiation test                                 | .88 |

| Figure 4-19 Setup of the system-level irradiation test (without collimator)      | 89 |

|----------------------------------------------------------------------------------|----|

| Figure 4-20 Setup of the system-level irradiation test (with collimator)         | 90 |

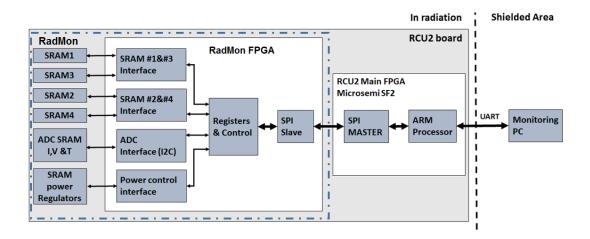

| Figure 4-21 Setup of the RadMon test                                             | 94 |

| Figure 4-22 SEU counts as a function of fluence of the RadMon test               | 95 |

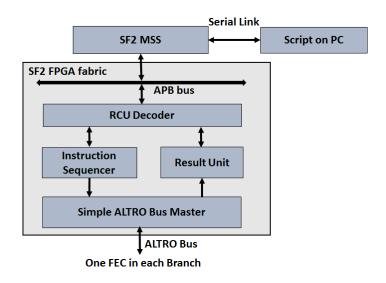

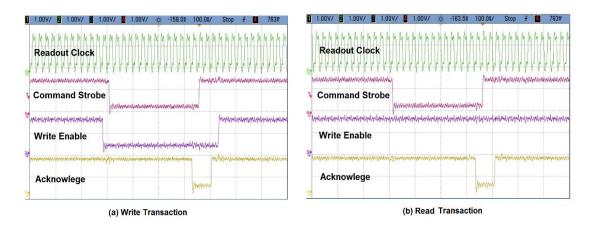

| Figure 5-1 Test design with the simple ALTRO bus master                          | 00 |

| Figure 5-2 Observation of the write and read transaction                         | 00 |

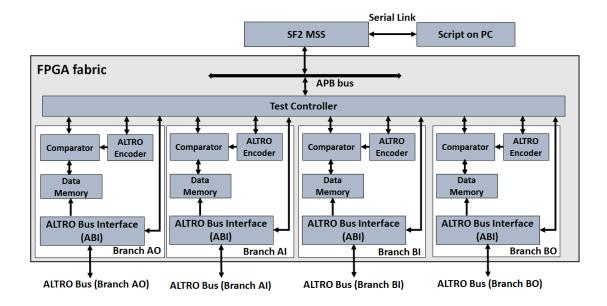

| Figure 5-3 Test design with the ALTRO Bus Interface                              | 01 |

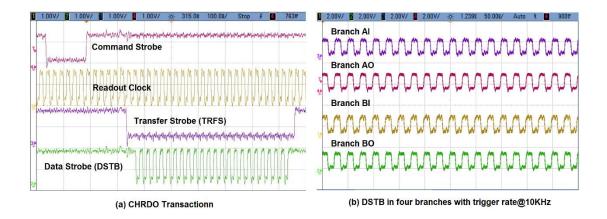

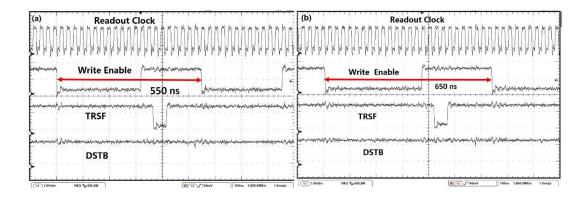

| Figure 5-4 Screenshot of CHRDO transaction                                       | 02 |

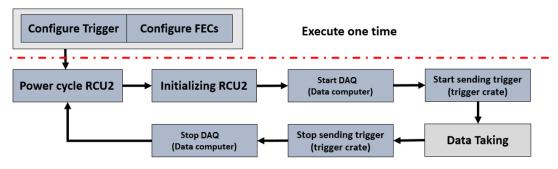

| Figure 5-5 Test procedure for the RCU2 with the second prototype of firmware 10  | 03 |

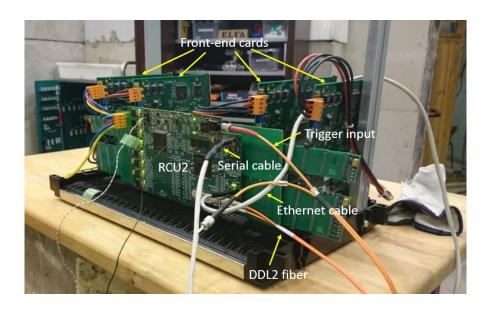

| Figure 5-6 The CERN setup - 1 RCU2 connects to 25 FECs                           | 06 |

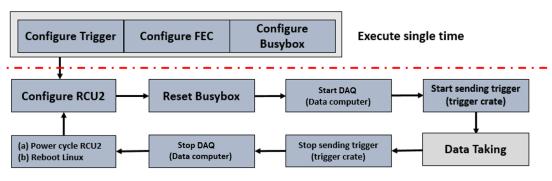

| Figure 5-7 Test procedure for the RCU2 with the production of firmware           | 06 |

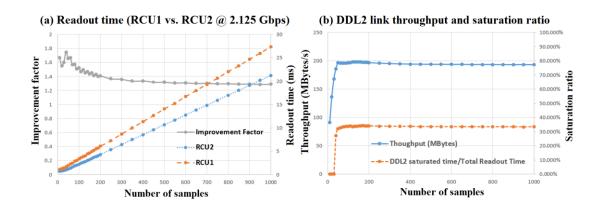

| Figure 5-8 Benchmarking on the RCU2 with DDL2 at 2.125 Gbps                      | 08 |

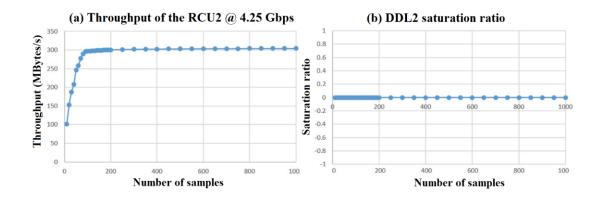

| Figure 5-9 Benchmark on the RCU2 with DDL2 at 4.25 Gbps                          | 09 |

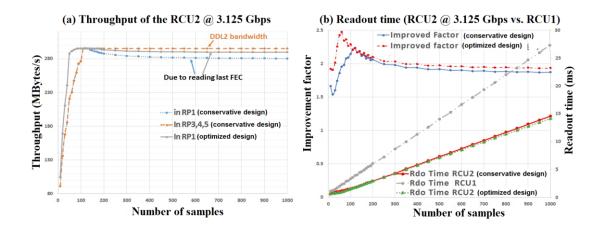

| Figure 5-10 Benchmarking of the RCU2 with DDL2 at 3.125 Gbps                     | 12 |

| Figure 5-11 Measurement of reading single word from one channel                  | 14 |

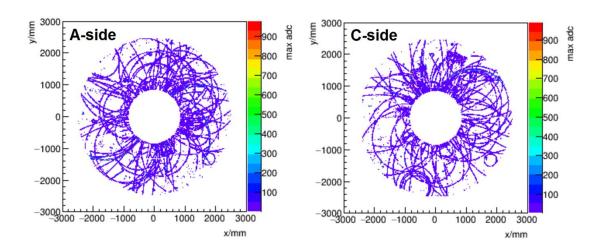

| Figure 5-12 Reconstructed data taken by TPC in the first p-Pb collision in Run21 | 18 |

| Figure D-1 CDH words of RCU2                                                     | 34 |

| Figure D-2 RCU2 payload words                                                    | 34 |

| Figure D-3 RCU2 Trailer words                                                    | 35 |

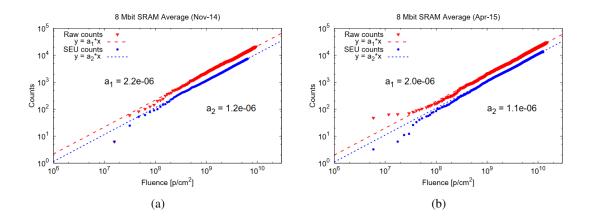

| Figure E.1-1 SEUs and fluence for the SRAM test in campaign No.2      | 136 |

|-----------------------------------------------------------------------|-----|

| Figure E.1-2 SEUs and fluence for the SRAM test in campaign No.3      | 136 |

| Figure E.2-1 Measurement of RCU2 signals                              | 137 |

| Figure E.2-2 Measurement of CHRDO for an empty channel                | 137 |

| Figure E.2-3 Measurement of CHRDO for the number of samples as 10     | 138 |

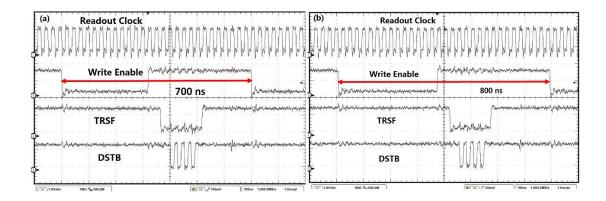

| Figure E.4-1 Inspection of oscillator                                 | 140 |

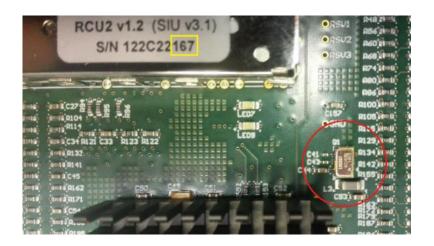

| Figure E.4-2 Screenshot of data-taking status                         | 141 |

| Figure E.5-1 The first 6 installed RCU2                               | 142 |

| Figure E.5-2 Data loop in sector (six readout partitions)             | 143 |

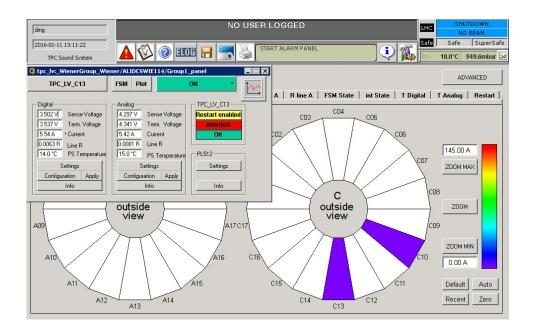

| Figure E.5-3 Radiation Monitor of the RCU2                            | 143 |

| Figure E.5-4 Check the DCS of installed partitions (colored blue)     | 144 |

| Figure E.5-5 Check the Status of FECs (Monitoring and Safety Module)  | 144 |

| Figure E.5-6 Check the power of installed partitions (colored purple) | 145 |

# **List of Tables**

| Table 3-1 Resources comparison between the RCU1 main FPGA, the RCU2 main                                               |

|------------------------------------------------------------------------------------------------------------------------|

| FPGA and the RCU1 firmware                                                                                             |

| Table 3-2 Execution time of each transaction for RCU163                                                                |

| Table 4-1 Overview of the irradiation campaigns (time-wise)66                                                          |

| Table 4-2 SRAM test results73                                                                                          |

| Table 4-3 Flip-flop test results76                                                                                     |

| Table 4-4 PLL test results79                                                                                           |

| Table 4-5 TTC interface test results (PLL lose lock)83                                                                 |

| Table 4-6 DAQ interface test results85                                                                                 |

| Table 4-7 DCS interface irradiation test results                                                                       |

| Table 4-8 Readout stability observations91                                                                             |

| Table 4-9 DCS stability observation93                                                                                  |

| Table 4-10 Summary of the MTBF in Run2 of the RCU297                                                                   |

| Table 5-1 Stress test of the ALTRO interface                                                                           |

| Table 5-2 System level validation of the RCU2 (second prototype of firmware) 104                                       |

| Table 5-3 System level validation of the RCU2 (commissioning version of the firmware wth DDL2 bandwidth of 2.125 Gbps) |

| Table 5-4 Test results of 6 sample RCU2s                                                                               |

| Table 5-5 Reliability estimation of the complete RCU2116                                                               |

| Table 5-6 verification of firmware with mitigation actions              | . 117 |

|-------------------------------------------------------------------------|-------|

| Table 6-1 Overview of End of Run (EoR) reasons for the ALICE experiment | .120  |

| Table E.3-1 Readout speed of single event (partition 1)                 | .138  |

# 1 Introduction

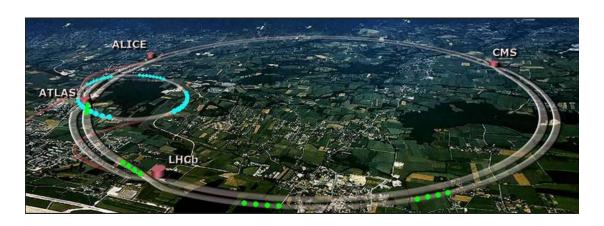

The Large Hadron Collider (LHC) is the largest particle accelerator in the world. It is hosted by CERN<sup>1</sup>, the European Organization for Nuclear Research, which is located near Geneva on the border between Switzerland and France. The LHC lies about 100 meters beneath the ground in a tunnel with a circumference of 27 kilometers. Two particle beams accelerated close to the speed of light travel in opposite directions and collide at dedicated locations, where four major experiments, ALICE [1], ATLAS [2], CMS [3] and LHCb [4], are positioned, see Figure 1-1.

Figure 1-1 The LHC with four experiments [5]

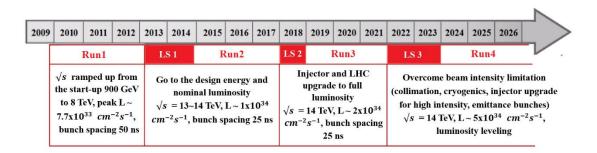

Figure 1-2 Roadmap of LHC to its full potential (from [6] with the add-on of the Run1 scenario)

As shown in Figure 1-2, the roadmap of the LHC to achieve its full design energy has been divided

<sup>&</sup>lt;sup>1</sup> CERN is the acronym of its French name Conseil Européen pour la Recherche Nucléaire

into several running periods and long shut-down periods. In the running periods, the LHC provides collisions for the experiments to take physics data. In the long shut-down periods, the LHC and the experiments are under maintenance and upgrade as a preparation for the next running period. During the first successful running period from November 2009 to February 2013 (Run1), the LHC ramped up its center-of-mass energy from the start-up 900 GeV to  $7 \sim 8$  TeV. In the second running period (Run2) which started in 2015 and will last until 2018, the center-of-mass energy of the collisions will reach up to 13 TeV for p-p collisions.

This thesis is part of the upgrade activities for the readout electronics of the ALICE Time Projection Chamber (TPC) [7] during the long shut-down 1 (LS1). Hence, this chapter will introduce the ALICE experiment and the TPC readout electronics used during Run1. As already mentioned, Run2 will introduce a higher energy in the collisions, and the practical implications of this will be discussed at the end of this chapter as part of the motivation for the upgrade.

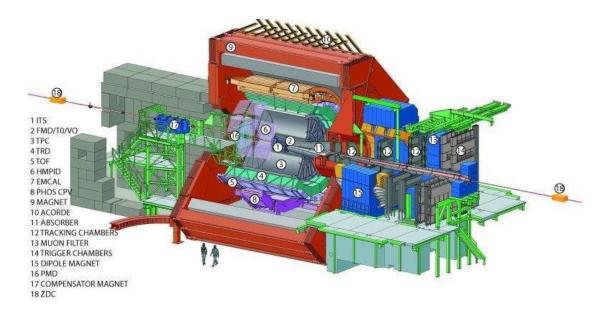

Figure 1-3 The ALICE detector [1]

### 1.1 The ALICE Experiment

ALICE is a general-purpose detector designed to study the physics of quark-gluon plasma. In normal condition, quarks are bound into hadrons by the force carrier of the strong force (gluons). A Pb-Pb collision in the LHC will create an extremely high temperature and energy density so that the

hadrons undergo a phase transition into quark-gluon plasma, where the quarks and gluons are not in a bound state. According to the theory of the Big Bang, the universe was in a state of quark-gluon plasma up to a few milliseconds after the Big Bang. As the temperature and the density dropped, the quarks and gluons were bound into different kinds of hadrons, which constitute the basic building block of matters. Since the life-time of quark-gluon plasma is rather short, it cannot be observed directly. Hence, the ALICE detector is comprised of several sub-detectors that are designed to observe the signatures that indicate the existence of quark-gluon plasma and to study its properties. Details on the physics and experimental observables of the ALICE experiment can be found in [1].

#### 1.1.1 ALICE sub-detectors

A collision at the LHC is called an event, and it produces a large number of secondary particles. The ALICE experiment is optimized to study Pb-Pb events, but pp and Pb-p events are recorded as well to provide reference data [1]. For each event, the momentum of the charged particles and the energy of the neutral particles are measured and in addition the types of particles (hadrons, electrons, photons and muons) are identified. Figure 1-3 gives the schematic layout of the ALICE detector. The size is  $26x16x16m^3$  with a weight of 10,000 tons. To accomplish the above-mentioned tasks, a set of sub-detectors are placed in different layers, in some distance away from the central collision point. These sub-detectors can be sorted into three categories: the central detectors, the forward sub-detectors and the muon spectrometer. Details on these sub-detectors can be found in [1] and only a short summary is presented here.

The central detectors can be sorted into the central tracking detectors, the particle identification detectors and the calorimeters. The central tracking detectors include the Inner Tracking System and the cylindrical TPC. The Inner Tracking System is designed to localize the primary vertex and reconstruct the secondary vertices. It comprises six layers of silicon detectors. The innermost two layers are the Silicon Pixel Detector, the middle two layers are the Silicon Drift Detectors, and the outermost two layers are the Silicon Strip Detector. The TPC is the main tracking detector in the ALICE experiment. Together with other central detectors, it is optimized to provide the charged particle momentum measurement, the particle identification and the vertex determination. The Transition Radiation Detector, the Time of Flight detector and the High-Momentum Particle Identification Detector are particle identification detectors. The Transition Radiation Detector is designed to identify electrons with the momenta above 1 GeV/c. The Time of Flight detector and

the High-Momentum Particle Identification Detector identify the charged particles (protons, kaons and muons) having intermediate and large momentum, respectively. Two calorimeter detectors, the Photon Spectrometer and the electromagnetic calorimeter (EMCal, since 2015 DCal) are designed to detect photons and measure particle jets, respectively.

The forward sub-detectors include the Zero Degree Calorimeter, the Photon Multiplicity Detector, the Forward Multiplicity Detector, the Veto and the Time Zero. These forward sub-detectors measure the multiplicity and the spatial distortion of the non-interacting nucleons, which can be used to determine the geometry of the collision. In addition, the Veto and the Time Zero are also responsible for providing minimum biased triggers.

The muon spectrometer detects muons after all the other particles have been stopped by the absorbers in the forward region and provides fast trigger decisions.

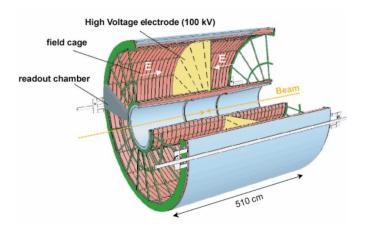

Figure 1-4 Three-dimensional view of the TPC [8]

#### **1.1.2** The Time Projection Chamber (TPC)

The TPC is the main tracking detector in the ALICE experiment. The layout of the TPC detector is shown in Figure 1-4. It is a cylindrical volume of 88 m<sup>3</sup> that is divided in to two field cages by a high voltage electrode and filled with gas that can be ionized. The TPC has an inner radius of 0.85 m and an outer radius of 2.8 m. It spreads over 5.1 m along the path of the colliding beams. Charged particles created in the collisions ionize the gas. In the presence of the electric field, the

electrons will drift toward the end-plates, where multi-wire proportional chambers are used to multiply the electrons from primary ionization.

#### 1.2 The TPC readout electronics in Run1

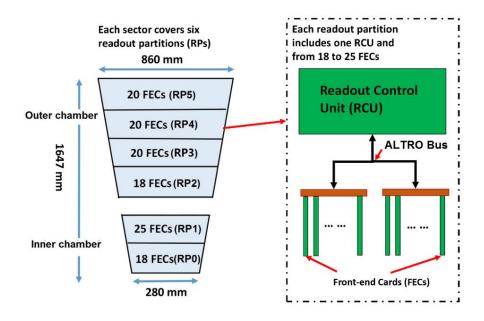

In the TPC there are in total 557 568 detector pads divided equally between the two end-plates, each of which is mapped to an individual channel in the readout electronics. The TPC readout electronics consists of 4356 Front-End Cards (FECs) and 216 Readout Control Units (RCUs), which are distributed into 36 trapezoidal sectors (18 in each end-plate). As shown in Figure 1-5, each sector covers six readout partitions along the radial direction in the TPC barrel. Each readout partition consists of from 18 to 25 FECs, depending on the readout partitions, which are connected to one RCU with a parallel multi-drop bus – the ALICE TPC Readout (ALTRO) [9] bus.

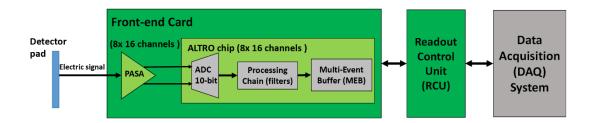

Figure 1-6 shows the signal path in the TPC readout electronics. The FEC processes the electric signals generated by the charges deposited on the detector pad and buffers the data. The RCU reads the data from the FECs, processes it and then transmits it to the Data Acquisition (DAQ) system [10].

Figure 1-5 Layout of the TPC readout electronics

Figure 1-6 Signal path in the TPC readout electronics

#### 1.2.1 The Front-end Card (FEC)

As shown in Figure 1-6, each FEC contains 128 signal channels, which are realized by 8 Preamplifier Shaper (PASA) [11] chips and 8 ALTRO chips. The PASA amplifies and shapes the electric signals from the detector pads. The ALTRO chip does analog to digital conversion, digital signal processing and buffering of the acquired data.

In addition, the FEC holds one SRAM based FPGA, the Board Controller. The Board Controller does low level control system tasks like monitoring of current, voltages and temperatures on the FEC. In addition, it controls the direction of the ALTRO bus in the communication between the actual FEC and the RCU.

#### **1.2.2** The Readout Control Unit (RCU)

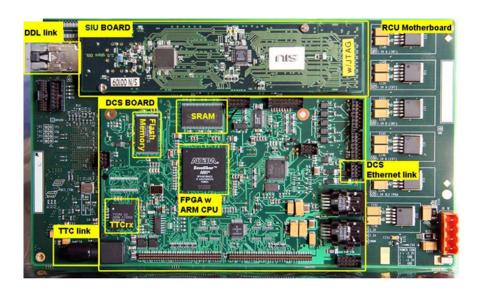

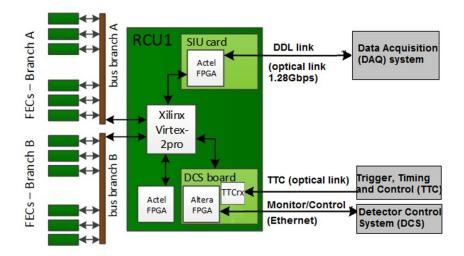

A front view and schematic layout of the RCU used in LHC Run1 can be found in Figure 1-7 and Figure 1-8, respectively. From here on this RCU is named RCU1. It consists of a motherboard with two daughter boards: The Detector Control System (DCS) [12] board and the Source Interface Unit (SIU) card.

The DCS board hosts a TTCrx [13] chip that processes the trigger information coming from the Trigger, Time and Control (TTC) [7] via an optical link and provides the 40 MHz clock. In addition, a minimalistic Linux platform is running on the ARM processor embedded in a SRAM-based Altera FPGA [14]. Dedicated software operating on this Linux platform propagates the monitoring values to the DCS through an Ethernet link, so that any potential hazardous situation can be detected.

The SIU card ships the packaged data, coming from the motherboard, to the DAQ through an optical

link of 1.280 Gbps. The protocol of the Detector Data Link (DDL) [7] is implemented on a flash-based FPGA on the SIU card.

Figure 1-7 Front view of the RCU1

Figure 1-8 Schematic layout of the RCU1

The motherboard holds the RCU1 main FPGA (SRAM-based Virtex Pro2 [15]) and a supporting FPGA (flash-based Actel APA075 [16]). The main FPGA is in charge of the data readout algorithms. It moves the sampled data from the FECs to the RCU1, processes and packages the data, and then pushes the data to the SIU card. At the time when the choice of the main FPGA was made, no flash-based FPGAs with enough resources were available to implement the readout algorithm, thus the

SRAM-based FPGA was selected [17]. Because the configuration memory of the main FPGA is proven to suffer Single Event Upsets (SEUs), the flash-based supporting FPGA has been added to detect the SEUs and reconfigure the main FPGA.

#### 1.3 TPC consolidation effort during LS1

#### 1.3.1 Motivation

Due to the enlarged event size and the increased event rate, the RCU1 was expected to limit the readout rate for Run2 [18]. In addition, the radiation related issues are expected to be more critical in Run2 because of the higher radiation load [19]. The limitations on the RCU1 is discussed below.

#### **Data rate limitations**

All the FECs are connected to the RCU1 via the ALTRO bus, which is divided into two separate branches. The bandwidth of each branch is 1.60 Gbps and it serves from 9 to 13 FECs, depending on the readout partitions. The readout time of an event is defined as that of the slowest readout partition, which is the readout partition 1 with 25 FECs. In each branch, all the channels in all the FECs need to be read sequentially. Therefore, for high occupancy events like central Pb-Pb collisions, the readout through the ALTRO bus is the bottleneck of the readout system.

According to the measurement for Pb-Pb events in 2010, the readout time of the TPC reached up to 4 ms (250 Hz), depending on the number of tracks [20]. In Run2 a readout rate of 400 Hz is expected and the event size will increase by 25% [20]. To accomplish this performance, the readout speed of the RCU1 needs to be improved by a factor of at least 2.

#### **Radiation Tolerance**

One major challenge for the TPC electronics is the radiation created by the colliding beams in the LHC. There are two kinds of radiation effects that is of concern, the Single Event Effects (SEEs) and the Total Ionizing Dose (TID) effect. The SEE is a transient effect, which is induced by a single ionizing particle. The TID effect is cumulative effect which refers to the total dose received by the Front-End Electronics (FEE) during its life-time. Two quantities that are commonly used to describe the radiation environment are the flux and the dose. Details regarding the radiation environment of TPC and the radiation effects can be found in section 2.1 and section 2.2.

In general, the RCU1 was performing very well in Run1. However, it is not a radiation-tolerant system and the main reason is the SRAM-based main FPGA. The radiation effects, of which the dominant ones are the SEUs in the configuration cell of the main FPGA, leading to the readout getting stuck (busy) or corrupted event headers [21]. Consequently, these errors caused stops of the data-taking in Run1 [18]. The SEU sensitivity of the RCU1 FPGA design has been characterized in [19], and it was found that about 1% of the SEUs will lead to the abortion of a physics run. In addition, there is no radiation protection on the DCS board, whose main FPGA is also SRAM-based. In Run1, the DCS board has experienced frequent communication errors (DCS-RCU) and communication losses (Ethernet to the DCS) [18]. Although these scenarios are not critical for data-taking, the loss of monitoring should be avoided.

In Run1, the longest data-taking session in heavy-ion collisions is 8 hours and 4 mins (run 138275 in the logbook [22]). In Run2, the duration of each data-taking session should be similar to that in Run1, so the RCU2 should be capable of reading data continuously for at least ~8 hours.

As mentioned above, in Run2 the expected radiation load in terms of the flux of fast hadrons on the TPC electronics located in the innermost locations (worst-case) will increase to 3.0 kHz/cm² from the 0.8 kHz/cm² in Run1 [18]. With such a significant increase, radiation effects are therefore foreseen to occur more frequent on the RCU1 in Run 2(discussed in section 2.2). Considering the study of the SEU rate for heavy ion runs in 2011 and the luminosity for Run2, the data-taking is expected to stop around every single hour, if no actions are taken on the RCU1 [18].

#### Conclusion

Based on the information presented above, it was concluded that the readout rate needed to be increased by a factor of at least 2. In addition, the radiation tolerance should also be improved to withstand the higher radiation load in Run2.

#### 1.3.2 Solutions

To consolidate the readout system and improve its performance, two upgrade options have been discussed. The first one is the Front-End Card Interface solution [23] and the second one is the Readout Control Unit 2.

#### The Front-End Card Interface solution

In this solution, each FEC is connected to a Front-End Card Interface that translates the parallel ALTRO bus interface into a serial one, which could deal with the peak data rate of 1.60 Gbps [23]. Therefore, the readout speed of the upgraded system could be improved with a factor of 10 with respect to that of the RCU1 [23]. In addition, this solution is also relevant for the upgrades planned for Long Shutdown 2 (LS2) given the fact that it would use components and an infrastructure that would be reminiscent of the planned LS2 upgrade [18].

However, this solution was eventually dropped because a lot of new PCB boards and fibers needed to be produced and installed in the TPC, which was not suitable for the aggressive time scale of LS1.

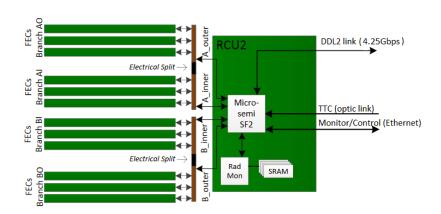

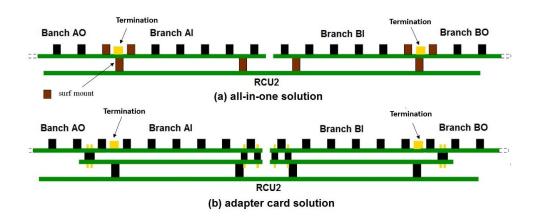

Figure 1-9 Sketch of the RCU2 design [18]

#### The Readout Control Unit 2 (RCU2)

The RCU2 was then proposed to give the needed performance. A sketch of the RCU2 is shown in Figure 1-9. The RCU2 is conceptually similar to the RCU1 and it reuses the existing infrastructure and architecture of the TPC electronics, such as the cables for TTC, DCS, DAQ and power. However, the ALTRO bus has been split from the current two branches into four branches. Correspondingly, the DDL protocol has been upgraded to the DDL2 protocol [24], which uses the same fiber but has a higher theoretical bandwidth of 4.25 Gbps. To utilize the improved parallelism, a new readout algorithm has also been implemented (discussed in section 3.3.1). The RCU2 could not improve the readout speed by a factor of 10 as the Front-End Card Interface solution. However, assuming there is no other bottleneck in the system, it could ensure at least a doubling of the readout speed, which

still fulfills the requirements for Run2.

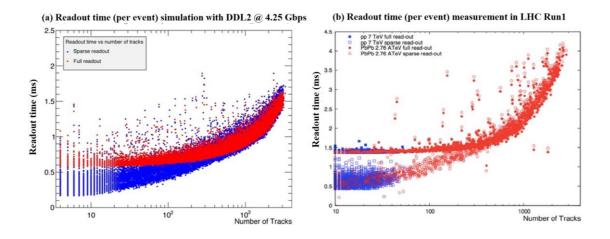

Before designing the RCU2, simulations were performed with a SystemC [25] model<sup>2</sup> of the new readout architecture. Actual data recorded in the heavy ion collisions in 2010 was used and bandwidth of the DDL2 link was set to be 4.25 Gbps. The simulation showed that the readout time of the largest event is ~1.6 ms (in subplot (a) in Figure 1-10), which is 2.5 times faster than the current speed of 4.0 ms (in subplot (b) of Figure 1-10). Taking the 25% increase on the event size into consideration, the readout rate of the RCU2 will reach ~500 Hz (2 ms), which doubles the readout speed of the RCU1.

Figure 1-10 Comparison of the readout time between RCU2 simulations [26] and the measurement of RCU1 in LHC Run1 [20]

The flash-based Microsemi Smartfusion2 (SF2) FPGA SoC [27][28], whose configuration memory is immune to SEU, was chosen as the main FPGA for the RCU2. Consequently, most of the stability issues seen in Run1, which can be traced back to the SEUs in the configuration cells of the RCU1 main FPGA [21], can be avoided in Run2. The PCB components of the RCU1 that has been proved functional in Run1 were considered to be reused. The components where no radiation tolerance related to the LHC environment was documented, including the SF2 FPGA, have been characterized and tested with several irradiation campaigns (discussed in Chapter 4).

<sup>&</sup>lt;sup>2</sup> Developed and simulated by Christian Lippmann (christian.lipmann@cern.ch)

#### 1.4 Primary objective and main contribution

The primary target of this Ph.D. project has been to study the radiation tolerance of the RCU2. This has involved irradiation testing of individual elements, work on improving the design, programming, connecting the elements and to run final tests.

#### 1.4.1 Radiation Tolerance

Several irradiation campaigns have been performed to evaluate the radiation tolerance of the RCU2. In this thesis, these tests have been divided in two steps. In the first step, radiation sensitivity of different aspects in the SF2 FPGA has been characterized (section 4.2) and all the hardware interfaces (section 4.3) on the RCU2 have been tested. The tests revealed potential issues and appropriate actions were implemented afterwards.

As a second step, a full system-level test of the RCU2 including the hardware, the firmware and the software was done under radiation in a situation close to normal operation. Stability issues regarding data readout and status control were observed. Actions to minimize the impact of these issues were later taken (section 4.4).

Based on the results of these irradiation tests, the cross-sections for different failure types have been extracted. While taking all the 216 RCU2 plus 4356 FECs into consideration, Mean Time Between Failure (MTBF) numbers for those failure types have been estimated for Run2.

#### 1.4.2 Design, Integration and Test of the RCU2

**Firmware design.** Originally, firmware modules that realize the readout algorithms (Readout Module) were planned to be inherited from the RCU1 FPGA design. Nevertheless, several engineering drawbacks were encountered while porting the firmware from the Xilinx FPGA to the SF2 FPGA (discussed in section 3.3.1). Therefore, the author of this thesis developed the first version of the Readout Module (section 3.3.2) for the RCU2. It is a new design but it inherits most of the concepts used in the RCU1 FPGA design. This module has been used in the system-level irradiation tests (section 4.4).

**System integration and test.** The integration and testing of the RCU2 is also an important task covered by this thesis. This task has been performed in two steps. Firstly, the functionality of the hardware interfaces has been verified (section 5.1). Secondly, all the firmware modules together with the Linux system have be integrated on the SF2 FPGA SoC. Then, the stability of the system has been tested and a benchmark of the readout speed has been performed (section 5.3). Two versions of the RCU2 system have been used in the tests: the second prototype (section 3.3.2) which has been used in the system-level irradiation test and the commissioning version<sup>3</sup> (section 3.3.3) that has been commissioned at the TPC. In addition, several designs for dedicated tests have also been developed by the author of this thesis (Chapter 5).

#### 1.5 Outline of the thesis

This thesis is structured into six chapters including this introduction chapter.

Chapter 2 describes the radiation environment of the TPC detector in Run2, the radiation effects on the RCU2 and the basics of the irradiation tests (selection of facility, dose calculation and SEU rate prediction).

Chapter 3 describes the RCU2 design. To start with, the hardware design is introduced. This includes the choice of the RCU2 main FPGA, the hardware interfaces, the Radiation Monitor and the ALTRO bus backplane. Furthermore, the firmware development on the RCU2 main FPGA has been discussed. This thesis focuses on the development of the modules that realizes the readout algorithms. In addition, functionality and structure of the other modules have been briefly discussed. And finally, the software design is presented.

Chapter 4 discusses the irradiation tests of the RCU2, which is the main contribution of this thesis. First of all, the test facilities are introduced and compared. Furthermore, characterization of the SF2 FPGA and test of the hardware interfaces are discussed. Finally, system-level irradiation tests of the RCU2, including the hardware, firmware and software, are presented. According to the test results, the expected error rate of various failures in the radiation environment of LHC Run2 is estimated and corresponded mitigation actions have been proposed. In addition, an evaluation of the Radiation

\_

<sup>&</sup>lt;sup>3</sup> Author of this thesis was not involved in the development of this version of firmware but performed the integration and test of the whole system (section 5.3).

Monitor is also presented. The chapter ends with a discussion on the radiation mitigation techniques in the FPGA fabric SRAMs and registers.

Chapter 5 discusses integration, validation and commission of the RCU2. Firstly, tests performed on the RCU2 prototype are discussed. This includes the stress tests on the RCU2 hardware prototype before mass production and validation on the RCU2 with second prototype of firmware before the system irradiation campaign. Secondly, integration and verification of the final RCU2 design and preparation of the mass installation are presented. A special focus has been put on the stability and the readout rate. Finally, commission of the RCU2 is discussed.

Chapter 6 concludes the thesis and describes the ongoing and planned work.

### 2 Radiation effects on the RCU2

Electronics which are exposed to a radiation environment (e.g. space, LHC) will potentially be affected by radiation effects. This also applies to the RCU2 which is exposed to the environment of the TPC. Therefore, it is of significant importance to know how these radiation effects are induced, how they affect the RCU2, and how to predict the rate of the radiation induced errors for LHC Run2.

### 2.1 Interaction of particle with matters<sup>4</sup>

In ALICE, heavy (Pb-Pb) and lower mass (e.g. pp) particles are collided to produce primary particles in high density. These particles can be divided into two categories: charged particles and neutral particles. Many of these particles interact with the absorbers and structural elements of the experiment, which produce hadronic and electromagnetic showers. The cascade of secondaries poses a radiation load on the electronic devices and consequently causes potential damages.

#### 2.1.1 Charged particles

Driven by the Coulomb force, which is the attraction or repulsion among particles due to the electric charge, charged particles interact with the atoms while passing through the material. In these interactions, the charged particles lose and transfer energy to the atoms through several processes: elastic or inelastic scattering with atomic electrons, elastic or inelastic scattering with nuclei, Bremsstrahlung, Cherenkov radiation, etc. Which of these processes dominate the energy loss depends on the energy, velocity, mass and charge of the particle as well as the properties of the material it collides with. For example, most of the energy loss in the interactions of heavy charged particles is through the non-elastic collisions with the atomic electrons in the material [29]. This process of energy loss is also called stopping power.

**Stopping Power<sup>5</sup>:** The stopping power (S) for a charged particle is defined as the differential energy loss (-dE) for this particle within the material divided by the corresponding differential length  $(d_x)$

<sup>&</sup>lt;sup>4</sup> This section is based on reference [29] and [30] if not otherwise stated.

<sup>&</sup>lt;sup>5</sup> The unit of stopping power is keV/um or MeV/cm.

of the path:

$$S = -\frac{dE}{dr} \qquad (2.1)$$

The stopping power is also called the rate of energy loss for a particle. It depends on the energy and type of the radiation as well as the property of the materials. The classical expression that describes the stopping power is the *Bethe–Bloch Formula* and is written as

$$-\frac{dE}{dx} = \frac{4\pi e^4 z^2}{m_0 v^2} NB$$

(2.2)

where

$$B \equiv Z \left[ ln \frac{2m_0 v^2}{l} - ln \left( 1 - \frac{v^2}{c^2} \right) - \frac{v^2}{c^2} \right]$$

(2.3)

with the following definitions:

v = velocity of the charged particle

z =charge of the particle in unit of e

N = number density of absorber atoms

Z = atomic number of absorber atoms

m = electron rest mass

e = electron charge

I = effective excitation and ionization potential of the absorber

B = stopping number (atomic number scaled for stopping)

The Bethe-Bloch Formula is valid for all types of charged particles provided their velocity remains large with respect to the velocity of the orbital electrons. Only the first item in the stopping number (B) is sufficient for the non-relativistic charged particles  $(v \ll c)$ . The stopping number (B) varies slowly with particle energy and is proportional to the atomic number (Z) of the absorber. Thus, the general behavior of stopping power can be inferred from the residual multiplicative factor. For a given non-relativistic particle,  $-dE/d_x$  varies as  $1/v^2$ , or inversely with particle energy.

The stopping power consists of two components, the mass collisional stopping power and the mass radiative stopping power. The former is resulted from the interactions of particles with orbital electron (i.e. atomic ionizations and excitations) and the latter is resulted from the interactions of particles with nucleus (i.e. bremsstrahlung production).

Linear Energy Transfer (LET)<sup>6</sup> is defined as the average energy (dE) locally deposited into the material by a charged particle of specific energy traversing a distance of  $d_x$  and it is written as  $dE/d_x$ . LET is closely related to stopping power except that it does not include radiative loss of energy (bremsstrahlung) and delta rays. For heavy charged particles, stopping power and LET are nearly equal; for beta particles, the delta-rays and the bremsstrahlung are not included in LET.

# 2.1.2 Neutral particles

Neutral particles are uncharged and therefore do not interact with matters by means of the Coulomb force. Neutrons and photons (gamma and X-rays) are typical neutral particles and the processes in their interactions are different.

**Neutrons:** Neutrons do not interact with atomic electrons, but interact with the nuclei of the atoms. Since the size of the nuclei is quite small compared to the whole atom, the probability of neutron interaction is rather low. Hence, neutrons could penetrate a long distance in the absorbing material before any interaction takes place. Processes in the nuclear interactions of neutrons highly depend on the available energy level. For example, the interactions of high energy neutrons will produce secondary radiation products (charged particles, neutrons, fission fragments, etc.), most of which transfer energy to the material through ionizing.

**Photons:** Photons are electromagnetic radiation with no rest mass, no charge, and travels at the speed of light. Energy of photon is in linear proportion to frequency (f) with the Plank's constant (h), and it is written as E = hf. All of the photon interactions lead to a partial or total transfer of the photon energy to the electron energy. There are three main processes in the energy transfer, which are photoelectric effects, Compton scattering and pair production.

\_

<sup>&</sup>lt;sup>6</sup> LET is strictly defined in terms of energy divided by distance, e.g., MeV/cm. However, since the energy lost is directly proportional to the density of the material traversed, it is useful to divide the LET by the density of the material. Therefore, the units of LET are also typically expressed as MeV· cm²/mg.

# 2.2 Radiation Effects related to the RCU2<sup>7</sup>

Electronic devices which are exposed to a radiation environment are expected to experience two categories of radiation effects: SEEs and cumulative effects. The cumulative effects include TID effect and Displacement Damage.

**Single Event Effects (SEEs):** SEEs originate from the energy deposited by single particle through ionization in a given sensitive volum, occurring in a short time. It is a transient effect and occurs stochastically. For the LHC environment, the charged hadrons<sup>8</sup> and the neutrons cannot deposit enough energy through direct ionization to induce a SEE. Instead, they generate a SEE through nuclear interaction with the material of the devices (section 2.1). Due to their statistical nature, SEEs are characterized with their probability of occurrence, which depends on the specifics of the radiation environment and the properties of the devices.

**Total Ionizing Dose (TID) effect:** TID is the progressive build-up of charges due to trapped holes in the insulating layers of MOSFET and BJT devices. Through ionization, electron-hole pairs are generated in the material along the particle track. Due to the high mobility, electrons can escape the oxide easily. In contrast, holes have a lower mobility, and can gradually be trapped in the dielectric. The TID effect may lead to parametric degradation (e.g. threshold voltage shift in MOSFET, current gain decreases in BJT) and eventually cause functional failure of the devices. TID is characterized by the maximum dose that a device can absorb before it no longer behaves within a given expected specification.

**Displacement damage:** Displacement damage is a non-ionizing effect and refers to the atomic displacement in the crystal lattice. If an incident particle can transfer enough energy to an atom in the crystal lattice by an elastic or inelastic collision, the atom can be knocked free from its lattice site and onto interstitial site. Displacement damage can change the electrical characteristics of certain components, e.g. reduced gain of bipolar transistors.

<sup>&</sup>lt;sup>7</sup> The basic principle of the radiation environment and the radiation effects on electronics is based on [31][32] and [33], if not otherwise stated.

<sup>&</sup>lt;sup>8</sup> In particle physics, a hadron is a composite particle made of quarks held together by the strong force in a similar way as molecules are held together by the electromagnetic force.

### 2.2.1 Radiation environment of the RCU2

Two quantities that are commonly used to describe a radiation environment are fluence rate and absorbed dose. Fluence rate<sup>9</sup>, also named flux, is defined as particles incident on a unit sphere or cross-sectional area per unit time. The time integrated flux is called fluence. Absorbed dose<sup>10</sup>, abbreviating as dose, is the mean energy imparted to per mass material minus the energy leaving the mass, either directly or through nuclear transformation. For a given number of particles, fluence and dose are correlated but not equivalent. In addition, another quantity named 1 MeV neutron-equivalent fluence<sup>11</sup> is normally used to express displacement damage.

Monte Carlo particle transport calculations shows that the radiation load in terms of the flux of fast hadrons on the TPC electronics locating in the innermost positions (worst-case) is estimated to be 0.8 kHz/cm², for the interaction rate of 8 kHz during Run1 [36]. Scaling the interaction rate to 30 kHz of Run2, the expected radiation load for Run2 will be 3.0 kHz/cm² [18]. This number is similar to what a satellite would encounter while traveling through the South Atlantic Anomaly [37] and ~ 0.6 million times of the radiation flux in ground level [38]. With such a significant number, SEEs are therefore expected to occur on the RCU2. For the 3 years running period of Run2, the total dose and the 1 MeV neutron-equivalent fluence are estimated to be less than a few krad and in the order of 10¹0 cm², respectively [18]. These number are not significant as the onset for the typical failures occur when the dose is over 10 krad and the 1 MeV neutron-equivalent fluence is above 10¹¹¹ cm² [39], so neither TID effect nor displacement damage is a big concern for the RCU2. However, TID effect on the SF2 FPGA still need to be considered, since it has previously been observed to lose its programmability at a low total dose level [40].

In the radiation environment of TPC, it is the high energy protons, neutron and pions (Energy > 10 to 20 MeV) that dominates the origin of the SEEs [36]. These high energy hadrons can be considered to be equally effective in their capability of producing SEEs [17]. In addition to these hadrons, there is also a considerable number of other particles (e.g. photons and electrons) that

<sup>&</sup>lt;sup>9</sup> Unit of flux is particles/cm<sup>2</sup>/s or a shorten version p/cm<sup>2</sup>/s [41].

<sup>&</sup>lt;sup>10</sup> Unit of dose is Gray and rad, where 1 rad = 0.01 Gray [41].

<sup>&</sup>lt;sup>11</sup> Unit of 1 MeV neutron-equivalent fluence is cm<sup>-2</sup> [41].

contributes to the TID effects [36].

### 2.2.2 Single Event Effects (SEEs)

The family of SEEs is quite wide. The main members of SEEs that may occur on the SF2 and the hardware interfaces of the RCU2 are discussed in the following sub-sections.

### **Single Event Upset (SEU)**

A SEU refers to a single bit-flip in the content stored in memory elements, which is induced by a single energetic particle strike [33]. A SEU will be provoked in the sensitive node if the energy deposited by single particle exceeds the critical charge of a storage element. SEUs are stochastic errors, which can happen in electronic devices at any time during their operation in radiation environment. SEUs are non-destructive and can be corrected by re-writing the memory elements.

The main FPGA of the RCU2 is the Microsemi SF2, which integrates a FPGA fabric, a Microcontroller Subsystem (MSS) [42] and several lanes of high speed serializer/deserializer (SERDES) interfaces [43]. Details regarding the SF2 are presented in section 3.1.1. The FPGA fabric of the SF2 is flash-based and its configuration cells are considered immune to SEU [28]. However, SEUs are still expected to occur in the SRAMs and in the flip-flops [44]. In addition, SEUs may also occur in the MSS of the SF2 and the hardware interfaces of the RCU2. If SEUs occur in critical bits, they may lead to Single Event Functional Interrupt, which will be discussed later in this section.

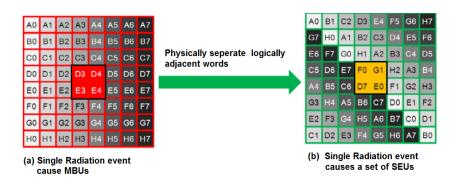

#### **Multiple-Bits Upsets (MBU)**

MBU refer to two or more bits in the same data word being flipped due to single radiation event. Because each bit-flip is actually a SEU, a MBU can be for simplicity treated as a set of SEUs.

In the SRAMs of the SF2, occurrence of MBUs is expected to be low for two reasons. Firstly, there is a physical distance between adjacent bits in the 65 nm manufacturing technology used for SF2 [45]. Secondly, as illustrated in Figure 2-1, logically adjacent data bits are physically separated in the memories. As a result, MBUs on physically adjacent bits can be divided into SEUs in several logical data words [45]. This dramatically reduces the probability of that an MBU will result in uncorrectable errors. In the irradiation tests performed by Microsemi in late 2014, the SF2 chips

were exposed to heavy ions at LET levels up to 90.3 MeV-cm<sup>2</sup>/mg and no MBUs were observed in the Large SRAMs, Micro SRAMs and flip-flops [45]. Therefore, no specific tests regarding MBUs will be discussed in this thesis.

Figure 2-1 Mitigation of MBUs in memory cells in SF2 [45].

#### **Single Event Transient (SET)**

If a single energetic particle hits the combinatorial logic in an integrated circuit, the deposited energy will give origin of a momentary pulse, which is defined as a SET [33]. In some cases, the transient pulse could propagate along the logic path until it is latched by some memory elements (e.g. SRAMs, flip-flop, latch), resulting in the changes on their output. As the clock frequency increases, the probability that SET will cause an upset in combinational logic increases. The ability of the SET to propagate and their probability of being captured by memory elements increases as well [34][35].

In this thesis, SET on the SF2 has been studied in terms of its probability of occurrence, varying the complexity of the combinatorial logics and the operating frequency of sequential logics (discussed in section 4.2.4).

### **Single Event Latch-up (SEL)**

A spurious current pulse induced by a single highly energetic particle passing through the sensitive regions of electronic components could bias the parasitic PNPN structure in the CMOS transistors and create a short between the power lines. In the JEDEC standard, this abnormal high-current state is defined as SEL [33]. SEL is potentially destructive and may cause permanent damage to electronic devices. If the device is not permanently damaged, a power cycle is required to the recover it back to normal operational situation. Several tests dedicated for SEL on the SF2 have therefore been

performed in this thesis (section 4.2.1). In the hardware interfaces of the RCU2, non-destructive SEL could induce Single Event Functional Interrupt and destructive SEL will lead to permanent damage.

### **Single Event Gate Rupture (SEGR)**

Transient gate leakage current induced by a single particle strike can lead to a high electric field. In the presence of this electric field, a subsequent conducting path through the gate oxide of a MOSFET can be built. This phenomenon is defined as SEGR [33], to which the power MOSFET in OFF state is susceptible. The SEGR is a destructive effect and can cause permanent damage on the devices.

SEGR is expected to occur in MOSFETs operating with supply voltage higher than 100 V [46]. Therefore, it is not expected to take place during the normal operation of the RCU2, whose supply voltage is only 4.3 V and 3.3 V.

#### **Single Event Functional Interrupt (SEFI)**

Soft errors are non-destructive errors induced by a single energetic particle strike, which includes SEU, MBU, SET (if latched) and non-destructive SEL [33]. SEFI is defined as the reset, the lock-up, or the detectable malfunctions caused by a soft error on electronic components [33]. In case a SEFI occurs, the component will usually restore its operability automatically. Notably, a SEFI is usually related to the SEUs in the control elements of the components, and the underlying reasons for a SEFI can be difficult to find due to the complexity of the devices involved.

On the SF2, the components that have been tested in this thesis are the phase-locked loop (PLL) [49] and the MSS. For the PLL, lock signal was used as the monitor. For the MSS, SEFI was identified through observing the operating status of the software running on it. The tests for SEFI in the PLLs and the MSS are discussed in section 4.2.5 and section 4.4.2, respectively.

As discussed in the above sub-sections, hardware interfaces of the RCU2 are also expected to suffer SEFIs. Therefore, corresponding tests have been performed (section 4.3) in this thesis. In these tests, SEFIs were identified through observing the functionalities of these interfaces.

# 2.2.3 Total Ionizing Dose (TID) effect

All the electronic components in a radiation environment are expected to absorb a dose during their life-time. Any device that is sensitive to TID effect is expected to fail if it has been exposed to the maximum limitation. As a flash-based FPGA, the SF2 is potentially sensitive to TID effects [40] [47], which may appear in two parts:

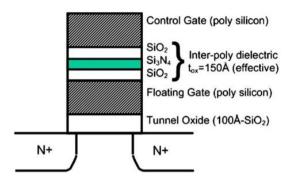

Figure 2-2 Structure of floating gate transistor in flash-based FPGA [47]

In the floating gate: Charge loss in the floating gate will lead to the shift of the threshold voltage and then the flips of stored bits [50]. Figure 2-2 demonstrates a typical flash structure, in which the bit value is stored as a charge on the floating gate. Electron-hole pairs are initiated while highly ionized particles passing through the transistors. There are three factors that reduces the threshold voltage of the floating gate [50] [51]: (1) injection of holes into the floating gate, (2) trapping of holes into the tunnel oxide and (3) emission of electrons over the poly-silicon/oxide barriers.

In the CMOS transistors: In the CMOS transistors, charges are progressively built up in the bulk of the oxides and the Si-SiO2 interfaces due to the trapping of holes. Screening or enhancing of the charges in the gate electric field of the transistors lead to the shift of threshold voltage and the increase of leakage current. In the recent technology with thin oxide where transistors are isolated from each other, the trapped holes can invert the interface at the edges of the transistors, then create open leakage paths between the drain and the source or between adjacent devices [47]. Radiation sensitivity of the CMOS transistors is in positive proportion to the thickness of the oxide due the capability of trapping holes.

In flash-based FPGAs, the charge pump, which provides a higher programming voltage, is the block that is most vulnerable to TID effect, because it has high operation-voltage and uses the transistors with thick oxide [48]. Therefore, in this thesis TID effect on the SF2 has been characterized in terms of functionality and programmability (section 4.2.6).

TID effects of the hardware interfaces is not a concern, since the commercial CMOS components could stand a dose in the order of 10 krad [39], which is higher than the total dose (a few krads) that the RCU2 is expected to absorb in Run2.

# 2.2.4 Summary

Both the SF2 and the hardware interfaces on the RCU2 are expected to suffer radiation effects in the TPC. For the SF2, the following radiation effects should be considered: (1) SEU in the SRAMs and the flip-flops, (2) SEFI in the MSS and the PLLs, (3) SEL of the FPGA and (4) TID effects of the whole SF2 chip. For the hardware interfaces, the sensitivity of SEFI should be investigated.

### 2.3 Irradiation tests

The radiation tolerance of the RCU2 is evaluated through a set of irradiation tests. Selecting a proper test facility is the prerequisite to ensure the reliability of these tests. For SEEs, the rates of occurrence extracted from the tests are used to predict the corresponding error rate in Run2. For TID effects, the SF2 is exposed to a certain amount of dose and then checked in terms of functionality and re-programmability. This section discusses how to select the test facilities, how to calculate the dose and how to estimate the rate of SEE induced errors.

## 2.3.1 Selection of test facilities<sup>12</sup>

Different kinds of radiation effects should be tested with different radiation sources. For the SEEs testing, mono-energetic proton beams with energy over 60 MeV can be used. While testing for SEL, mono-energetic proton beams with the energy higher than 200 MeV is recommended. The proton

<sup>&</sup>lt;sup>12</sup> Most of the recommendations regarding how to select test facility are from [54].

beams are good candidates because they are widely provided by many facilities. The reason for preferring mono-energetic beams is that the cross-section can be measured at a precise value of energy. For testing the TID effects, a <sup>60</sup>CO source is commonly used. Due to the limited number of test devices and time-slots, in our campaigns, the SEEs, the SEL and the TID effects need to be tested simultaneously. In this case, mono-energetic proton beams of 60 to 200 MeV can be used as the radiation source.

All the major tests were performed at the Svedberg Laboratory in Uppsala [52], with a mono-energetic proton beam of 180 MeV. In addition, several preliminary tests were carried out at the Oslo Cyclotron [53], with a mono-energetic proton beam of 25 MeV. The tests at the Oslo Cyclotron were intended to make a first screening of the candidate components. In addition, one supplementary test was performed at Nuclear Physics Institute [55] in Prague, with a mono-energetic proton beam of 35 MeV. The results of these test are discussed in detail.

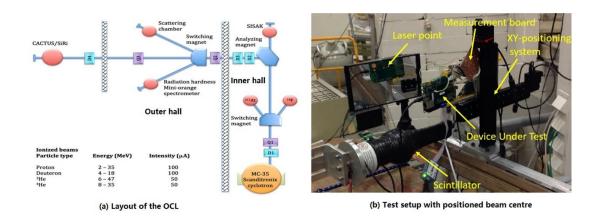

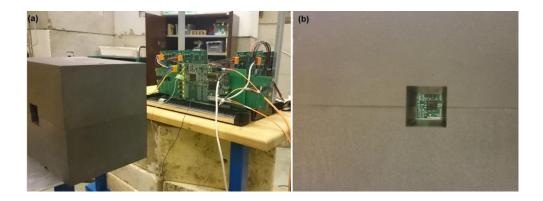

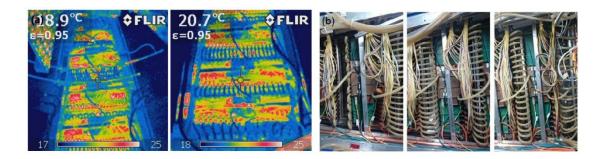

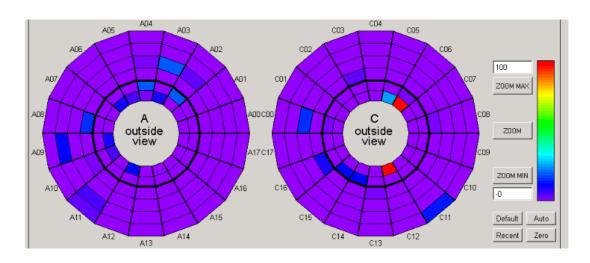

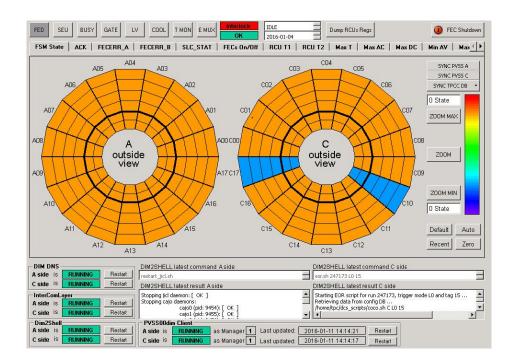

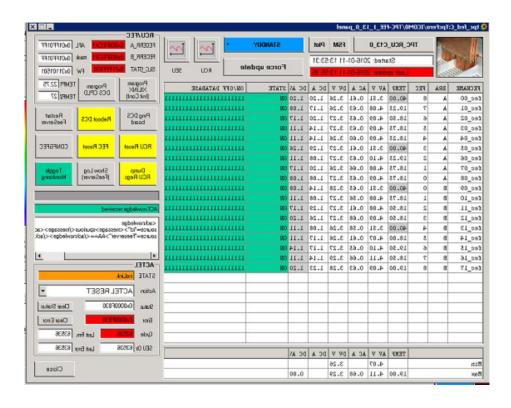

Figure 2-3 Test facility of the Oslo Cyclotron. (a) Layout of the Oslo Cyclotron [53]. (b) Test setup and positioned beam center.

#### The Oslo Cyclotron

The Oslo Cyclotron is operated by the Department of Physics, University of Oslo. It is an accelerator in Norway that provides ionized particles for basic research. The Oslo Cyclotron can accelerate protons to the range from 2 MeV to 35 MeV. In our tests, a proton beam of ~25 MeV was used to irradiate the devices. Subfigure (a) of Figure 2-3 shows the layout of the Oslo Cyclotron, which includes the inner hall, where the MC-35 cyclotron is located, the outer hall, where the electronics are tested. Before performing the tests, the central position of the beam needs to be found in two

steps. Firstly, radiation films are exposed so that spread of the beam can be seen according to the area turned black. Afterwards, a radiation monitor<sup>13</sup> connecting to a X-Y positioning system is moved within the area of the beam spot to find the position (beam center) where highest number of SEUs is produced (referred to the counts on the scintillator<sup>14</sup> locating at fixed position). Subfigure (b) of Figure 2-3 demonstrates an example setup at the Oslo Cyclotron, in which the beam center is pointed by a laser on the reflection of the devices in a mirror.

Figure 2-4 Test facility of the Svedberg Laboratory. (a) Layout of the test area [52]. (b) Setup of our test.

### The Svedberg Laboratory

The Svedberg Laboratory is operated by the Uppsala University in Sweden. With the Gustaf Werner cyclotron, it provides a proton beam ranging from 20 MeV to 180 MeV, with a beam spot diameter from 0.4 cm to 20 cm. The beam from the cyclotron is controlled to exit into the blue hall where the electronics are tested. The devices were exposed to the proton beam of ~180 MeV in our test. In contrast to the Oslo Cyclotron, beam dosimetry service, including calibration of the beam, is provided by the Svedberg Laboratory. Subfigure (a) of Figure 2-4 shows the layout of the test area. Subfigure (b) of Figure 2-4 shows the setup of the system level irradiation tests (discussed in section 4.4).

<sup>&</sup>lt;sup>13</sup> Details regarding the radiation monitor can be found in [56].

<sup>&</sup>lt;sup>14</sup> Details regarding scintillation counts can be found in [57].

## 2.3.2 Dose calculation

LET  $(dE/d_x)$  is used to calculate the dose received by the tested devices. While passing through the devices, the proton beam transfers part of its energy to the material. The energy transfer  $(\Delta E_{beam})$  can be calculated with equation 2.4, where  $\rho_{silicon}$  is the density of the silicon,  $dE/d_{x\_silicon}$  is the LET of proton in silicon and  $dx\_silicon$  is length of particle path in the silicon.

$$\Delta E_{beam} = (\rho_{silicon} * \frac{dE}{dx \ silicon} (E_{beam}) * dx\_silicon) \ [MeV]$$

(2.4)

Because the beam continuously loses energy along its path, the LET of the beam keeps increasing. However, for a short path as in the devices, these changes on the LET can be neglected. Therefore, equation 2.4 gives an approximation that is close enough to the real value.

As mentioned above, dose is defined as the total energy deposited on per unit mass of the device. Since fluence stands for the total number of particles hit per unit area of the device, the total energy transferred by the protons can be calculated as  $\Delta E_{beam}$  multiplies the fluence; multiplies the area of the device ( $A_{surface}$ ). Therefore, dose can be simply calculated with equation 2.5, where numerator is the total energy deposited by the beam, and denominator is the mass of the device. Assuming that all the protons pass through the device vertically, length of the path can be treated the same as the thickness of the silicon.

$$Dose\left(Si\right) = \frac{\frac{dE}{dx}(E_{beam})* \rho_{silicon}*dx*fluence*A_{surface}}{A_{surface}*d_{thick}*\rho_{silicon}} \approx \frac{dE}{dx_{silicon}}(E_{beam})*fluence\left[\frac{MeV}{mg}\right] \ (2.5)$$

The SI-unit of dose is Gray (Gy) [41], which is 1 Joule of energy absorbed in a kilogram of matter (J/kg). When it comes to radiation of electronics, another unit that is often used is radiation absorbed dose (rad) [41]. The relation between Gy and rad can be seen in equation 2.6 [41].

$$1 Gy = 1 \frac{J}{kq} = 100 \text{ rad } (2.6)$$

$$1 \frac{MeV}{mg} = \frac{1.602E - 13 J}{1E - 6 kg} = 1.602E - 7 \text{ Gy} = 1.602E - 5 \text{ rad } (2.7)$$

Equation 2.7 presents the conversion from  $\frac{MeV}{mg}$  to rad. Hence, equation 2.5 can be transformed into

equation 2.8, which is used to calculate dose in this thesis.

$$Dose(Si) = 1.602 * 10^{-5} * \frac{dE}{dx_{silicon}} (E_{beam}) * fluence [rad]$$

(2.8)

# 2.3.3 Predicating the rate of SEEs induced errors

In the irradiation campaigns, the tested device is exposed to a certain fluence and the number of experienced SEE induced errors ( $N_{SEE}$ ) are counted. Device sensitivity to SEEs is characterized as cross-section (CS), which is the probability that a particle strike will induce SEE. The cross-section is calculated by dividing  $N_{SEE}$  with fluence, as given by equation 2.9 [33],

$$CS_{\text{device}} = \frac{N_{\text{SEE}}}{\text{fluence}} = \frac{N_{\text{SEE}}}{\text{flux*time}} \left[ \text{cm}^2 / \text{device} \right]$$

(2.9)

where the fluence can be simplified to time multiplied by flux for a stable radiation environment (e.g. TPC and test facility).

The uncertainty of the cross-section ( $\sigma_{CS}$ ) is dependent on uncertainty of the  $N_{SEE}$  ( $\sigma_{N_{SEE}}$ ) and the fluence ( $\sigma_{fluence}$ ). Since the SEEs are random in time and linearly depends on the number of incoming particles,  $\sigma_{N_{SEE}}$  can be given by Poisson distribution ( $1/\sqrt{N_{SEE}}$ ). The  $\sigma_{fluence}$  depends on the method of fluence calculation that is used in each irradiation campaign (Appendix C). Hence, the  $\sigma_{CS}$  can be calculated with equation 2.10 [29].

$$\sigma_{CS} = \sqrt{(\frac{1}{\sqrt{N_{SEE}}})^2 + \sigma^2_{fluence}}$$

(2.10)

To characterize and evaluate the radiation tolerance of the tested devices, the MTBF in Run2 of different types of errors need to be calculated. This can be done with equation 2.11, which is derived from equation 2.10 by setting the  $N_{\text{SEE}}$  to be 1, applying the radiation flux in Run2 and using the cross-section for certain kind of error (failures).

$$MTBF = \frac{1}{flux_{Run2}*CS_{device}}$$

(2.11)

# 3 The RCU2

The RCU2 design consists of three layers: hardware, firmware and software. The firmware has gone through three versions: the first prototype, the second prototype and the commissioning version. The author has contributed to all these versions. For the first prototype, the author studied the feasibility of porting the RCU1 design into the RCU2. For the second prototype, the author was the main contributor to the Readout Module as well as the responsible for the system integration. For the commissioning version, the author tested the firmware in hardware. The author also proposed the optimizations to improve readout speed.

This chapter starts with an overview of the RCU2, in which the hardware design, including the main FPGA that host the firmware, and the software design are described. Afterwards, the overview of the firmware design is given, where the Readout Module is discussed in more detail.

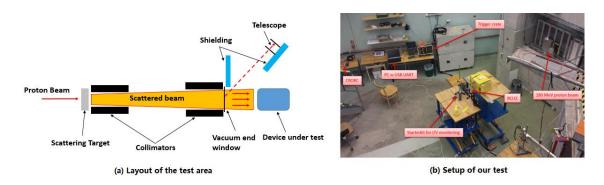

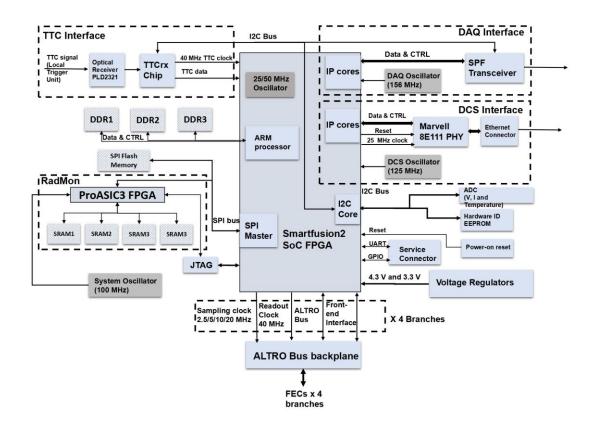

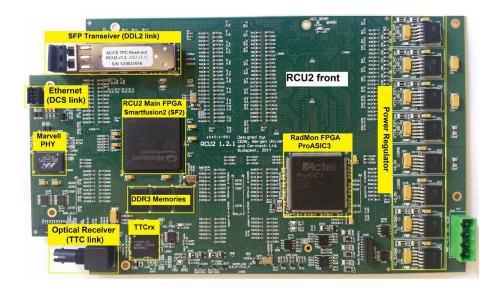

### 3.1 RCU2 overview

The development of the RCU2 was initiated in April 2013, and 216 RCU2s with new backplanes were supposed to be installed at the end of 2014, just before the start of LHC Run2<sup>15</sup>. The restricted time-frame implied that the existing TPC readout electronics needed to be reused as much as possible. All the cabling for the hardware interfaces and power supply should remain as it was for the RCU1. Besides, the RCU2 still uses the ALTRO bus to communicate with the FECs, as changing this was considered to be too ambitious imposing a high risk given the available time to finish the project. Although being similar in appearance, the RCU2 has the following major improvements with respect to the RCU1<sup>16</sup>:

- (1) The ALTRO bus is split into four branches instead of the two branches for the RCU1, which ensures at least a doubling of the readout speed.

- (2) In the RCU1, the functionalities are distributed on the three PCBs: the RCU motherboard, the SIU card, and the DCS card. The RCU2 is one single PCB which improves the operational