## UiO **Department of Physics** University of Oslo

# Single ASIC NFC Sensor Tag

Joar Digernes Særsten Master's Thesis, Spring 2016

## Abstract

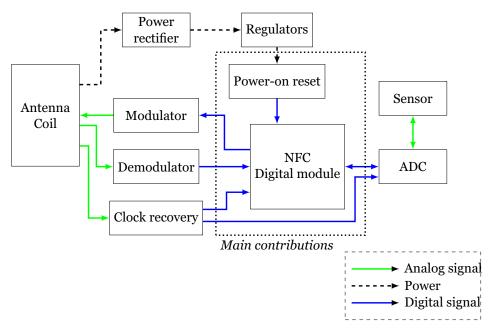

In order to use a smart phone or smart watch with the near field communication (NFC) standard to read sensor data from a micro-implant, an NFC tag with integrated ADC and sensor front-end is implemented.

An NFC digital protocol module is combined with an energy efficient front-end, ADC, energy harvester and NFC data link to form a passive NFC tag with a fully integrated and complete sensor interface.

This work builds on previous work where parts of this system have been designed and tested as standalone solutions. Previously, a sensor interface ASIC has been developed that provides the front-end to a resistive or capacitive sensor and converts its output (e.g. blood sugar concentration) into digital data ready to be transferred. Another NFC physical layer ASIC has been developed which hosts the energy harvesting and physical communication layer required to operate with an NFC enabled mobile phone, or other NFC readers. An implementation of the NFC digital protocol has been created and tested on a FPGA together with the physical communication layer and front-end and ADC. The FPGA implementation was modified further to be synthesized and combined with the two previous ASICs into a single ASIC.

A power-on reset circuit was implemented for the digital core's startup conditioning on power up.

The main contributions of this work has been to add the higher level NFC protocol control logic module as well as a power-on reset circuit, and to integrate all of these modules onto a single system-on-chip (SoC).

# Acknowledgment

First of all, I would like to thank my advisors, Dr. Ali Zaher and Prof. Philipp Häfliger, for giving me the opportunity to write my master thesis on such an interesting subject. I would also like to thank them for their advice, guidance and willingness to answer both the hard and the surprisingly simple questions that I have encountered during the process of completing this master project.

Thanks are in order to Girish Aramanekoppa Subbarao who spent much time cutting the ESD protection connections using the Focused Ion Beam machine.

I would also like to thank Olav Stanly Kyrvestad, Senior Engineer here at the Research Group for Nano electronic systems, who has been of substantial help throughout the project.

And to my fellow students at SEF, ELDAT and NANO: thanks.

Oslo, May 2016 Joar Digernes Særsten

# Contents

| Ι  | Int  | roduction                         | 19 |

|----|------|-----------------------------------|----|

| 1  | Goa  | ls for this thesis                | 21 |

| 2  | Bac  | kground                           | 23 |

|    | 2.1  | Motivation                        | 23 |

|    | 2.2  | Previous work                     | 23 |

|    | 2.3  | NFC-A tag type 1                  | 24 |

|    |      | 2.3.1 Tag to reader communication | 24 |

|    |      | 2.3.2 Reader to tag communication | 25 |

|    |      | 2.3.3 Commands                    | 26 |

|    |      | 2.3.4 Waking a tag                | 28 |

|    |      | 2.3.5 Cyclic Redundancy Check     | 28 |

|    | 2.4  | Front-end and ADC                 | 28 |

|    |      | 2.4.1 ADC                         | 28 |

|    |      | 2.4.2 Front end                   | 29 |

|    |      | 2.4.3 ADC interface               | 30 |

|    |      | 2.4.4 Converted data ready signal | 30 |

|    | 2.5  | Power harvesting                  | 30 |

|    | 2.6  | Clock Extraction                  | 31 |

|    | 2.7  | Demodulator                       | 31 |

| II | Pr   | oject                             | 33 |

| 3  | Digi | ital Design                       | 37 |

|    | 3.1  | Central control module            | 38 |

|    |      | 3.1.1 Clock divider               | 38 |

|    | 3.2  | Receiving Cyclic Redundancy Check | 40 |

|    | 3.3  | Transmit Cyclic Redundancy Check  | 40 |

|    | 3.4  | Transmit module                   | 40 |

|    | 3.5  | Receiving Module                  |    |

|    | 3.6  | Reading ADC data                  |    |

|    | -    | 3.6.1 Sensor read procedure       |    |

|    | 3.7  | Logic synthesis                   | 45 |

| 4  | Ana | alog Design                                                              | 47       |

|----|-----|--------------------------------------------------------------------------|----------|

|    | 4.1 | ADC                                                                      | 47       |

|    | 4.2 | ADC module interconnection                                               | • /      |

|    | 4.3 | Modulating transistor                                                    | 47       |

|    | 4.4 | Power-on reset circuit                                                   | 49       |

|    | 4.5 | Power harvester                                                          |          |

|    | 4.6 | Voltage regulator for the digital core                                   | 51       |

| 5  | Sys | tem Integration                                                          | 55       |

|    | 5.1 | Connecting the modules together                                          |          |

|    | 5.2 | Complete pin diagram                                                     |          |

|    | 5.3 | Produced chip                                                            |          |

|    | 5.4 | ESD clamp orientation error                                              |          |

|    |     | 5.4.1 ESD diode connection cutting                                       | 61       |

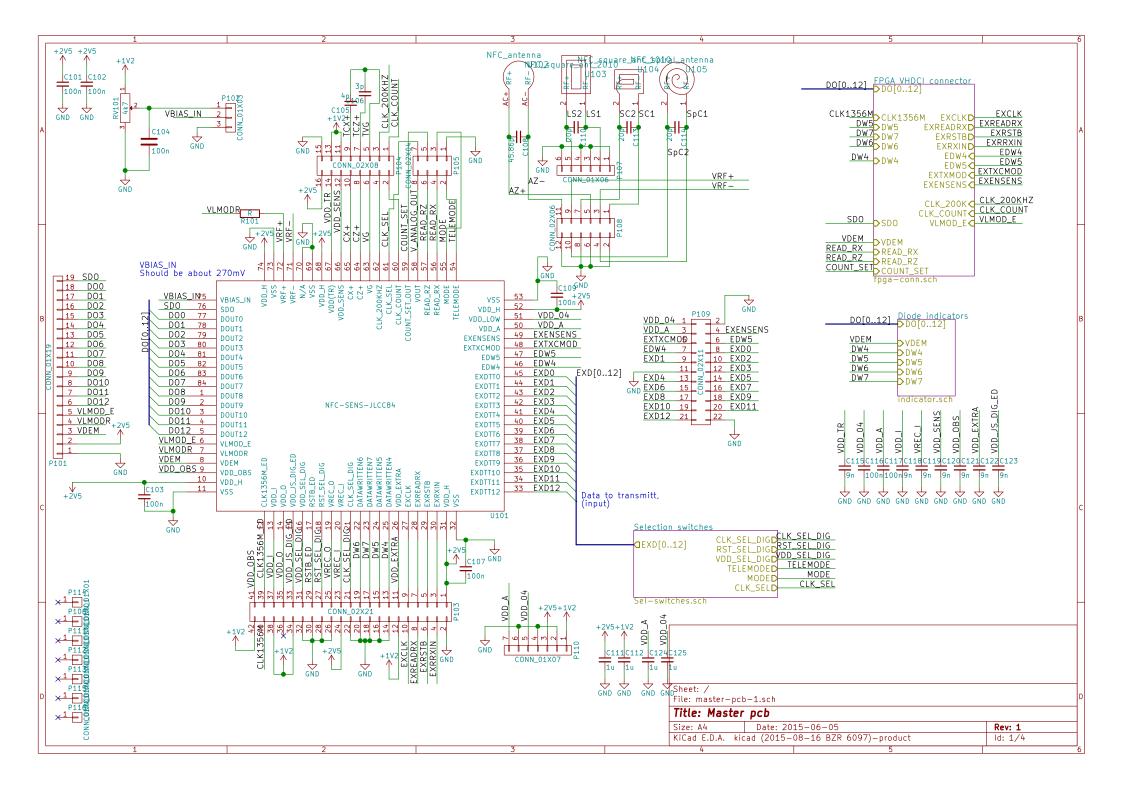

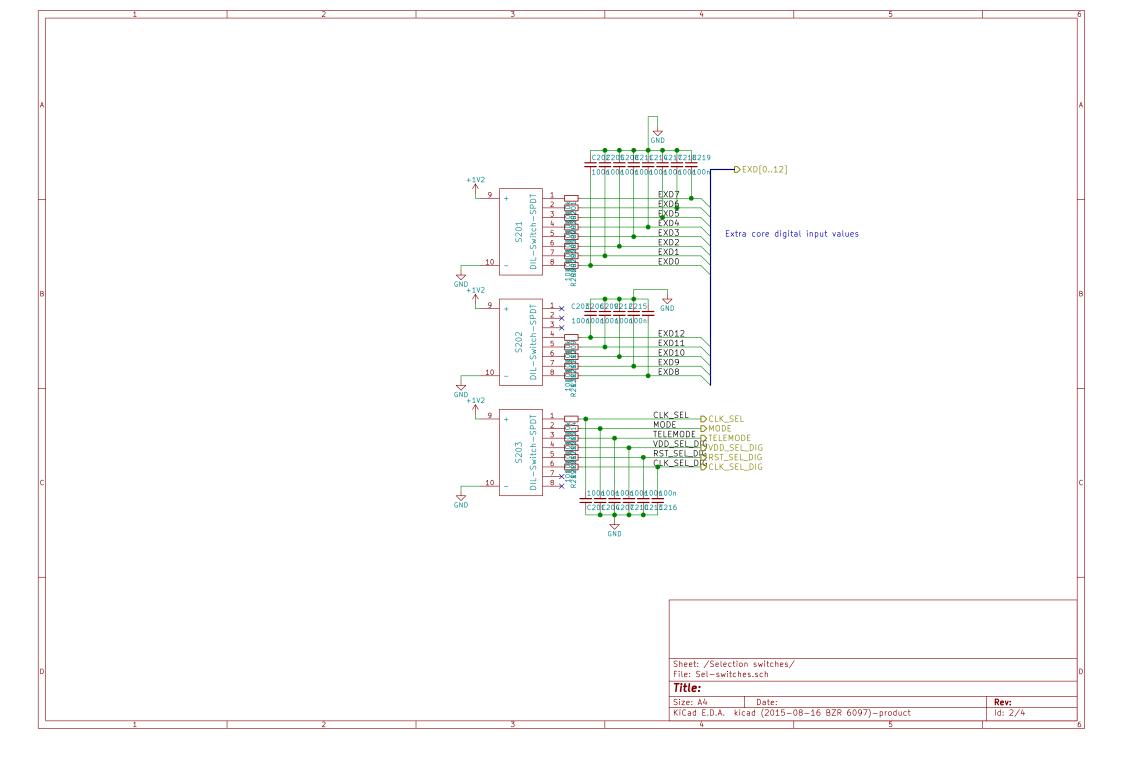

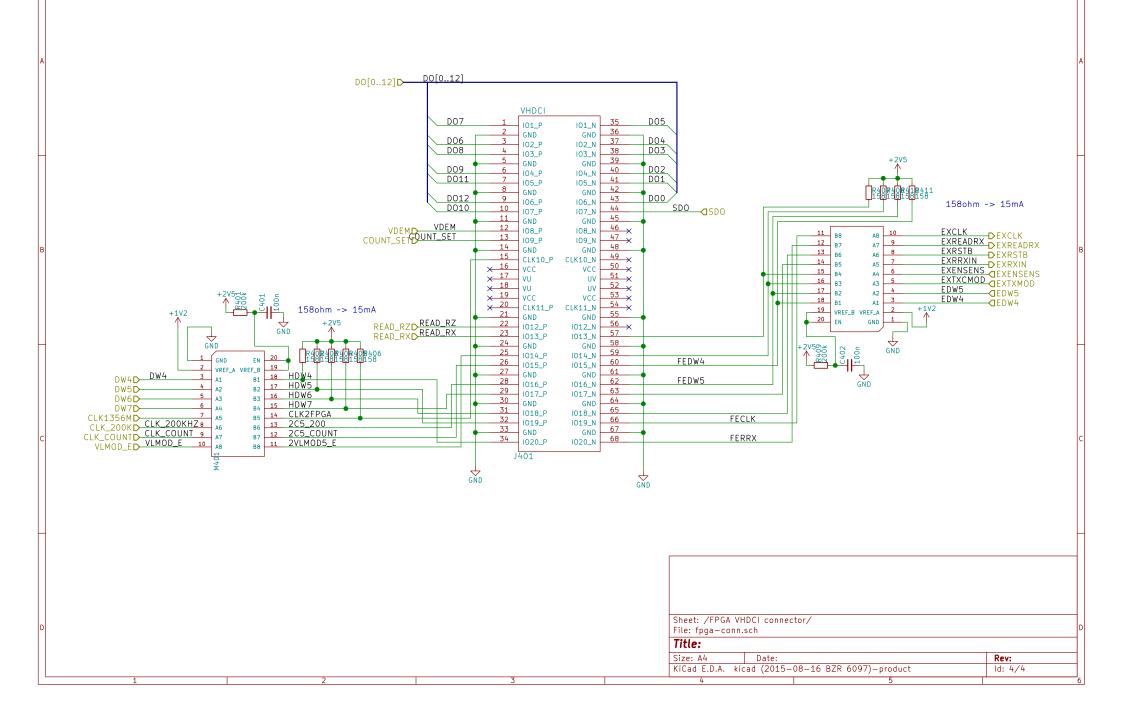

| 6  |     | t Board                                                                  | 63       |

|    | 6.1 | VHDCI connector                                                          | •        |

|    | 6.2 | Indicators                                                               | •        |

|    | 6.3 |                                                                          | · ·      |

|    | 6.4 | NFC Antenna/Inductive receiver                                           | 65       |

| П  | ΙN  | Ieasurements and Results                                                 | 67       |

|    |     |                                                                          | ,        |

| 7  |     | C Measurements                                                           | 69       |

|    | 7.1 | Bad ESD protection                                                       | -        |

|    | 7.2 | Extra digital core functionalityExtra digital core's current consumption |          |

|    | 7.3 | 7.3.1 Static current                                                     | 74<br>74 |

|    |     | 7.3.2 With clock                                                         | 74<br>74 |

|    |     | 7.3.3 EXRXIN receiving REQA command                                      |          |

|    |     | 7.3.4 EXRXIN receiving REQA and subsequently RID                         | /0       |

|    |     | command                                                                  | 76       |

|    |     | 7.3.5 EXRXIN receiving REQA and subsequently READ                        | ,        |

|    |     | ALL command                                                              | 76       |

|    | 7.4 | Reading digital inputs                                                   |          |

|    |     | 7.4.1 Write erase command with special address oxoE                      |          |

|    | 7.5 | POR circuit delay measurements                                           |          |

|    | 7.6 | Clock Extraction Measurement                                             |          |

|    | 7.7 | Testing the Demodulation Module                                          |          |

|    | 7.8 | Extra core connected to Demodulation and clock recovery                  | 88       |

| п  |     | on alusion and Eutrino Manle                                             | 01       |

| 11 |     | onclusion and Future Work                                                | 91       |

| 8  | Dis | cussion                                                                  | 93       |

|    | 0.  | 8.0.1 Challenges                                                         |          |

|    | 8.1 | Conclusion                                                               |          |

|    | 8.2 | Possible applications                                                    | 94       |

### 8

| 8.3 | Future work | • | • | • | • |  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | ç | <b>)</b> 5 |

|-----|-------------|---|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------------|

|     |             |   |   |   |   |  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |            |

### **V** Appendices

# **List of Figures**

| 2.1  | Tag to reader frame format. Eof is End of frame, SoF is Start                                                                   |     |   |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|---|

|      | of Frame                                                                                                                        | 25  | 5 |

| 2.2  | Reader to tag frame format                                                                                                      | 27  | 7 |

| 2.3  | WUPA poll modulation waveform                                                                                                   | 28  | 3 |

| 2.4  | ADC top level schematic interface overview                                                                                      | 29  | 9 |

| 2.5  | Capacitive and resistive sensor ADC connections. Subscript                                                                      |     |   |

|      | S denotes sensor, R denotes reference                                                                                           | 29  | 9 |

| 2.6  | Timing diagram, from simulated VHDL model, demonstrat-                                                                          |     |   |

|      | ing ADC readout procedure. Demonstrating the out of place                                                                       |     |   |

|      | reset occurring after a data ready signal (read_rx), and why                                                                    |     |   |

|      | care needs to be taken to ensure data is correctly read                                                                         | 30  | ) |

| 2.7  | Single voltage rectifier element schematic.                                                                                     | 3   | 1 |

| 2.8  | Clock recovery circuit                                                                                                          | 3   | 1 |

| 2.9  | Demodulation circuit, as presented in [22]                                                                                      | 32  | 2 |

| 2.10 | Full system module and inter-connection overview                                                                                | 35  | 5 |

| ~ .  |                                                                                                                                 |     |   |

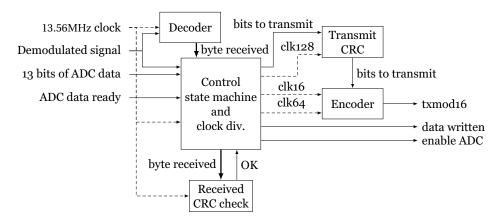

| 3.1  | Digital core topology and important signal interconnects                                                                        | 37  | 7 |

| 3.2  | State diagram describing how commands received change                                                                           |     |   |

|      | the tag's operation and that after each response it returns to the READY state.                                                 | 0.0 | ~ |

| 0.0  |                                                                                                                                 | 39  | J |

| 3.3  | Receiving module state diagram. <i>cnt</i> is a counter counting cycles between received modulated signal lows. <i>i</i> is an  |     |   |

|      | cycles between received modulated signal lows. <i>i</i> is an indexing variable. <i>bits</i> is a register holding decoded bits | 4.0 | • |

| 0.4  | Procedure for reading a sensor using the tag and how the tag                                                                    | 42  | 2 |

| 3.4  | behaves in turn. <i>Timescale not comparable</i>                                                                                |     | 4 |

| 0 5  | ADC clock enable diagram, as the tag sees it.                                                                                   | -   |   |

| 3.5  | Simplified synthesis process overview                                                                                           |     |   |

| 3.6  | Simplified synthesis process overview                                                                                           | 45  | ) |

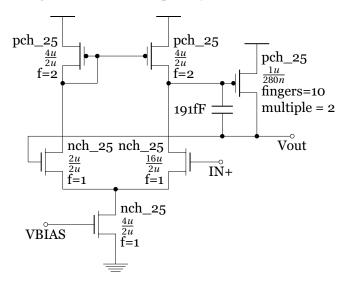

| 4.1  | ENABLE_SENS controls whether a clock signal should feed                                                                         |     |   |

| •    | through to the ADC or not. Note that the clock output is                                                                        |     |   |

|      | not 200kHz as the label implies, but rather 211.88kHz, under                                                                    |     |   |

|      | normal operation.                                                                                                               | 49  | 9 |

| 4.2  | N channel transistor 2.5V version, shown with labels indicat-                                                                   |     |   |

|      | ing its size and connection to the antenna coil, VLMODR is                                                                      |     |   |

|      | connected, through a resistor off chip, back to VAC- termi-                                                                     |     |   |

|      | nal on the coil.                                                                                                                | 49  | ) |

| 4.3  | Schematic of test bench for modulation transistor                                                                               | -   | ) |

| 4.4  | Schematic of POR delay element circuit from [2]                                                                                 | 50  | ) |

| 4.5                                                                         | Schematic of four POR elements cascaded with a buffer to create a POR circuit                                                                                                                                                                                                     | 51                         |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 4.6                                                                         | Simulated delay of four POR elements cascaded as is shown<br>in Figure 4.5, with added components simulating how the<br>circuit would be measured on chip. Delay is from input to                                                                                                 |                            |

| 4.7                                                                         | output level passing their relative percentage threshold<br>Antenna/coil input diode overvoltage protection/voltage<br>clamp                                                                                                                                                      | 52<br>52                   |

| 4.8                                                                         | Schematic of regulator for digital core                                                                                                                                                                                                                                           | 52<br>53                   |

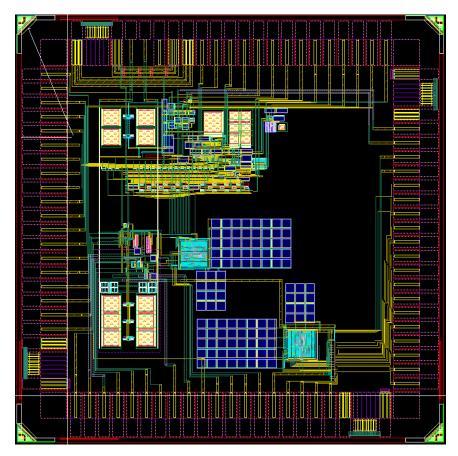

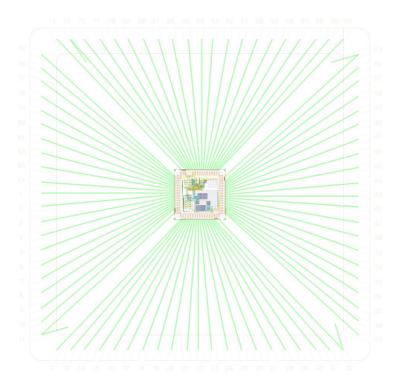

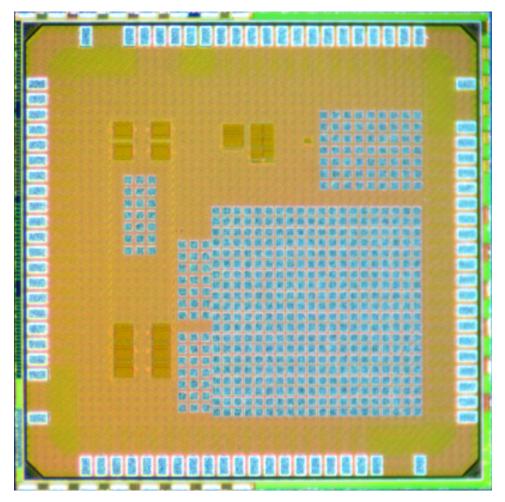

| 5.1                                                                         | Chip layout with pad frame.                                                                                                                                                                                                                                                       | 56                         |

| 5.2                                                                         | Bonding diagram                                                                                                                                                                                                                                                                   | 57                         |

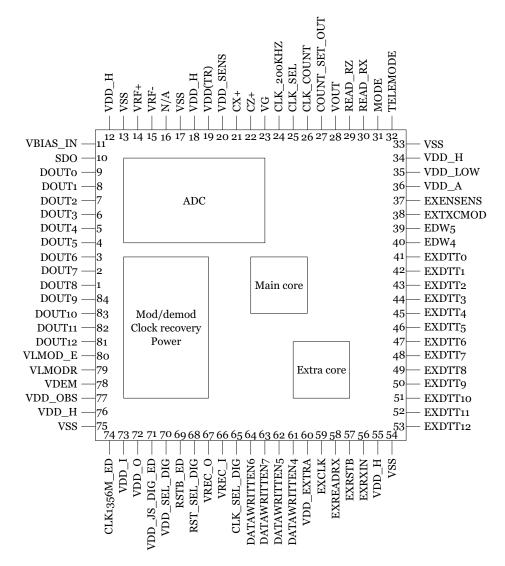

| 5.3                                                                         | Chip package IO pin layout                                                                                                                                                                                                                                                        | 58                         |

| 5.4                                                                         | Image of chip die, captured with microscope                                                                                                                                                                                                                                       | 59                         |

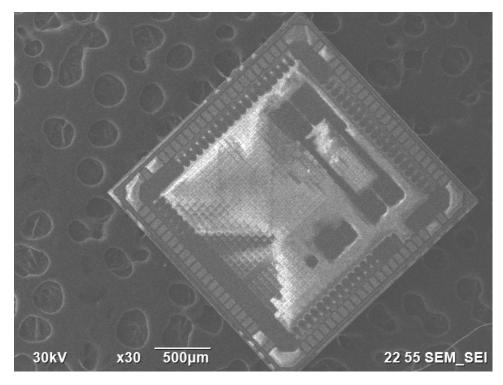

| 5.5                                                                         | Electron microscope image of full chip                                                                                                                                                                                                                                            | 60                         |

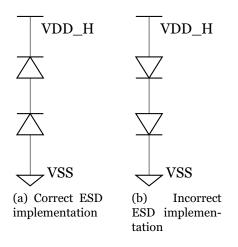

| 5.6                                                                         | Correct and incorrect ESD protection implementation. Sim-                                                                                                                                                                                                                         |                            |

|                                                                             | plified                                                                                                                                                                                                                                                                           | 60                         |

|                                                                             | <ul><li>(a) Pad frame ESD protecting diode implementation</li><li>(b) Pad frame ESD protecting diode implementation ori-</li></ul>                                                                                                                                                | 60                         |

|                                                                             | ented incorrectly                                                                                                                                                                                                                                                                 | 60                         |

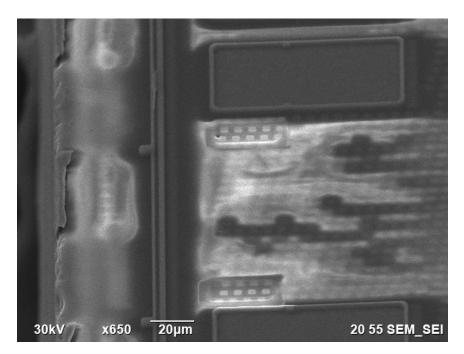

| 5.7                                                                         | Electron microscope image of ESD diode after ion beam has cut connecting metal lines                                                                                                                                                                                              | 62                         |

|                                                                             |                                                                                                                                                                                                                                                                                   |                            |

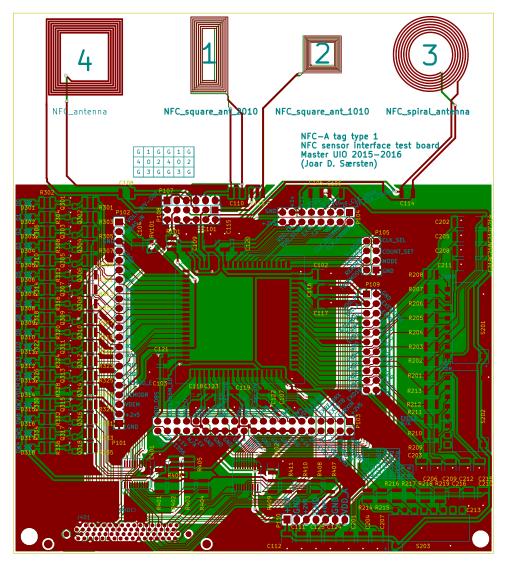

| 6.1                                                                         | Test PCB lavout                                                                                                                                                                                                                                                                   | 63                         |

| 6.1<br>6.2                                                                  | Test PCB layout                                                                                                                                                                                                                                                                   | 63<br>66                   |

| 6.2                                                                         | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing. | 63<br>66                   |

|                                                                             | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing  | 66                         |

| 6.2                                                                         | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing  | 66                         |

| <ul><li>6.2</li><li>7.1</li></ul>                                           | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing  | 66<br>69                   |

| <ul><li>6.2</li><li>7.1</li><li>7.2</li></ul>                               | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing  | 66<br>69                   |

| <ul><li>6.2</li><li>7.1</li><li>7.2</li></ul>                               | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing  | 66<br>69<br>70             |

| <ul><li>6.2</li><li>7.1</li><li>7.2</li><li>7.3</li></ul>                   | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing  | 66<br>69<br>70<br>71       |

| <ul> <li>6.2</li> <li>7.1</li> <li>7.2</li> <li>7.3</li> <li>7.4</li> </ul> | Header pin description for selecting an active antenna.<br>Position 0 is connected to the chip, $1 \rightarrow 4$ are connected to<br>marked antennas on the board, while "G" indicates a ground<br>connection. Using a simple jumper an antenna can be chosen<br>during testing  | 66<br>69<br>70<br>71<br>72 |

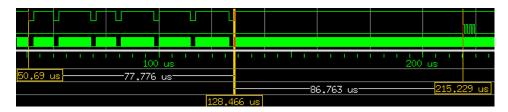

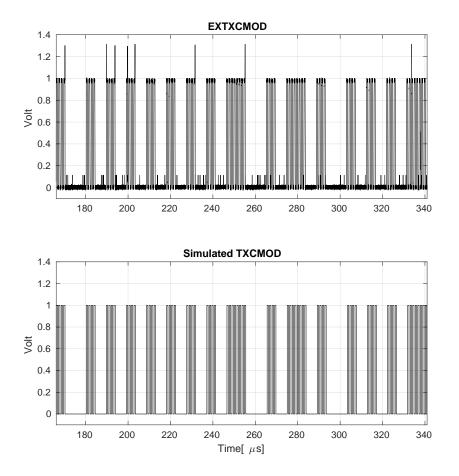

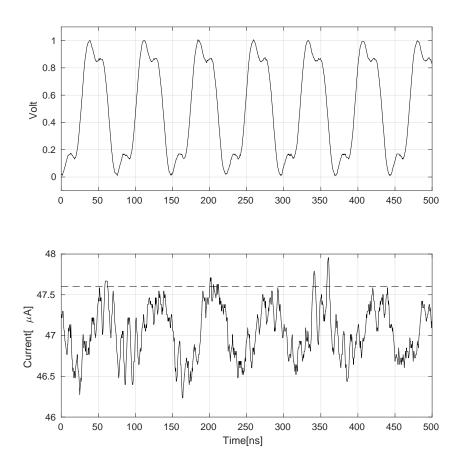

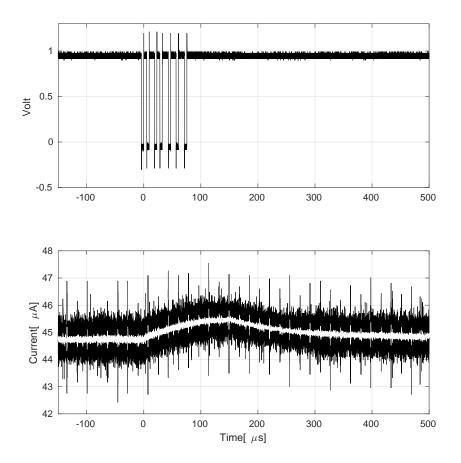

| 7.7  | Current consumption of chip while REQA command is                    |    |

|------|----------------------------------------------------------------------|----|

|      | received. The white line in the middle of the current plot           |    |

|      | is the result of a moving average of 200 points over the wave        |    |

|      | that enclose it.                                                     | 77 |

| 7.8  | Current consumption during REQA command receipt and                  |    |

|      | the extra core's ATQA response on EXTXCMOD pin.                      |    |

|      | EXRXIN on top left interrupted by EXTXCMOD top right.                |    |

|      | Current consumption bottom, with dashed line showing                 |    |

|      | current measured with voltage source between commands.               |    |

|      | White line in middle of current consumption is a moving av-          |    |

|      | erage over 200 values.                                               | 78 |

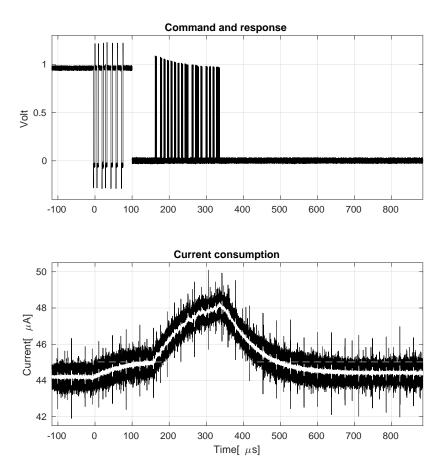

| 7.9  | Current consumption during REQA and RID command and                  |    |

|      | response output on EXTXCMOD pin. White line in middle                |    |

|      | of current consumption is a moving average over 200 values.          | 79 |

| 7.10 | Current consumption during REQA and RALL command re-                 |    |

|      | ceiving and its READ ALL response output on EXTXCMOD                 |    |

|      | pin. White line in middle of current consumption is a moving         |    |

|      | average over 200 values                                              | 80 |

| 7.11 |                                                                      |    |

|      | command on special address oxoE                                      | 82 |

| 7.12 | Reading out two bytes from registers holding read data input         |    |

|      | values. Here address 0 <i>x</i> 0 <i>D</i> and 0 <i>x</i> 0 <i>E</i> | 83 |

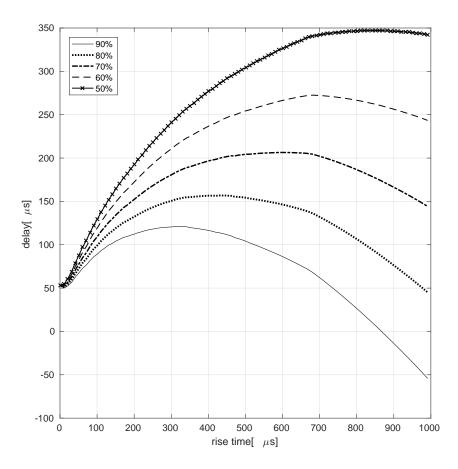

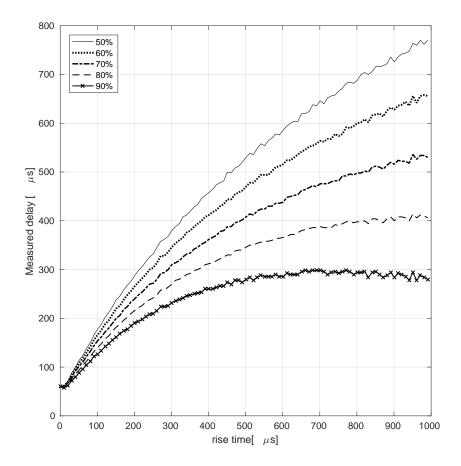

| 7.13 | Measured delay time POR circuit in fabricated ASIC. Shows            |    |

|      | relation between delay time and rise time of an expressed            |    |

|      | pulse acting as a voltage source on digital voltage input            | 85 |

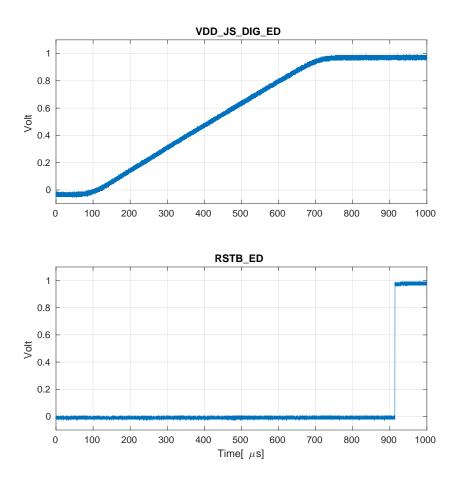

| 7.14 | First flank of a POR delayed RESETB signal as measured               |    |

|      | on RSTB_ED. Rise time for the square wave set to 500µs,              |    |

|      | expressed on pin VDD_JS_DIG_ED. Shows how the active-                |    |

|      | low reset trails the input voltage                                   | 86 |

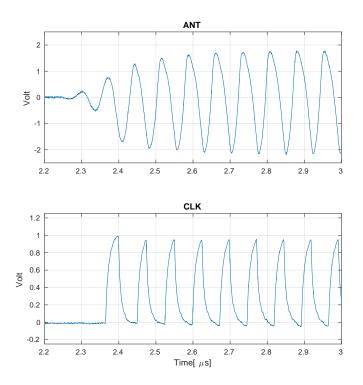

| 7.15 | Clock extraction from induced wave from an NFC reader                |    |

|      | with external power for clock recovery and buffers                   | 87 |

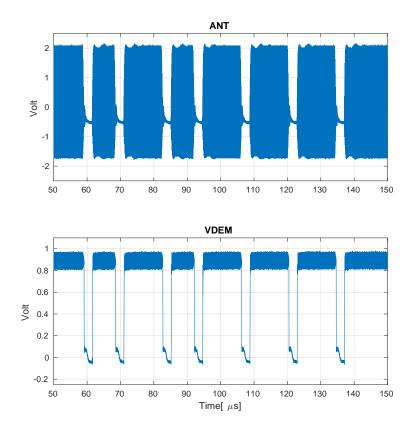

| 7.16 | Recovered antenna carrier wave and demodulated signal.               |    |

|      | Demonstrating the functionality of the demodulation circuit.         |    |

|      | That is demodulating a signal from a smart phone acting as           |    |

|      | a NFC reader                                                         | 88 |

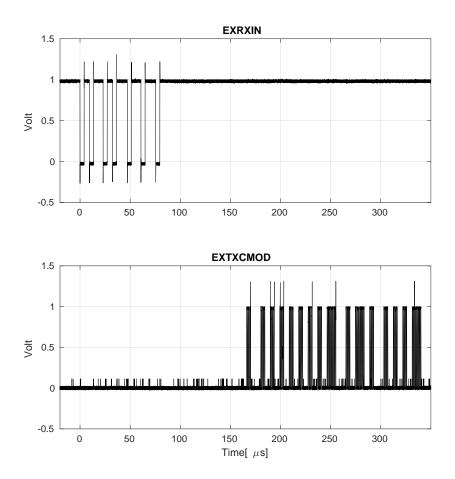

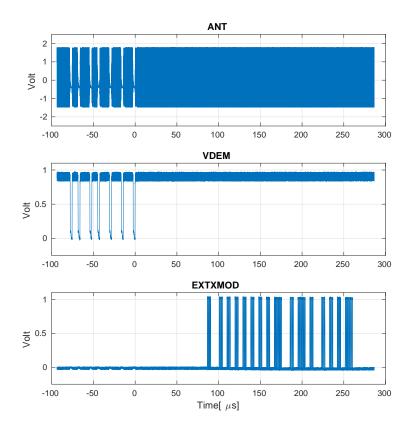

| 7.17 | Clock recovery and demodulation connected to extra core.             |    |

|      | Demonstrating a correct response, ATQA, to the REQA                  |    |

|      | command sent by a NFC reader, here a smartphone of type              |    |

|      | LG P800                                                              | 90 |

# **List of Tables**

| 2.1<br>2.2 | Tag to reader bit encoding, from [3]. Subcarrier is $\frac{f_c}{16} \approx 847$ kHz<br>Poll→Listen pattern modulation, as per [8]. $f_c$ is the carrier | 24 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2        | frequency, typically 13.56MHz                                                                                                                            | 25 |

| 2.3        | Poll $\rightarrow$ Listen bit encoding, based on previous bit value. Start                                                                               | -5 |

| 5          | of Frame (SoF) indicates to a tag that a frame follows.                                                                                                  | 26 |

| 2.4        | Poll→Listen pattern decoding. Start of Frame (SoF) indi-                                                                                                 | _0 |

|            | cates to a tag that a frame follows.                                                                                                                     | 26 |

| 2.5        | Reader(poll) to tag(Listen) commands[8, 17]                                                                                                              | 27 |

| 2.6        | ATAQ response                                                                                                                                            | 27 |

|            |                                                                                                                                                          | _, |

| 3.1        | Memory map, as it is hard coded in HDL source code. ADC value in block 2 byte 1 is reset to/default 00, but after a sensor                               |    |

|            | read event it stores a byte of the previously read ADC value.                                                                                            | 39 |

| 3.2        | Cycles used in implementation to determine different pat-                                                                                                | 39 |

|            | terns. A single bit duration is 128 cycles.                                                                                                              | 41 |

| 3.3        | Tag's sensor data registers available to <i>READ</i> command                                                                                             | 43 |

| 3.4        | Format of address operand ADD, from [17]                                                                                                                 | 43 |

| 4.1        | ADC module terminals. External means that it is accesible<br>on the outside of the chip, while internal means that it is only                            |    |

|            | accessible from the digital core                                                                                                                         | 48 |

| 6.1        | NFC inductors/antenna                                                                                                                                    | 65 |

| 7.1        | Measurement setup for REQA applied on extra core's                                                                                                       |    |

|            | EXRXIN and the response measured on EXTXCMOD                                                                                                             | 70 |

| 7.2        | Extra core's current consumption without clock signal, mea-                                                                                              |    |

|            | sured on VDD_EXTRA, other logic level pulls are handled by                                                                                               |    |

|            | other voltage sources to minimize the effect of current draw                                                                                             |    |

|            | from the wrongly oriented ESD protection diodes                                                                                                          | 74 |

| 7.3        | Clock current measurement connection setup                                                                                                               | 75 |

| 7.4        | REQA measurement connection setup                                                                                                                        | 76 |

| 7.5        | RID command and response hex values HR: Header ROM                                                                                                       |    |

|            | byte, CRC: Cyclic Redundancy Check, UID: Unique IDentifier                                                                                               | 76 |

| 7.6        | Memory readout ordered similary as EEPROM memory map                                                                                                     |    |

|            | seen in [17, page 5]. First two bytes are header ROM 0 and 1,                                                                                            |    |

|            | last to bytes are CRC bytes                                                                                                                              | 81 |

| 7.7        | Read sensor read out after a simulated sensor read, switches                                                                                             |    |

|            | in position $0x1E65$                                                                                                                                     | 84 |

| 7.8  | Measurement setup for POR circuit delay measurements                                | 84  |

|------|-------------------------------------------------------------------------------------|-----|

| 7.9  | Measurement setup for clock recovery                                                | 87  |

| 7.10 | Measurement setup for extra core connected to demodula-<br>tion and clock recovery. | 89  |

| 8.1  | BOM, ordered from Farnell, part 1 of 2                                              | 111 |

| 8.2  | BOM, ordered from Farnell, part 2 of 2                                              | 112 |

## Preface

This thesis is the result of my study for a master degree in Microelectronics at the Department of Physics, University of Oslo. I started this work spring 2015 and concluded my research spring 2016.

My interest into biological sensing implantable technology and embedded systems were the main reasons for choosing this project. A personal curiosity was to be a part of the complete process from design concept to a complete system which could interface with the real world. This specific project looked to not only be an interesting one, but one with potential future real life implementations.

Ali Zaher (my co-supervisor), Thanh Trung Nguyen, Philipp Häfliger (my main supervisor), and I published a paper called "the Integrated electronic system for implantable sensory NFC tag", seen in [22]. It is a preceding and concurrent part of this work, where the parts implemented on a single ASIC in this work are presented as separate parts of a system with a goal of a future single ASIC implementation of said system.

# Part I Introduction

# Chapter 1

# **Goals for this thesis**

- **Goal:** Demonstrating how a small implantable NFC and sensor tag is feasible for chronic disease monitoring, e.g. diabetes or high blood pressure.

- **Objective:** Design, implement and test a single passive ASIC NFC sensor tag to enable a small NFC sensing system.

#### **Scope:** – Make and test a process for digital design synthesis.

- Synthesize an NFC-A Tag type 1 digital core.

- Implement previously made sensor readout, and NFC communication and power layer modules with synthesized digital core in a single ASIC.

- Create a system which only needs an external antenna, capacitive energy storage and sensor.

- Create system testing board.

- Connect test board together with an FPGA development board and do comprehensive testing.

- Test system with commercial, commonly available, NFC reader: smartphone with NFC capability.

- Demonstrate passive tag operation, that is, no batteries or external power needed on the tag's side

- Demonstrate tag sensor read-out using an NFC reader.

## **Chapter 2**

# Background

### 2.1 Motivation

In 2006 Philipp Häfliger here at the Research Group for Nano electronic systems at the department of informatics at the University of Oslo, started as a collaboration with a medical technology company, Lifecare AS, to research a continuous and long term glucose sensor read-out. This project has been called GlucoSense.

There are an estimated 415 million people with diabetes per 2015 in the world. With conservative estimates, the global prevalence of diabetes type 1 is 29 million (7% - 12%) of diabetes cases in high-income countries are type 1). With daily insulin treatment, regular blood glucose monitoring and maintenance of a healthy diet and lifestyle, people with type 1 diabetes can lead a normal, healthy life.[6]

An implantable glucose sensor together with the NFC sensor readout tag presented in this work could reduce the need of daily blood-drop glucose measurements or weekly replacement of a percutaneous sensor.

### 2.2 Previous work

A first integrated sensor tag electronics implementation is presented in [10]. It started as a collaboration between the Research Group for Nano electronic systems, here, and Lifecare AS, a health startup.

Thanh Trung Nguyen together with Philipp Häfliger developed front end and ADC further into what is presented in [18] and [13]. [13] and [10] also uses only a single resistance divider instead of a Wheatstone bridge, while maintaining a differential input by swapping the polarity of the sensor supply source which suppresses 1/f noise since it uses correlated double sampling (CDS). The RF back-end is described in the extending paper [15]. There, a parallel to serial logic block continuously encodes read-out data as a serial bit stream, which in turn is transmit back to the reader using loadshift keying (LSK). In [12] the ADC as is implemented here is demonstrated, that is, it envisions a capacitive sensor to be measured, similarly to this project. [16] demonstrates [12] implemented in 90nm TSMC process; its layout was refitted for use in the project presented here. Ali Zaher, Aage Dahl and Thomas Peter Plagemann developed an android NFC performance testing software suite in [5]. Based on their measurement results from testing five different NFC tags, NFC-A tag type 1 was selected for further development based on its low power consumption during read and simplicity. It did have higher power consumption during write operations, but as *write* is not implemented with actual writing of bits, in this project, it should not affect the technology selection much.

In [22] Ali Zaher, Joar Særsten, Thanh Trung Nguyen and Philipp Hafliger, presents the system implemented with the three main components being two ASICs and one FPGA, which again is implemented on a single ASIC in the project presented here.

### 2.3 NFC-A tag type 1

NFC-A and its subset tag type 1, is the communication protocol used in this project.

NFC-A has two communication schemes; Reader to tag communication, poll  $\rightarrow$  listen, uses amplitude shift keying(ASK). And Tag to reader communication, listen  $\rightarrow$  poll, which modulates the load on the receiving coil, also known as load-shift keying (LSK). [8]

#### 2.3.1 Tag to reader communication

Communication from tag to a reader is accomplished with subcarrier modulation using Manchester encoding.

The tag creates the sub carrier by switching a load connected to the inductive coupling area, creating a subcarrier frequency of  $\frac{fc}{16} \approx 847$ kHz as per [3]. This subcarrier is subsequently keyed on and off according to Manchester encoding.

In Manchester encoding a binary 1 is represented by a negative transition in the half-bit period and a binary 0 is represented by a positive transition. [7, page 181] Tag to reader bit representation and Manchester encoding definitions are listed in Table 2.1 where a bit duration is  $\frac{fc}{128} \approx 106$ kHz.

Table 2.1: Tag to reader bit encoding, from [3]. Subcarrier is  $\frac{f_c}{16} \approx 847$ kHz

| Logic value            | Subcarrier modulation of carrier |

|------------------------|----------------------------------|

| 1                      | First half modulated             |

| 0                      | Second half modulated            |

| Start of communication | First half modulated             |

| End of communication   | no modulation                    |

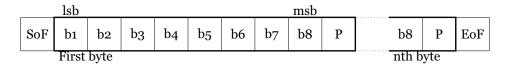

The frame format for tag to reader communication is: a start bit, data byte sent with least significant bit first, followed by an odd parity bit, repeated until an *end of frame* pattern is transmitted to signal the end of tag to reader communication. Figure 2.1 illustrates the tag to reader frame format. The *end of frame* pattern is straightforwardly defined as no modulation. [17]

Figure 2.1: Tag to reader frame format. Eof is End of frame, SoF is Start of Frame.

#### 2.3.2 Reader to tag communication

Communication from the reader to the tag is accomplished by modified miller encoding using amplitude modulation keying (ASK) of the carrier wave [8, page 15].

In normal Miller code (also known as delay encoding): A binary 1 is represented by a transition in the half-bit period; a binary 0 is represented by the continuance of the 1 level over the next bit period. A sequence of zeros creates a transition at the start of a bit period, so that the bit pulse can be more easily reconstructed in the receiver (if necessary). [7, page 181]

The encoding used here, for reader to tag communication, is a modified miller encoding scheme, where each transition is replaced by a negative pulse.

The pulses are shorter than a bit period ensures that the carrier wave is active for longer and therefore more power is transmitted during communication [7, page 181].

During ASK modulation the reader pulls the carrier amplitude down to less than 5% of its initial amplitude. These pulses lasts for a minimum of  $0.5\mu$ s or up to a maximum of  $3\mu$ s.[3]

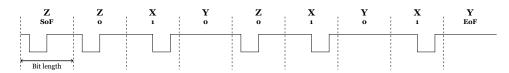

A more rigorous way of defining this modified miller encoding, as listed in [3], is to define each transition pulse type into patterns, and listing how bit values and their order determine what patterns should be expressed. There are three Poll $\rightarrow$ Listen patterns, **X**, **Z** and **Y**, they are generated based on the rules listed in Table 2.2.

Table 2.2: Poll $\rightarrow$ Listen pattern modulation, as per [8].  $f_c$  is the carrier frequency, typically 13.56MHz

|         | Bit duration  | $\operatorname{on}(\frac{128}{f_c})$ |

|---------|---------------|--------------------------------------|

| Pattern | First half    | Second half                          |

| Х       | No modulation | Modulated                            |

| Y       | No mod.       | No mod.                              |

| Z       | Modulated     | No mod.                              |

Bits are encoded into patterns using the rules listed in Table 2.3. Shortly summarized, 1s are encoded as X patterns, while os are encoded as Y and

Z patterns, where Z patterns are used for repeated zeros, Y for first and singular os. The take home message from this table should be that a Y pattern is never repeated, and only follows an X. The only instance when a Y follows a Z is after a transmission has ended, that is, no communication. The Y pattern is not really a pattern, as it involves no modulation of the carrier wave; which is also why Y pattern can indicate *end of frame* (EoF) as no modulation for subsequent bit durations means no frame is transmitted.

To indicate the start of frame (SoF), a Z pattern is expressed, this gives the tag something to coordinate its timing to, as it is always a Z pattern.

The tag (Listen device) decodes patterns according to the rules listed in Table 2.4.

Table 2.3: Poll  $\rightarrow$  Listen bit encoding, based on previous bit value. Start of Frame (SoF) indicates to a tag that a frame follows.

| Previous | current |         |

|----------|---------|---------|

| bit      | bit     | pattern |

| None     | SoF     | Ζ       |

| 1 0      | 1       | Х       |

| 0        | 0       | Ζ       |

| 1        | 0       | Y       |

|          | •       |         |

Table 2.4: Poll $\rightarrow$ Listen pattern decoding. Start of Frame (SoF) indicates to a tag that a frame follows.

| Pattern   | Interpretation |

|-----------|----------------|

| First Z   | SoF            |

| Х         | 1              |

| Z         | 0              |

| Y after X | 0              |

| Y else    | EoF            |

The frame format for reader to tag communication is what is specified in [17] and [8] under Tag type 1. NFC-A, and tag type 1, frame format uses 7-bit short frame for commands, which starts with a *start of frame* (SoF) pattern and ends with a *end of frame* (EoF) pattern. Bits are transmitted in the order of least significant bit (lsb) to most significant bit (msb).

NFC-A tag type 1 is different from NFC-A specification in that it breaks up bytes into single frames instead of sending them together as a continuous bit stream. Regular data is transmitted similarly, but instead of seven bits, all eight are transmitted. Figure 2.2 describes these two frame formats.

#### 2.3.3 Commands

Table 2.5 lists the reader commands as defined in [17] and the corresponding overlapping commands from [8].

| Short or Command Frame           |     |    |    |    |    |    |     |     |     |  |  |  |  |  |

|----------------------------------|-----|----|----|----|----|----|-----|-----|-----|--|--|--|--|--|

| SoF                              | b1  | b2 | b3 | b4 | b6 | b7 | EoF |     |     |  |  |  |  |  |

| lsb msb<br>Operand or Data Frame |     |    |    |    |    |    |     |     |     |  |  |  |  |  |

| SoF                              | b1  | b2 | b3 | b4 | b5 | b6 | b7  | b8  | EoF |  |  |  |  |  |

|                                  | lsb |    |    |    |    |    |     | msb |     |  |  |  |  |  |

1 1

01

.

$\mathbf{\alpha}$

Figure 2.2: Reader to tag frame format

Table 2.5: Reader(poll) to tag(Listen) commands[8, 17]

| NFC-A    | Topaz/Tag type 1 | Command code  | Description       |

|----------|------------------|---------------|-------------------|

| SENS_REQ | REQA             | 0 <i>x</i> 26 | Request command   |

| ALL_REQ  | WUPA             | 0 <i>x</i> 52 | Wake-up           |

|          | RID              | 0 <i>x</i> 78 | Read ID           |

|          | RALL             | 0 <i>x</i> 00 | Read All          |

|          | READ             | 0 <i>x</i> 01 | Read(Single byte) |

|          | WRITE-E          | 0 <i>x</i> 53 | Write-with-erase  |

|          | WRITE-NE         | 0x1A          | Write-no-erase    |

*REQA* and *WUPA* commands, should, from the specifications, respond with an ATQA, defined as two bytes without any checksum. The first byte, 0x00, means that the tag UID is 4 bytes long. The second byte is 0x0C, and means that the tag is of type 1 tag platform. [8] This is again explained in Table 2.6.

| First Byte: |      |     |                         |    |    |    |    |  |  |  |  |  |

|-------------|------|-----|-------------------------|----|----|----|----|--|--|--|--|--|

| b8          | b7   | b6  | b5                      | b4 | b3 | b2 | b1 |  |  |  |  |  |

| 0           | 0    | 0   | 0                       | 0  | 0  | 0  | 0  |  |  |  |  |  |

|             |      | RFU | Single device detection |    |    |    |    |  |  |  |  |  |

| 4 by        | ytes |     | type 1 tag              |    |    |    |    |  |  |  |  |  |

| Second Byte: |    |    |    |      |       |    |    |  |  |  |

|--------------|----|----|----|------|-------|----|----|--|--|--|

| b8           | b7 | b6 | b5 | b4   | b3    | b2 | b1 |  |  |  |

| 0            | 0  | 0  | 0  | 1    | 1     | 0  | 0  |  |  |  |

|              | R  | FU |    | Туре | 1 Tag | 5  |    |  |  |  |

Table 2.6: ATAQ response

Figure 2.3 demonstrated how a Wake-up (*WUPA*) command is encoded for reader to tag (poll  $\rightarrow$  listen) communication.

In this project the *WRITE-E* command is also used to enable the ADC clock. It was selected for that purpose because of its long response time at about 5.23ms. [17] Which means that the reader supplies uninterrupted

Figure 2.3: WUPA poll modulation waveform

power and clock for the whole duration, and the ADC can work without interruption during that time.

### 2.3.4 Waking a tag

A NFC-A tag, and NFC-A Tag Type 1, are woken up with a *WUPA* or *REQA* command before actual reading or writing can be done. The tag must be ready to receive one of these commands within a guard time of 5ms of unmodulated carrier wave. [8]

#### 2.3.5 Cyclic Redundancy Check

To ensure that commands and data is transmitted, and received, correctly, the NFC-A tag type 1 standard uses cyclic redundancy check (CRC), more precisely, the CRC type used is CRC-16-CCITT, with registers initially set to 0xFFFF. [17]

Formally, CRC-16-CCITT is defined with the polynomial divisor  $x^{16} + x^{12} + x^5 + 1$ .

In [8] this flavor of CRC is called CRC\_B, it is so called to differentiate it to another CRC implementation used for NFC-A tags, called CRC\_A. An important difference between CRC\_A and CRC\_B is that the registers are initially set to 0*xFFFF* for CRC\_B, while for CRC\_A they are initialized to 0*x*6363.

All commands and responses, except for REQA and WUPA, use Cyclic Redundancy Check error recognition during data transfer.

### 2.4 Front-end and ADC

#### 2.4.1 ADC

The ADC is Thanh Trung Nguyen's design of an integrating ADC as presented in [16], with small modifications.

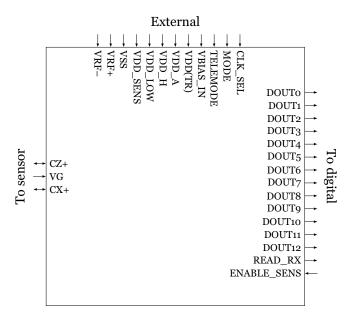

Figure 2.4 shows the signals going out an in of the front-end/ADC module used in the work presented here. From the signal interface figure one can see that it is connected to the antenna coil, that is because it has its own rectifier and regulators independent on the regulators and rectifiers used for the digital core, clock recovery, demodulator and modulator. The same is true for the ADC's clock recovery.

Figure 2.4: ADC top level schematic interface overview

#### 2.4.2 Front end

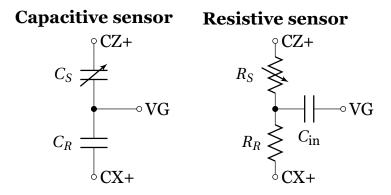

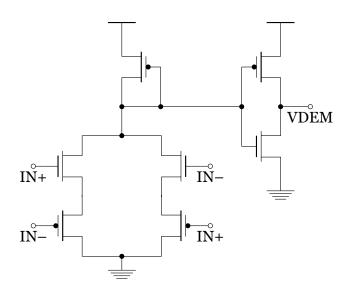

The ADC's sensor connections are VG, CZ+ and CX+. CZ+ is the reference or capacitive zero connection, CX+ is the sensor connection, VG is the amplifier input. Figure 2.5 demonstrates how sensors can be connected.

Even though it is made for capacitive measurement, it can be adopted to a resistive measuring with the addition of a capacitor on the input VG in series with the resistive network consisting of Rsens and Rref. The gain of the amplifier can be controlled by selecting the input capacitance.

$$A = \frac{C_{in}}{C_F}$$

Where the internal  $C_F$  is 4pF as can be viewed from the paper [16], and in Figure 2.5. The capacitive sensor arrangement is what is used in this work.

Figure 2.5: Capacitive and resistive sensor ADC connections. Subscript S denotes sensor, R denotes reference

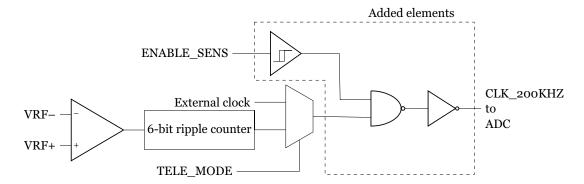

#### 2.4.3 ADC interface

The ADC operates continuously, as long as there is clock on the input. This is exploited in this work by adding logic for an ENABLE\_SENS signal, which, when high, enables the clock input to ADC. As this is a new addition, and not present in previous work, it is explained further in 4.1.

The digital outputs seen in Figure 2.4, called DOUT<0:12>, hold the sensor value converted to digital values.

#### 2.4.4 Converted data ready signal

After an analog to digital conversion the ADC enables a data ready signal, called *READ\_RX*, output indicating that its data outputs have valid values. This signal goes low based on its internal clock without any acknowledge from the digital core interfacing it.

Do to the ADC's implemented logic, data ready signal going high do not necessary mean that data is, in fact, ready. There are two things to look out for: first, data ready is pulsed almost immediately after starting a conversion. Second, do to a glitch in the logic there is an extra data ready signal pulsed after the ADC has reset its internal counters which means that the data on the output is nothing but zeros.

Another reason for not using just any data ready signal is because the ADC is more accurate after a few cycles, which Trung explains in [16]

A timing diagram demonstration the reset after data ready signal and after starting the ADC readout procedure can be seen in Figure 2.6.

| Internal clock   |  |   |   |   | Π |  | U |  |  | U | 5 | l | Γ | Ш |  | П |   | Л   | υ |   |

|------------------|--|---|---|---|---|--|---|--|--|---|---|---|---|---|--|---|---|-----|---|---|

| enable_sens      |  |   |   |   |   |  |   |  |  |   |   |   |   |   |  |   |   |     |   |   |

| DOUT< 0:12 >     |  | λ |   |   |   |  |   |  |  |   |   |   |   |   |  |   | A | фC) |   |   |

| read_rx          |  |   | Π |   |   |  |   |  |  |   |   |   |   |   |  |   |   | Π   | П |   |

| Internal reset_n |  |   |   | Γ |   |  |   |  |  |   |   |   |   |   |  |   |   |     |   | Γ |

Figure 2.6: Timing diagram, from simulated VHDL model, demonstrating ADC readout procedure. Demonstrating the out of place reset occurring after a data ready signal (read\_rx), and why care needs to be taken to ensure data is correctly read.

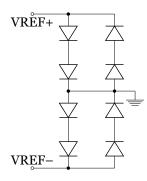

### **2.5** Power harvesting

To make use of the power from the carrier wave generated by the NFC reader a rectifier rectifying the AC signal to DC is required.

In [15] Trung Nguyen uses two rectifiers derived from [11, 20]. Ali Zaher proposes to use the same setup of a rectifier in [21] and a similar topology is proposed in [22] using three cascaded rectifiers.

Figure 2.7 shows the schematic of a single rectifier element as Nguyen and Zaher have utilized in their designs. This design can be cascaded in multi stage configuration to generate higher voltages on its output.[11]

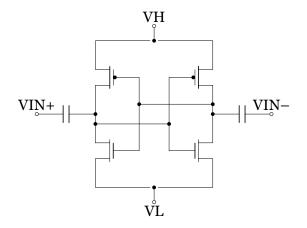

Figure 2.7: Single voltage rectifier element schematic.

### 2.6 Clock Extraction

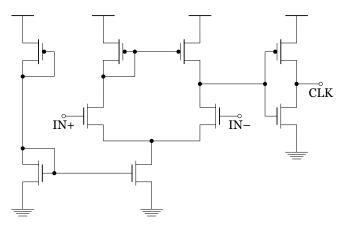

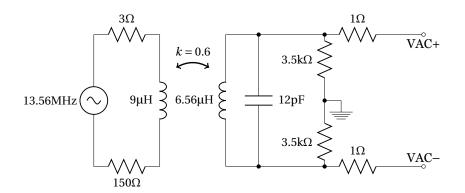

The carrier wave's frequency generated by the NFC reader is 13.56kHz $\pm$ 7kHz [3]. To recover clock from this carrier wave Zaher propose in [22] a simple clock extraction circuit consisting of a comparator. This design can be seen in Figure 2.8.

Figure 2.8: Clock recovery circuit

A similar implementation is demonstrated in [14, 15] as the chosen clock extraction implementation.

### 2.7 Demodulator

To interpret ASK modulated waveform from the carrier wave, a demodulator is needed. In [22] Zaher presents a demodulator which work with modulation more than 30% amplitude modulation index. The design he proposes can be seen in Figure 2.9.

Figure 2.9: Demodulation circuit, as presented in [22]

Part II Project

# **Full system overview**

Figure 2.10 shows an overview of the modules and their interconnections of the system which this project implements.

Figure 2.10: Full system module and inter-connection overview.

# Chapter 3 Digital Design

Figure 3.1: Digital core topology and important signal interconnects.

VHDL code for the digital design was written together with my supervisor Ali Zaher. We tested different approaches, where we tried each of our solutions to problems that were encountered and continued working with the best solution onto the next problem. Zaher took our solution and implemented it on a FPGA testing it in conjunction with his ASIC implemented demodulator/modulator, verifying that it could communicate with a phone acting as a NFC reader. He also did successful trials with that system connected to Trung's ADC on a separate chip.[21]

The HDL code, now tried and tested on an FPGA, was then modified further to be synthesizable into gate level logic. By employing more complex test benches, further testing and verification was done to ensure that it continued to adhere to the NFC-A tag type 1 specifications.

A VHDL model of the ADC interface's logic, ADC presented in [16], was implemented in the test bench to verify that the digital core could, in fact, operate together with the ADC as they are combined on the chip. This VHDL model allowed us to flush out bugs that would have otherwise been concealed, potentially springing forth at unfavorable moments, that is, after tape-out.

Figure 3.1 shows a somewhat simplified overview of how the VHDL code is segmented into modules, what signals are exchanged between them, and inputs and outputs of the entire digital core. The following sections will go more into the details for each module.

#### 3.1 Central control module

This module handles the NFC protocol logic, and includes a simple clock divider to generate clocks for uplink modulation.

It takes the decoded received bytes from the decoder module, checks CRC, determines what to do, and if it should respond. If it should respond, it creates a bit stream which is sent to the transmit CRC module, which in turn pads CRC bytes to it and sends it along to the encoder, which handles the modulation encoding of data for communication back to a reader.

The tag type which this design is based on has 120 bytes of user addressable memory, where 96 bytes, are non-volatile read/write memory available to the user.[17] The design presented here does not use any nonvolatile memory, instead a static implementation of the dynamic memory defined in [17] was hard-coded in the control module. The resulting memory map can be seen in Table 3.1.

The Header ROM(HR) bytes identify what specifications are implemented in the tag. HRo = 0x11 identifies the tag as a Type 1 NDEF capable tag with static memory map.[9] According to the specifications [9, 17], HR1 is reserved for internal use and shall be ignored.

Byte number 1 in block 2 contains the lower byte of the previously read ADC value. It can only be read using the *READ ALL* command, normal *READ* commands adhere to the setup listed explained more in the upcoming Section 3.6.

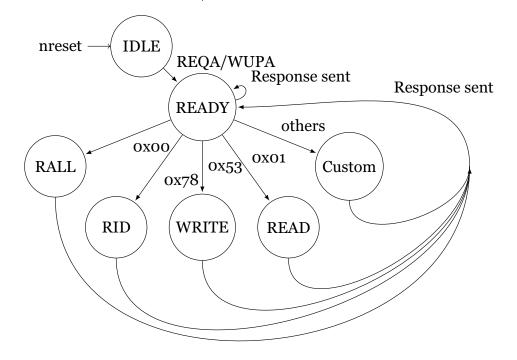

A simplistic state diagram shown in Figure 3.2 describes how the system is ready to receive and act on new commands after having received a *REQA* or *WUPA* command. The tag returns to the *IDLE* state when reset signal is pulled low, which happens during tag power up.

#### 3.1.1 Clock divider

The NFC standard requires that the tags response times are within small time margins. More specifically: The Topaz specifications[17] require that the response time from command send completion to the tag response (Device Response Delay) is  $\frac{128n+84}{f_c}$  for commands ending with a 1 bit and  $\frac{128n+20}{f_c}$  for commands ending with a 0 bit. Where  $f_c$  is the carrier frequency and n is defined as 9 for the commands *REQA*, *WUPA*, *READ*, *RID*, *RALL*, 554 for *WRITE-E* and 281 for *WRITE-NE*.

To achieve this, the main control module is running at carrier frequency and generates slower clocks that are synchronized to the rising edge of input patterns and the carrier frequency.

Three clocks are generated:  $\frac{f_c}{16}$ ,  $\frac{f_c}{64}$  and  $\frac{f_c}{128}$ . The  $\frac{f_c}{128}$  and  $\frac{f_c}{64}$  clock is used for timing bit lengths and half bit lengths in the transmit module, respectively. The final clock at  $\frac{f_c}{16}$  is used to generate the modulation

|               | Block |    |     | BY | TE nu | umbe | r  |    |    |

|---------------|-------|----|-----|----|-------|------|----|----|----|

| TYPE          | No.   | 0  | 1   | 2  | 3     | 4    | 5  | 6  | 7  |

| HR            |       | 11 | 4C  |    |       |      |    |    |    |

| UID           | 0     | oF | oF  | oF | oF    | 00   | 00 | 00 | 00 |

| DATA          | 1     | E1 | 10  | oE | 00    | 00   | 00 | 00 | 00 |

| DATA          | 2     | 00 | ADC | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | 3     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | 4     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | 5     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | 6     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | 7     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | 8     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | 9     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | Α     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | В     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| DATA          | С     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| Reserved      | D     | 00 | 00  | 00 | 00    | 00   | 00 | 00 | 00 |

| LOCK/reserved | E     | 01 | Eo  | 00 | 00    | 00   | 00 | 00 | 00 |

Table 3.1: Memory map, as it is hard coded in HDL source code. ADC value in block 2 byte 1 is reset to/default 00, but after a sensor read event it stores a byte of the previously read ADC value.

Figure 3.2: State diagram describing how commands received change the tag's operation and that after each response it returns to the READY state.

frequency used for load modulating the carrier wave, as explained in the section explaining tag to reader communication, Section 2.3.1.

The Specifications gives a margin for error of 6.5 clock cycles [17, page 11], simulation results from my implementation gives results which are within 90ns or  $\approx$  2 clock cycles off, which is within these margins.

#### 3.2 Receiving Cyclic Redundancy Check

This module is relayed bits received in the receive module via the control module. It runs cyclic redundancy check (CRC) of type CRC-B on the bits. If in the end the two bytes in the CRC registers are zero the CRC code for received bits are valid. This is possible due to the nature of CRC-B, which uses xor operations and bit shifting to verify received frames.

#### 3.3 Transmit Cyclic Redundancy Check

This module operates similarly to the receiving CRC module, see Section 3.2, except that it adds its final CRC register values to the end of the frame it receives from the control module, and subsequently pass it along to the encoding transmit module.

#### 3.4 Transmit module

A bit stream padded with CRC bits is sent from the transmit CRC module to the transmit module.

The clock divider in the control module, see Section 3.1.1, governs the timing of tag to reader communication.

As the clocks, and bit stream is controlled, what is left for this module is to handle Manchester encoding, which is described in the tag to reader communication section under background, see Section 2.3.1.

#### 3.5 Receiving Module

This module takes the demodulated signal embedded in the carrier wave by the reader and interprets it into bit values.

During downlink carrier wave amplitude modulation of the carrier wave, the clock recovery module has little or nothing to work with, and consequently the clock, from the tag's point of view, disappears during modulation. This means we can not use simple pattern recognition based on time-sampling the demodulated signal, since the tags reference to time is lost in the exact moment there is something of interest happening.

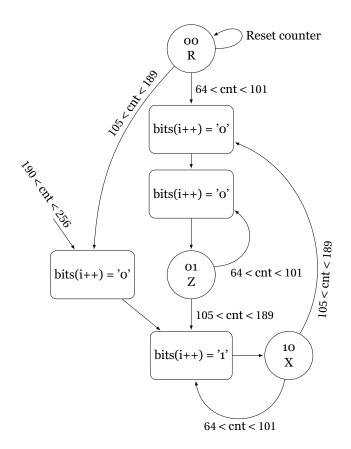

An oscillator could have been implemented to offload the internal clock during the pauses in the carrier wave, but it was deemed too complex a solution for a problem which could easily be circumvented. Our solution is instead to count the time between amplitude modulated signals, that is, time between clock losses, and use this information to discern the different patterns received. From what we know about the operation of reader to tag communication, explained in Section 2.3.2, we can distinguish patterns based on the number of cycles between each carrier modulation. Based on the known specifications and simulation experimentation the number of cycles for the different possible patterns was determined. Cycles are counted between two modulations of the carrier wave, such that the pattern decoded and subsequently the interpreted bytes are one period behind modulated bit patterns. A table covering the cycles classifying separate patterns is listed in Table 3.2. The important part to notice here is that a **Y** pattern is not recognized by it self, but from its resulting increase in pause between modulations.

Table 3.2: Cycles used in implementation to determine different patterns. A single bit duration is 128 cycles.

| Cycles |     | Pattern  |         |  |  |  |

|--------|-----|----------|---------|--|--|--|

| from   | to  | previous | current |  |  |  |

| 64     | 101 | Z        | Ζ       |  |  |  |

| 64     | 101 | Х        | Х       |  |  |  |

| 64     | 101 | _        | SoF + Z |  |  |  |

| 105    | 189 | Х        | Y + Z   |  |  |  |

| 105    | 189 | _        | SoF + X |  |  |  |

| 105    | 189 | Z        | Х       |  |  |  |

| 190    | 256 | Х        | Y + X   |  |  |  |

Figure 3.3 demonstrates the state machine that decodes received patterns into their respective bit values. The bits gathered in the state machine forms a byte, which is then passed along to the control module for further processing and use.

#### 3.6 Reading ADC data

After a glance over the memory map listed in Table 3.1, an experienced reader in the field of NFC-A tag type 1 might ask: "how do I read out the full-size sensor data, and why is it not explicitly listed in the memory map?" This section will try to answer that pressing question.

Figure 3.1, in the beginning of this chapter, describing the digital core, shows how 13 bits of ADC data is input into the control state machine, not only the 8 bits available through a *READ-ALL* command. In the implementation presented here, *READ-ALL* access different "memory space" than what is accessed using a *READ* command.

*READ-ALL* command access a hard-coded "memory space" with an added dynamic ADC readout byte in the middle, useful during testing. On the other hand, *READ* commands return data as they are listed in Table 3.3.

So, if we would like to read the complete ADC output data using our smart phone we need to understand how the interface to the ADC is

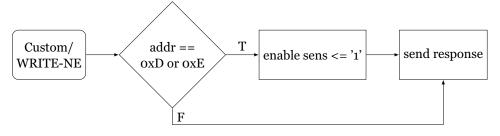

Figure 3.3: Receiving module state diagram. cnt is a counter counting cycles between received modulated signal lows. i is an indexing variable. *bits* is a register holding decoded bits

implemented. the ADC's input clock is enabled using a *enable\_sens* signal. If a *WRITE-E* command is done on address 0x0D or 0x0E the ADC clock is activated, by the *enable\_sens* signal going high. The *enable\_sens* remains high until the ADC's data ready signal, *READ\_RX*, has been high for 6144 clock cycles, ensuring that the next ADC activation starts the cycle at the same position every time.

After the tag has stored sensor values, the temporary stored values can be read using the *READ* command. The addresses listed in Table 3.3 describe which address contains data from sensor read-out.

| Address | Block | Byte |                                                |    |    |    |       |       |      |          |

|---------|-------|------|------------------------------------------------|----|----|----|-------|-------|------|----------|

| (hex)   | no.   | no.  | b8                                             | b7 | b6 | b5 | b4    | b3    | b2   | b1       |

| oxoD    | 1     | 5    | Lower ADC bits                                 |    |    |    |       |       |      |          |

| oxoE    | 1     | 6    | 0                                              | 0  | 0  |    | Hi    | gher  | ADC  | bits     |

| 0x14    | 2     | 4    | Secondary ADC read low                         |    |    |    |       |       |      |          |

| 0x15    | 2     | 5    | 0                                              | 0  | 0  | Se | econd | ary A | DC r | ead high |

| oxXX    | N/A   | N/A  | data in(8 downto 1), at last data ready signal |    |    |    |       |       |      |          |

Table 3.3: Tag's sensor data registers available to READ command.

The address setup follows the format as is listed in 3.4, although, in the implementation presented in this work, the relationship between what is read using *READ ALL* command and using *READ* command differ enough that the block and byte addresses are only listed here to indicate the implementation's heritage and specification compliance.

A full sensor read-out procedure is explained in the following subsection 3.6.1.

Table 3.4: Format of address operand ADD, from [17]

| ADDR |       |    |    |    |      |    |     |

|------|-------|----|----|----|------|----|-----|

| msb  |       |    |    |    |      |    | lsb |

| b8   | b7    | b6 | b5 | b4 | b3   | b2 | b1  |

| 0    | block |    |    |    | byte |    |     |

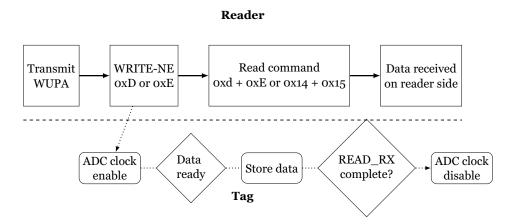

#### 3.6.1 Sensor read procedure

A read sensor command was implemented that causes the ADC to run and two 13-bit readouts are sampled. The command was implemented using the write-erase (*WRITE-E*) command, explained and listed in Section 2.3.3.

The readout procedure is as follows:

- 1. Reader initiates communication with a *REQA* or *WUPA* command to the tag.

- 2. The reader sends a *WRITE-ERASE* to address 0x0D or 0x0E (what is in its data block is irrelevant)

- 3. Tag enables ADC's clock, using the *enable\_sens* signal explained back in Section 2.4.4.

- 4. The ADC signals that a conversion is complete by enabling a data ready signal, also known as *READ\_RX*, when data is available at its output. On the third and fifth data ready signal the digital core samples the data and stores them in four registers holding one byte each.

All this is happening between the *WRITE-ERASE* command is received and a response is transmitted.

- 5. The reader sends *READ* command to address 0x0D, 0x0E, 0x14 and 0x15 which contains the high and low bit values of the third and fifth ADC readouts, respectively.

- 6. The reader inverts its received values and optionally displays the ADC measured values to the user.

This procedure might be hard to digest, to simplify matters somewhat, Figure 3.4 is of assistance .

Figure 3.4: Procedure for reading a sensor using the tag and how the tag behaves in turn. *Timescale not comparable*

A diagram describing how the *enable\_sens* signal is set can be seen in Figure 3.5.

Figure 3.5: ADC clock enable diagram, as the tag sees it.

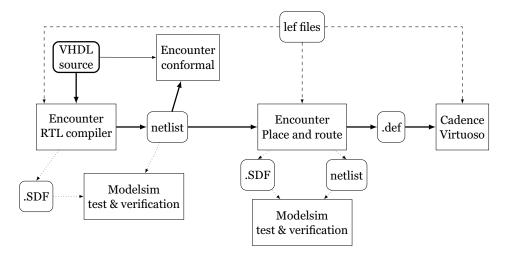

#### 3.7 Logic synthesis

Synthesis of the digital design was done using the Cadence software package.

First the VHDL code was compiled into gate level Verilog netlist using Cadence Encounter RTL Compiler.

Next, Cadence Encounter conformal tool checked the equivalence between the synthesized netlist and the source VHDL design.

When conformity was verified, the verilog netlist was simulated in modelsim for extra verification. During verilog netlist compilation a standard delay format (SDF) file is created, it is used in conjunction with the verilog netlist in modelsim to simulate the design with an approximation of the added delays inherent in the physical implementations.

Finally, Cadence Encounter Place and route tool layout and route the verilog HDL using TSMC 90nm standard cells library made available from IMEC/Europractice.

Now we have a near transistor-level gate layout ready for implementation with the other non-digital modules. IMEC keep the transistor level design safe at their end, while we only have access to the top level blocks, but of course the delay and parasitic properties making it possible to do a synthesis are made available to us. Again it is possible to test our design against a new SDF file, now making use of the delays on the synthesized clock network and other physical layout properties. Testing using the test benches created during design creation were re-run with these new delay values, it operated within specifications. Figure 3.6 gives an overview of the synthesis process as explained.

Figure 3.6: Simplified synthesis process overview

A tutorial, or walkthrough, was created for the process of synthesis; it can be seen in the appendix.

The process as listed in the appendix was based on a tutorial written by Amir Hasanbegovic and Hans K.O. Berge, and some initial research into the topic by Ali Zaher. Other aspects were learned from [19], together with info from [4].

### **Chapter 4**

### **Analog Design**

The complete design consists of an ADC and front-end module, a modulator/demodulator module, clock recovery module and two identical digital cores. See Figure 2.10.

The ADC and front-end is based on the implementation shown in [16], with the modulating transistor removed, and an added enable signal which controls the clock signal into the ADC.

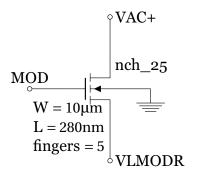

Modulator/demodulator, clock recovery and power regulators are based on the designs presented in [22]. The modulator/demodulator module was changed to provide a stronger clock output, and the modulating transistor was replaced with a 2.5V transistor.

As the previous work has been implemented in TSMC 90nm process, the work presented here uses the same process to enable reuse of these previously made modules.

#### **4.1 ADC**

The ADC is Thanh Trung Nguyen's design of an integrating ADC, as presented in [16], with small modifications.

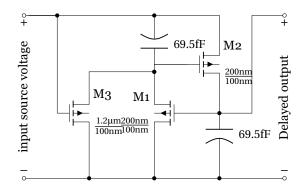

An enable signal was added to control the power draw of the ADC. Figure 4.1 shows how a nand gate acts as a switch controlled by the signal "ENABLE\_SENS", passing the clock signal when it is high and stopping it when low.

#### 4.2 ADC module interconnection

The pins and interconnections for the ADC module can be seen in Table 4.1.

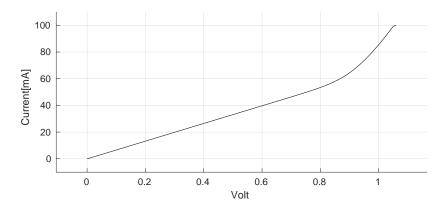

#### 4.3 Modulating transistor

Communication from tag to reader is transferred using load shift keying. To change the load, a modulating transistor was implemented. Table 4.1: ADC module terminals. External means that it is accesible on the outside of the chip, while internal means that it is only accessible from the digital core.

|                     | :                     |                                                                                     |

|---------------------|-----------------------|-------------------------------------------------------------------------------------|

| Pin                 | internal/<br>external | Description                                                                         |

|                     |                       |                                                                                     |

| CLK_SEL             | external              | Selects internal 50MHz oscillator or externaly connected clock on CLK_COUNT for the |

|                     |                       | integrating ADC time counting signal.                                               |

| CLK_COUNT           | external              | Clock used for counting rise and fall times in                                      |

| CLK_COUNT           | external              | the ADC.                                                                            |

| CLKIN_200KHZ        | external              | External logic clock.                                                               |

| TELE MODE           | external              | Selects external 200kHz clock for internal                                          |

| TEEL_MODE           | CATCHINA              | logic, or if low, selects 211.88kHz clock ex-                                       |

|                     |                       | tracted from 13.56MHz carrier wave. Here                                            |

|                     |                       | low is used.                                                                        |

| ENABLE_SENS         | internal              | enables logic clock to pass through to the                                          |

|                     |                       | internal logic. Used by the digital core to                                         |

|                     |                       | enable/disable ADC operation, see Figure                                            |

|                     |                       | 4.1.                                                                                |

| MODE                | external              | Selects between two modes of operation that                                         |

|                     |                       | differ mainly in how far the integrating ADC                                        |

|                     |                       | count during conversion. Here the longer                                            |