# Scalable Heterogeneous Supercomputing: Programming Methodologies and Automated Code Generation

# by Mohammed Sourouri

Thesis submitted for the degree of Philosophiae Doctor Department of Informatics Faculty of Mathematics and Natural Sciences University of Oslo November 2015

#### © Mohammed Sourouri, 2015

Series of dissertations submitted to the Faculty of Mathematics and Natural Sciences, University of Oslo No. 1703

ISSN 1501-7710

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, without permission.

Cover: Hanne Baadsgaard Utigard. Print production: John Grieg AS, Bergen.

Produced in co-operation with Akademika Publishing. The thesis is produced by Akademika Publishing merely in connection with the thesis defence. Kindly direct all inquiries regarding the thesis to the copyright holder or the unit which grants the doctorate.

# **Abstract**

Manycore processors such as Graphics Processing Units (GPUs) and Xeon Phis have remarkable computational capabilities and energy efficiency, making these units an attractive alternative to conventional CPUs for general-purpose computations. The distinct advantages of manycore processors have been quickly adopted to modern heterogeneous supercomputers, where each node is equipped with manycore processors in addition to CPUs.

This thesis takes aim at developing methodologies for efficient programming of GPU clusters, from a single compute node equipped with multiple GPUs that share the same PCIe bus, to large supercomputers involving thousands of GPUs connected by a high-speed network. The former configuration represents a peek into future node architecture of GPU clusters, where each compute node will be densely populated with GPUs. For this type of configuration, intra-node communication will play a more dominant role. We present programming techniques specifically designed to handle intra-node communication between multiple GPUs more effectively. For supercomputers involving multiple nodes, we have developed an automated code generator that delivers good weak scalability on thousands of GPUs.

While GPUs are improving rapidly, they are still not general-purpose, and depend on CPUs to act as their host. Consequently, GPU clusters often feature powerful multi-core CPUs in addition to GPUs. Despite the presence of CPUs, the focal point of many GPU applications has so far been on performing computations exclusively on the GPUs, keeping CPUs sidelined. However, as CPUs continue to advance, they have become too powerful to ignore. This gives rise to heterogeneous computing where CPUs and GPUs jointly take part in the computations.

The potentially achievable performance of heterogeneous computing codes can be very large, but requires careful attention to many programming details. We explore resource-efficient programming methodologies for heterogeneous computing where the CPU is an integral part of the computations. The experiments conducted demonstrate that by careful workload-partitioning and communication orchestration, our heterogeneous computing strategy outperforms a similar GPU-only approach on structured grid and unstructured grids.

Although our work demonstrates the benefit of heterogeneous computing, the painstaking programming effort required is holding back its wider adoption. We address this issue through the development and implementation of a programming model and source-to-source compiler called Panda, which automatically parallelizes serial 3D stencil codes originally written in C to heterogeneous CPU+GPU code for execution on GPU clusters. We have used two applications to assess the performance of our framework. Experimental

results show that the Panda-generated code is able to realize up to 90% of the performance of corresponding handwritten heterogeneous CPU+GPU implementations, while always outperforming the handwritten GPU-only implementations.

Compared to the more established GPU-only approach, the methodologies presented in this thesis contribute to harnessing the computational powers of GPU clusters in a more resource-efficient way that can substantially accelerate simulations. Moreover, by providing a user-friendly code generation tool, the tedious and error-prone process associated with programming GPU clusters is alleviated, so that computational scientists can concentrate on the science instead of code development.

# **Preface**

This thesis has been submitted to the Faculty of Mathematics and Natural sciences at the University of Oslo in fulfillment of the requirements for the degree of Philosophiae Doctor (Ph.D.). It is the result of more than three years of research conducted at Simula Research Laboratory and University of California, San Diego. This work has been supervised by Professor Xing Cai, Professor Scott B. Baden and Dr. Johan Simon Seland. Furthermore, this work was supported by the FRINATEK program of the Research Council of Norway, through grant No. 214113/F20.

# Acknowledgements

I would like to thank my advisors: Professor Xing Cai for always being there for me with his leadership, patience, guidance and invaluable help throughout my Ph.D., Professor Scott B. Baden for a great collaboration and for inspiring me to commit to the highest standards, and Dr. Simon Seland for valuable discussions and advice. It has been a privilege of a lifetime to work with all of you.

It has also been a pleasure to work at Simula Research Laboratory, as it provides an excellent work environment for conducting research. However, I would never in a million years end up at Simula had it not been for Dr. Tor Gillberg, whose encouragement and belief in me convinced me to pursue an academic career.

As a member of the High-Performance Computing group, I had the great opportunity to interact with fellow colleague Dr. Johannes Langguth with whom I had enjoyable and interesting collaboration. I also wish to thank Dr. Huayou Su at the National University of Defense Technology for his enthusiasm and input during his visit to Simula, also for making my stay in China pleasent.

During my enriching time at University of California, San Diego, I had the opportunity to work with many talented researchers. In particular, I wish to thank Dr. Nhat Tan Nguyen and Tatenda Chipeperekwa. I would also like to thank Natalie Lynn Larson for the countless hours they spent on proofreading my papers.

This Ph.D. has truly been a remarkable journey that has forged new collaborations across multiple countries. I wish to extend my gratitude to Filippo Spiga at the University of Cambridge for providing help and administrative support on the Wilkes cluster. Moreover, I would also like to thank Robert French, Adam Simpson, and Dr. Jack Wells at the Oak Ridge Leadership Computing Facility for their help on the Titan supercomputer. I would like to thank Ryan Davis at Princeton University and Assistant Professor Didem Unat at Koç University for interesting discussions and suggestions.

None of this work would be possible without the continuous patience, love and support of my dear friends and family, in particular, my parents, Sima and Reza, and my brother Saher.

Finally, I would like to express my sincere thankfulness to my beloved Frøydis, to whom I dedicate this thesis, for her love, patience and understanding.

Thank you.

Mohammed Sourouri, Oslo, September 2015

# **Contents**

| Abstra        | ct                                                                     | iii              |

|---------------|------------------------------------------------------------------------|------------------|

| Prefac        | e                                                                      | v                |

| Ackno<br>List | wledgements t of Papers                                                | <b>vii</b><br>xi |

| Introd        | uction                                                                 | 1                |

| 1             | Distributed Memory Parallelization                                     | 3                |

| 2             | GPU Programming using CUDA                                             | 3                |

| 3             | Heterogeneous CPU+GPU Computing                                        | 5                |

| 4             | A Framework for Heterogeneous CPU+GPU Computing                        | 6                |

| 5             | Summary of papers                                                      | 7                |

| 6             | Discussion                                                             | 15               |

| 7             | Conclusion                                                             | 18               |

| Paper         | I: Effective Multi-GPU Communication Using Multiple CUDA Streams       |                  |

| and           | d Threads                                                              | 29               |

| 1             | Introduction                                                           | 32               |

| 2             | Background                                                             | 33               |

| 3             | State of the Art                                                       | 33               |

| 4             | A New Communication Scheme                                             | 35               |

| 5             | Experimental Setup and Measurements                                    | 38               |

| 6             | Related Work                                                           | 40               |

| 7             | Conclusions                                                            | 41               |

| _             | II: CPU+GPU Programming of Stencil Computations for Resource-Efficient |                  |

| Use           | e of GPU Clusters                                                      | 45               |

| 1             | Introduction                                                           | 48               |

| 2             | GPU-only Implementations                                               | 49               |

| 3             | Heterogeneous CPU+GPU Implementations                                  | 51               |

| 4             | Performance Projections                                                | 57               |

| 5             | Experimental Setup And Results                                         | 57               |

| 6             | Related Work                                                           | 61               |

| 7             | Conclusions                                                            | 63               |

| Paper 1 | III: Scalable Heterogeneous CPU-GPU Computations for Unstructured |     |

|---------|-------------------------------------------------------------------|-----|

| Tetr    | rahedral Meshes                                                   | 69  |

| 1       | Introduction                                                      | 72  |

| 2       | Solving diffusion equations with finite volumes                   | 73  |

| 3       | Partitioning and Problem Setup                                    | 74  |

| 4       | Experimental Setup                                                | 78  |

| 5       | Experimental Results                                              | 79  |

| 6       | Conclusions                                                       | 81  |

| Paper I | IV: Panda: A Compiler Framework for Concurrent CPU+GPU Execution  |     |

| of 3    | BD Stencil Computations on GPU-accelerated Supercomputers         | 87  |

| 1       | Introduction                                                      | 90  |

| 2       | The Panda Programming Model                                       | 91  |

| 3       | The Panda Source-to-Source Compiler                               | 93  |

| 4       | Experimental Results                                              | 98  |

| 5       | Related Work                                                      | 103 |

| 6       | Limitations                                                       | 105 |

| 7       | Conclusion                                                        | 106 |

| Append  | dix I: Computational Resources                                    | 111 |

| 1       | Dirac                                                             | 113 |

| 2       | Stampede                                                          | 113 |

| 3       | Wilkes                                                            | 113 |

| 4       | Titan                                                             | 114 |

# **List of Papers**

#### Paper I

Effective Multi-GPU Communication Using Multiple CUDA Streams and Threads Mohammed Sourouri, Tor Gillberg, Scott B. Baden, Xing Cai Published in the proceedings of the 20th IEEE International Conference on Parallel and Distributed Systems, 2014, Pages 981-986

#### • Paper II

# CPU+GPU Programming of Stencil Computations for Resource-Efficient Use of GPU Clusters

Mohammed Sourouri, Johannes Langguth, Filippo Spiga, Scott B. Baden, Xing Cai Accepted for publication in the proceedings of the 18th IEEE International Conference on Computational Science and Engineering, 2015

#### Paper III

# Scalable Heterogeneous CPU-GPU Computations for Unstructured Tetrahedral Meshes

Johannes Langguth, Mohammed Sourouri, Glenn T. Lines, Scott B. Baden, Xing Cai Published in *IEEE Micro, Volume 35, Issue 4, Pages 6-15, 2015*

#### • Paper IV

Panda: A Compiler Framework for Concurrent CPU+GPU Execution of 3D Stencil Computations on GPU-accelerated Supercomputers

Mohammed Sourouri, Scott B. Baden, Xing Cai Submitted for publication.

# Introduction

**Figure 1:** The Titan supercomputer consists of 18688 compute nodes and was used in connection with Paper IV. The total compute capacity of the machine is 27 Petaflops. Image courtesy of Oak Ridge National Laboratory.

Mesh based simulations constitute one important motif of High Performance Computing (HPC) and are used in a wide range of scientific applications such as earthquake simulations [75], weather prediction [66], new materials discovery [57], and cardiac modeling [28]. For many computational scientists and engineers, computer simulations have become an irreplaceable tool, as they offer a fast, safe and an affordable way of conducting scientific experiments.

A common trait for many scientific applications is the need for more computing power to solve larger problems or to solve a problem faster. The continuous need for more computing power is by and large the main driving force behind the HPC market today. Historically, the most traditional way of providing computational scientists with more processing power has been by the release of newer processing units with higher computing capacity, that is, units capable of delivering more Floating-Point Operations Per Second (FLOPS). Occasionally, better and faster algorithms have also played a vital role.

The primary source of greater processing capacity in processing units has been attributed

to *Moore's law* [24], which states that the number of transistors roughly doubles every two years. An important detail in the evolutionary history of processing units is the slower improvement rate of memory bandwidth. The disparity between a processing unit's processing power and memory bandwidth, better known as the *memory wall* [70], is a growing concern for many computational scientists. Because applications that are limited by the memory bandwidth are prevented from fully utilizing the system's compute capacity, this leads to a waste of resources. In general, applications that are limited by the system's memory bandwidth are categorized as *memory bound* applications, while applications that are bound by the system's processing power are called *compute-bound* applications [72]. Prime examples of the former are stencil computations, while dense matrix multiplication serves as a good example of the latter. This thesis concentrates solely on mesh-based applications that are normally memory bound.

When scientific applications solve large problems that are too big to fit in the memory of a single machine or demand more processing power than a single machine can deliver or both, the application is usually written for clusters or very large clusters called *supercomputers*. Both of these systems are composed of multiple computers, called *compute nodes*, connected by a high-speed interconnect to aggregate the computational power and memories of each individual compute node.

Supercomputers have predominantly been homogeneous systems powered by conventional CPUs. However, we have lately witnessed a shift towards heterogeneous clusters. The nodes of these systems are equipped with manycore processors such as Graphics Processing Units (GPUs) or Xeon Phis, in addition to CPUs. By looking at the latest Top 500 list [63] of supercomputers published in June 2015, it is evident that the interest in heterogeneous systems is growing. For example, on the November 2009 list, only two of the systems were heterogeneous, while on the latest list, 88 systems are classified as heterogeneous systems. Figure 1 shows a picture of the Titan supercomputer, which is a heterogeneous supercomputer where each compute node is equipped with an NVIDIA Tesla K20x GPU and one 16-core AMD Opteron 6274 CPU. Titan consists of more than 18600 compute nodes and is at the moment of writing the second fastest supercomputer in the world [63].

One possible explanation for the increasing interest in heterogeneous clusters might be that manycore processors, such as GPUs, deliver higher theoretical rates of FLOPS with a greater power-efficiency than traditional multi-core CPUs. High FLOPS performance is regarded as a key attribute in many fields of scientific computing, especially with respect to numerical applications. The focus of this thesis is on mesh-based simulations on heterogeneous supercomputers equipped with GPUs developed by NVIDIA.

Currently, the most powerful supercomputers are Petascale systems, which means that they are capable of performing more than one quadrillion  $(10^{15})$  FLOPs. Moreover, the largest and the fastest supercomputers today are distributed memory systems interconnected by ultra-fast Infiniband technology [63]. In distributed memory systems, the different compute nodes are physically separated by the network so access to each other's memory requires explicit inter-node communication.

### 1 Distributed Memory Parallelization

The *de facto* programming model for scientific applications that targets distributed memory systems is message passing. The Message Passing Interface (MPI) [34] is a standardized library interface that developers are encouraged to follow. Examples of well-known, vendor neutral MPI libraries are MVAPICH2 [37] and OpenMPI [45].

Compared to sequential applications, writing MPI applications is regarded a challenge for many computational scientists, as it introduces the programmer to a parallel programming model called Single Program Multiple Data (SPMD), where the same application is executed on unique MPI processes, but with different data [11]. Other complicating details of MPI programming are domain decomposition, process layout, data sharing and explicit communication between different processes, which require calls to MPI routines.

HPC applications are judged by their ability to scale with the computing power provided by the cluster they are executed on. The two most common scaling methodologies in HPC are *strong* and *weak* scaling. In strong scaling studies the emphasis is generally on the solution time. Hence, the problem size is kept fixed, and more computational resources are added to obtain a faster solution time. Weak scaling studies are a type of experiments where the problem size is increased proportionally with the number of compute resources because the application can benefit by increasing the problem size and/or resolution. Under both of the scaling studies, communication becomes quickly a bottleneck as the number of compute nodes taking part in the computations grows. Usually, this is because the speed of communication is much slower than the speed of computations, but other reasons such as sequential communication patterns and network traffic congestions could also lead to poor scalability.

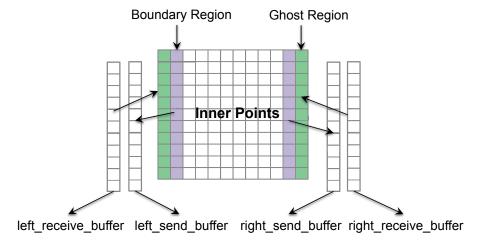

Hiding communication is considered by many as one of the most challenging aspects of developing MPI applications. The most widespread way of hiding latency overheads is by overlapping computations and communication [39]. Typically, this is done by adding a layer of *ghost cells* or *halo points* [25] around the problem domain so that the boundary points are separated from the interior points. Before computation of the interior points is started, the halo boundary points are computed first. During the computation of the interior points, halo boundary data are exchanged between neighboring domains using MPI routines such as MPI\_Irecv and MPI\_Isend. However, a much used strategy to improve performance is by using non-blocking MPI routines, such as MPI\_Irecv and MPI\_Isend, to build efficient pipelines. Other latency-hiding techniques include message aggregation [53], data compression [53] and virtualization [18], but are outside the scope of this thesis.

# 2 GPU Programming using CUDA

The increasing popularity of GPU-based computing poses a great challenge for computational scientists because programming GPUs is radically different than programming CPUs. This is primarily due to GPUs are complicated to program than CPUs is primarily due to the inherently different hardware architectures. For example, CPUs and GPUs differ in terms of how memory is handled. GPUs are designed to prioritize memory bandwidth over latency since latency can be hidden by parallel computation. CPUs, however, are

designed around large cache coherent memories to increase (single threaded) application performance. GPUs are not general-purpose processing units and must be installed in a system with a CPU that can act as the *host*. NVIDIA GPUs are programmed using the CUDA [40] programming API.

CUDA exposes the developer to a parallel programming model based on SPMD [7]. Moreover, in CUDA lightweight processes called *threads* are organized into *thread blocks*, which are used to carry out computations in special functions called *kernels*. Every thread block launches the same kernel, but each thread within a thread block processes its designated data elements. However, before the GPU can process the data, the programmer must explicitly transfer data from the host CPU to the GPU across the slow PCIe bus because GPUs and CPUs do not share the same memory space. The CUDA API provides functions for realizing such data transfers. Furthermore, independent of the direction, each and every transfer is incurred with a performance penalty when data is moved across the high-latency PCIe bus.

The descriptions unveiled above highlight only *some* of the details that require a programmer's attention. Although a small number of programmers manage to overcome the obstacles of GPU programming, realizing high performance is possibly the most challenging part of GPU programming, which sometimes requires that existing algorithms are redesigned so that they better map to the GPU's architecture [10, 13, 14, 26, 32, 54, 71]. Unless the algorithms are reworked, CPUs could potentially outperform GPUs [8, 38].

GPUs are designed to exhibit parallelism by incorporating thousands of simplistic cores operating at low frequencies < 800 MHz. CPUs on the other hand incorporate typically 8-18 more powerful cores running at frequency close to 3 GHz. The inclusion of thousands of cores demands a memory bandwidth that is capable of handling the traffic generated by all of the cores. In order to cope with the increased memory traffic, GPUs utilize faster and more expensive GDDR5 memory, while CPUs use the much slower and less expensive DDR3/DDR4 technology. Because GDDR5 is more expensive, GPUs come with a very limited memory capacity. A typical compute node today is equipped with 128-256 GB of DDR3/DDR4 CPU memory, while the fastest GPUs are equipped with only 12 GB of memory. Hence, the limited memory capacity offered by GPUs becomes quickly a bottleneck when performing simulations involving large datasets/compute heavy kernels. However, by distributing a simulation across multiple GPUs, computational scientists are able to access more memory and computational capacity.

Multi-GPU programming follows the same principles as ordinary multi-CPU codes, that is, MPI is used for inter-node communication and ghost cells are used to hide communication overheads. One important difference is that in multi-GPU applications, computations are typically executed by CUDA kernels on the GPU and not on the CPU. The role of the CPU in multi-GPU applications is mostly to perform administrative tasks such as intra and inter-node communication. Since the computations are done on the GPU, the CPU is mostly idling and thus left underutilized.

| <b>Processing Unit</b> | 2× Intel Xeon E5-2680 | Nvidia Tesla K20 |

|------------------------|-----------------------|------------------|

| Peak DP, GFLOPs        | 345.6                 | 1170             |

| Peak BW [GB/s]         | 102.4                 | 208              |

| STREAM [GB/s]          | 77                    | 151              |

**Table 1:** An overview of key hardware specifications of the GPU-equipped compute nodes of Stampede.

#### 3 Heterogeneous CPU+GPU Computing

One recent development in scientific computing has focused on combining CPUs and manycore processors for improved performance and energy efficiency [36]. The main purpose of a CPU+GPU implementation is to fully utilize the entire pool of processing units to solve a given problem as fast as possible. Table 1 displays the specifications for the GPU and the CPUs installed in some of the compute nodes of the Stampede [62] supercomputer. Judging by the performance numbers shown in Table 1, the GPU's theoretical peak FLOPS rate is approximately 3.4× higher than the two CPUs'. The realistic memory bandwidth obtained using the STREAM benchmark [33] is merely 1.94× higher. We concentrate on memory bound applications and therefore on the memory bandwidth numbers.

In short, the numbers from Table 1 tell us that the GPU is close to  $2\times$  faster than the two CPUs. So the workload division must reflect this performance difference. If the workload division is not appropriate, the application will most likely run into workload balancing issues that will degrade the performance because the fast GPU will continuously wait for the CPU. Thus, load balancing is an essential component of any heterogeneous CPU+GPU implementation.

There are multiple ways to load balance heterogeneous CPU-GPU implementations. Previous attempts at developing prediction models for heterogeneous CPU+GPU codes include [3, 6, 55, 65, 67] both *static* and *dynamic* load balancing have been proposed in the past.

Static load balancing means that the workload is partitioned before the computations. Typically, the entire or a small portion of the application is profiled first. Then, the acquired profiling data is used as a guiding measure to determine the workload division. There are significant advantages with static load balancing. Since the load balancing is performed before the actual computation takes place, the overhead associated with this strategy is virtually non-existent. The disadvantage of static load balancing is that it cannot be applied to computational problems in which the optimum workload division cannot be determined by profiling or where the optimum workload division varies during the execution.

Dynamic load balancing means that a special load balancer or scheduler automatically adjusts the workload division between the CPU and the GPU during the computation. This is especially useful for volatile workloads. Dynamic load balancers are usually domain specific, and can thus be difficult to generalize. The main disadvantage of dynamic load balancing is the relatively high overhead arising from the need to continuously reevaluate and adjust the workload division. The workload of the applications that we focus on do not change during execution, therefore we consider a static load balancing scheme as the most viable approach

In connection with this thesis, we have developed a simple static model for predicting the CPU's workload ratio for memory-bound applications. As opposed to other models [3, 6, 55, 65, 67] our model is not dependent on instrumenting, sampling or profiling of the target application on multiple nodes. The only dependency introduced in our model is the STREAM memory benchmark, which is open-source software that can be freely downloaded. It is only necessary to run the STREAM memory benchmark on a single compute node. We relate the workload ratio of a given processing unit to the its bandwidth and divide it by the aggregated memory bandwidth of all the processing units, as shown in (1).

$$\frac{CPU_{Bw}}{(GPU_{Bw} + CPU_{Bw})}\tag{1}$$

In (1),  $CPU_{Bw}$  and  $GPU_{Bw}$  represent the actual memory bandwidths obtained using the STREAM memory benchmark. As an illustrative example, we use results from Table 1 and insert these numbers into (1) to get an appropriate CPU workload division ratio, which is 33%. Additionally, if the peak theoretical results from Table 1 were used, the suggested CPU workload division ratio would be 32%, which could leave the CPUs slightly underutilized. However, achieving the peak theoretical memory bandwidth is a naive assumption, which is similar to what other researchers have observed [27, 72]. Thus, for more accurate predictions, we use the realistic memory bandwidth obtained using the STREAM memory benchmark.

#### 4 A Framework for Heterogeneous CPU+GPU Computing

It is hypothesized that the collaboration of CPUs and manycore processors will play an even more important role in near-future, especially as future HPC will adopt fused CPU+manycore processor chips [1, 36]. A number of studies have demonstrated the benefit of concurrent CPU+GPU execution in for example stencil computations [28, 49, 57, 65, 73]. Despite the advantages of this approach, the number of tools that can reap the benefit of this strategy is rather limited.

Many scientists already find code development for a single GPU challenging, in particularly an entire cluster of CPUs+GPUs. This challenge is further complicated by the lack of a high-level unified programming model that enables developers to exploit different levels of parallelism. Despite the proliferation of programming models such as CUDA and OpenCL [23], developing clean code with high performance in a productive manner remains a big task. The lack of productivity is tightly coupled with the fact that current programming models require low-level knowledge of the underlying architecture. This type of knowledge is often difficult to grasp for computational scientists. Moreover, current programming models also expose the developer to far too many complex programming details.

Another complexity that is often neglected is portability. Developers face at least two challenges with respect to portability. The first challenge is tied to new GPU architectures. GPUs, like CPUs, are also updated at the rate of Moore's law, resulting in a new generation of architecture every two years. Traditionally, with every new generation of architecture, certain architecture-specific optimizations become obsolete. The second

daunting challenge arises when developers try to port code between different types of clusters e.g. between two heterogeneous clusters using different types of GPUs or even worse, between a homogeneous and a heterogeneous cluster.

The difficulties described above have given rise to a variety of approaches such as compiler directives, libraries and Domain Specific Languages (DSLs). One developer friendly approach, advocated by some experts, is the use of compiler directives to guide the compiler in generating parallelized code. Thanks to the backing of numerous vendors, OpenACC [43] and OpenMP [44] have rapidly established themselves as the most popular solutions for directive-based code development. Despite delivering acceptable performance [31, 69] in a broad range of applications, neither of these two solutions is capable of producing code that can target an entirely homogeneous or an entirely heterogeneous cluster. As a result, developers must write code that deals with MPI.

DSLs constitute a compromise between language generality and performance. Depending on the framework, DSLs may support distributed memory systems. Since DSLs' knowledge are limited to a particular domain, they can leverage on this knowledge to deliver excellent performance. In contrary to a directive-based approach, DSLs [17, 74] require that both novice and expert programmers invest a considerable amount of time and effort in code development. A similar investment in code *redevelopment* is also required, if the programmer already has a parallel or a serial implementation.

Unlike DSLs, but like directives, libraries [56] offer the opportunity to stay within the boundaries of a general purpose programming language, but at the expense of performance. The common trait of libraries and DSLs is that they both require explicit changes to the code, which can easily cause programmers unnecessary difficulties. Portability is another issue that libraries often fail to address, as they are traditionally optimized for a specific architecture or cluster.

The different programming models presented so far highlight the lack of a developer-friendly model that is capable of realizing high-performance on modern heterogeneous clusters using a general purpose programming language. This is especially a challenge for domain scientists who wish to write code that can harness the computational provided by heterogeneous clusters.

## 5 Summary of papers

During the course of this PhD project, two papers were published in international peer-reviewed conferences [58, 59], one in an international peer-reviewed journal [28] and another one is submitted to an international peer-reviewed conference.

The focal point of this thesis has been a bottom-up approach to heterogeneous computing on GPU clusters. Paper I describes an effective communication scheme for 3D stencil computations on compute nodes equipped with multiple GPUs. Papers II and III detail advanced hybrid programming models for implementing scalable HPC applications on GPU clusters. The hybrid programming model outlined in Papers II and III consists of MPI, CUDA and OpenMP, making it possible to combine the computing power of CPUs and GPUs to achieve high performance on both structured and unstructured grids. Paper IV presents Panda, a novel programming model and its adherent compiler framework for

automated generation of 3D stencil codes on structured grids incorporating the hybrid programming model detailed in Paper II and III. Details regarding the computational resources used in the thesis are presented in Appendix I.

# 5.1 Paper I: Effective Multi-GPU Communication Using Multiple CUDA Streams and Threads

Future heterogeneous supercomputers such as ORNL Summit [42] and ANL Aurora [2] will feature compute nodes that are equipped with multiple GPUs or Xeon Phis. Installing multiple devices per node has advantages with respect to space and energy. We are already witnessing a shift towards this architectural change. For example, the world's current No. 1 supercomputer, Tianhe-2 (see [63]), is already equipped with three Xeon Phi coprocessors on each node.

The most widespread method for developing HPC code with multiple GPUs per node in mind is by spawning a unique MPI process for each GPU. The clear advantage of this approach is versatility, since the same code will work flawlessly regardless of the number of devices installed per node. However, in this approach, intra-node and inter-node communication are not differentiated and as a result unnecessary overhead is induced due to ineffective and redundant memory copies between the GPU, CPU and the MPI communication subsystem [21], and the creation of a process context for each GPU [48]. When an MPI process is controlling a GPU, it is encapsulated by the process' context, which means that e.g. two neighboring GPUs on the same node cannot exchange data directly unless message-passing or inter process communication is practiced. On the other hand, when one or more threads are controlling one or multiple GPUs, data can be more directly exchanged between the different GPUs using functions from the standard CUDA API.

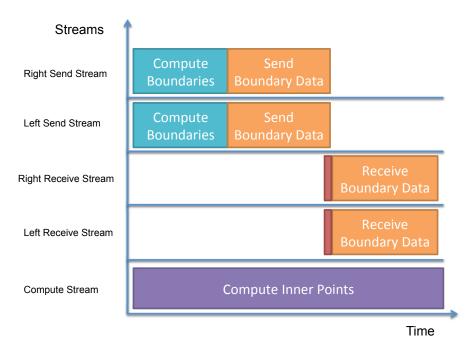

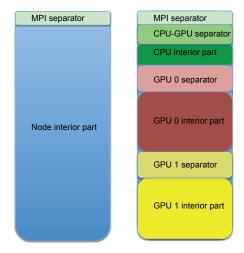

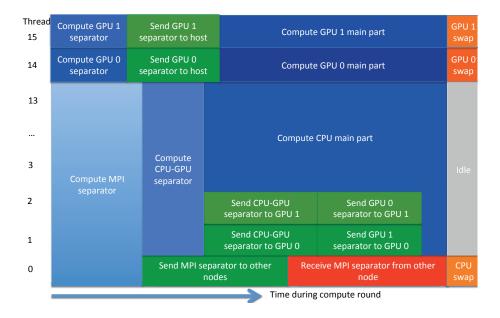

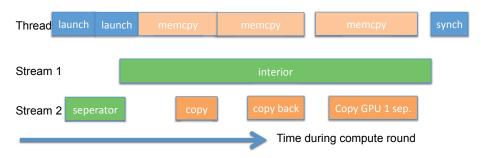

This paper introduces an efficient intra-node communication scheme designed for computations on compute nodes that are equipped with multiple GPUs. In the presented scheme, the domain is decomposed, whilst one OpenMP thread is spawned to control each GPU, as opposed to one MPI process per GPU. The benefit of using threads is that the GPUs can effectively communicate using shared-memory and the ability to perform concurrent kernel launches. Since the GPUs stay within the same process context, the GPUs can benefit from fast intra-node GPUDirect v2 Peer-to-Peer [41], which is not possible if MPI is used.

Another optimization, called multi-streaming, is used to increase performance by placing the CUDA streams, which are responsible for sending computed halo boundaries and unpacking the halo boundaries, in separate OpenMP threads. In addition to the thread responsible for controlling the GPU, two additional threads are spawned per GPU, one for sending computed halo boundaries and one for receiving computed halo boundaries. The benefit of this strategy is that CUDA kernels responsible for unpacking halo boundary data can start immediately after the data from a neighboring device has been received. On the contrary, if only one thread was used to control multiple GPUs, the running thread could be blocked by for example another function, which would prevent the CUDA unpack kernels from being launched.

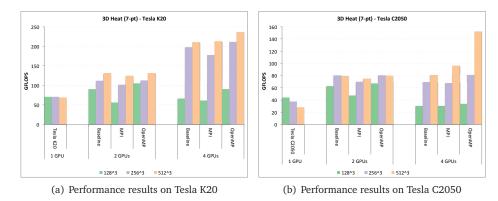

The performance of the proposed scheme is compared to a state-of-the-art MPI imple-

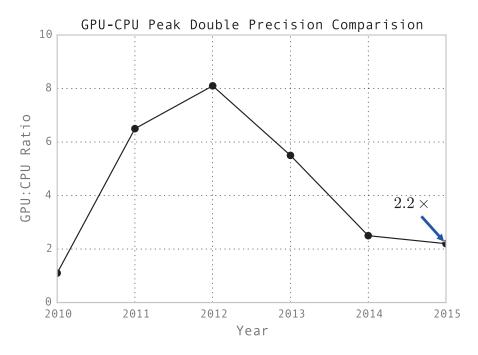

**Figure 2:** Since 2010, the difference in peak double precision floating point between GPUs and CPUs has become smaller. from 8× in 2010 to 2.2× in 2015.

mentation [5, 20, 35, 46, 47, 50, 56] where an MPI process is spawned per GPU and two CUDA streams are created. The first CUDA stream is used for the halo boundaries, while the second CUDA stream is used for computation of the interior points. Strong scaling experiments are conducted using a simple 7-point 3D Laplacian kernel. This particular compute kernel is chosen because it rapidly becomes communication bound. Our proposed scheme outperforms the MPI implementation and is up to 1.85× faster.

# 5.2 Paper II: CPU+GPU Programming of Stencil Computations for Resource-Efficient Use of GPU Clusters

High computational throughput and energy efficiency have placed GPUs at the heart of many clusters. GPUs are not general-purpose and depend on a CPU to operate, which is why GPU clusters are populated with CPUs. A recent surge of microarchitectural enhancements [15] such as the integration of more cores, advanced vector extensions, and fused multiply-add, has made it possible for CPUs to deliver an impressive amount of processing power, as Figure 2 displays. Furthermore, CPUs also provide fast and large last level caches, which can increase performance substantially if properly exploited, as a numerous studies [4, 10, 12, 51, 60] have shown. Additionally, modern CPUs nowadays provide a good memory bandwidth and a bytes-per-FLOP ratio that is within the vicinity of GPUs [30]. However, in many GPU applications, computations that once were performed

on a CPU are now offloaded to the GPU, leaving the powerful CPUs underutilized.

In Paper II, two different CPU+GPU implementation techniques are developed and compared with a corresponding GPU-only implementation where the computations are performed exclusively on the GPU. The implementations developed employ a workload-partitioning strategy, which enables concurrent CPU+GPU execution to increase performance by exploiting the CPU's strength.

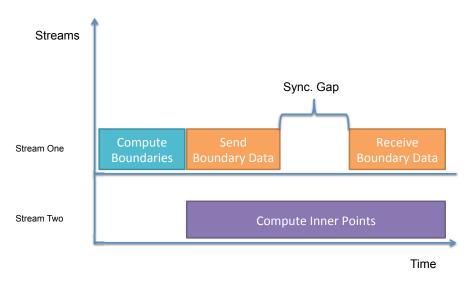

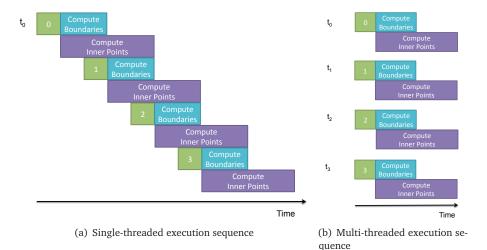

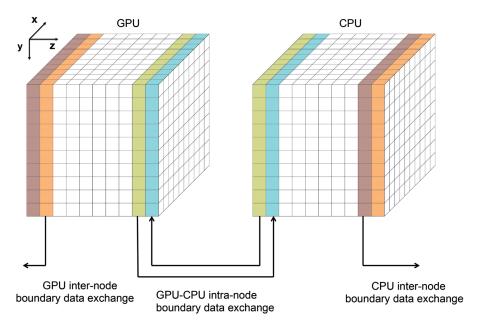

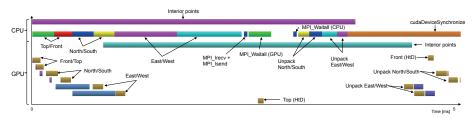

The first CPU+GPU implementation is a naive version that augments an existing state-of-the-art multi-GPU application [5, 35, 46] based on MPI and CUDA, by performing computations on the CPU using OpenMP. More specifically, the domain is decomposed, followed by a separation of halo boundary and interior points on each GPU. By processing the interior points and the boundary points separately in different CUDA streams, communication can be overlapped with computation.

Similar to state-of-the-art multi-GPU applications, asynchronous MPI routines are posted at the very beginning to build efficient communication pipelines, followed by CUDA kernel launches on the GPU. The computations on the CPU can only start once the different CUDA kernels have been launched. The naive implementation trades ease of use with only moderate speedups compared to the GPU-only version. The main drawback of this version stems from its inability to overlap CPU+GPU computations with inter-node MPI communication. Although asynchronous CUDA routines are used to ensure that intra-node communication is overlapped, inter-node communication is rarely overlapped since CUDA kernel launches and CUDA data transfers can not be launched because the CPU is busy computing. For example, the unpacking of halo boundary data can not start on the GPU until the CPU has completed the computations of the interior points.

The naive implementation inability to overlap CPU+GPU computations with communication is addressed in an improved implementation called *nested*. OpenMP's nested parallelism capability is used to separate computations of the interior points and inter-node communication as distinct tasks. Moreover, two different thread groups are then created to concurrently process the different tasks. The first thread group is responsible for MPI communication, launching CUDA kernels and computations of halo boundaries on the CPU. Furthermore, the second group is dedicated to computing the interior points on the CPU.

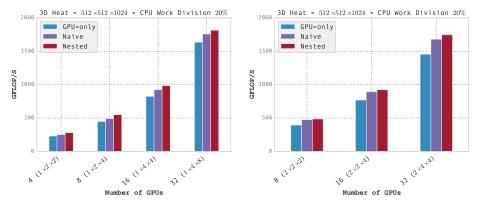

One of the challenges that developers are facing when dealing with CPU+GPU codes is to find the optimal workload division ratio for the processing units, that is, the appropriate compute portion that gives the highest performance. Paper II presents a performance model for predicting the load balance between the CPU and the GPU in memory bound applications. With the aid of the STREAM memory benchmark [33] the realistic memory bandwidth of each processing unit is surveyed. The obtained memory bandwidth results are then used to determine the CPU workload ratio by dividing the CPU's memory bandwidth by the total aggregated bandwidth of the CPU and the GPU.

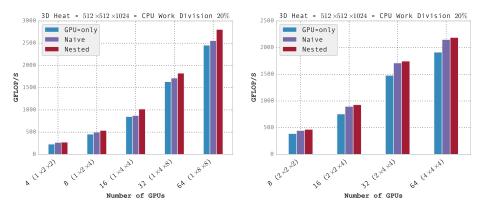

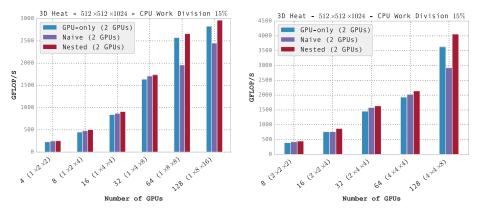

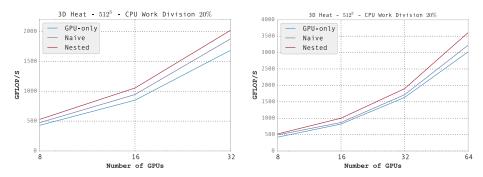

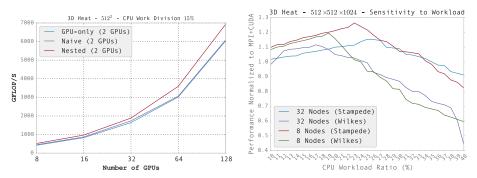

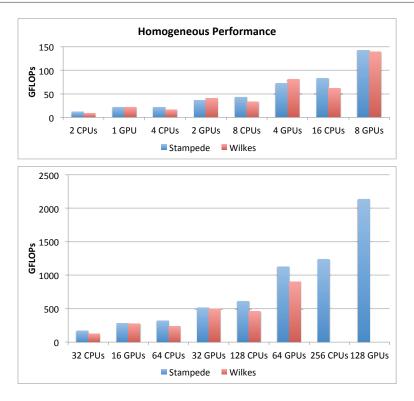

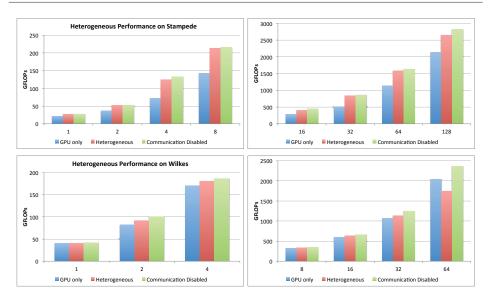

Strong and weak scaling experiments on the Stampede [62] and the Wilkes [64] clusters were conducted to assess the performance of the two implementations. Additionally, the results were compared to a corresponding handwritten GPU-only implementation. Both of the proposed implementation strategies outperformed the GPU-only implementation on the two clusters. In order to evaluate the accuracy of our performance model, a series of CPU workload sensitivity experiments were conducted by varying the CPU's workload

ratio. The results from this experiment aligned well with the results predicted by our performance model.

Despite the accuracy of our performance model, projecting a perfect workload division ratio for CPU+GPU codes remains a complicated matter because the workload ratio can be very sensitive to various parameters such as problem size, performance difference between the processing units, etc. Another important finding of this experiment is that a CPU workload ratio that is too high will degrade the performance, but a too low CPU workload ratio is acceptable. In other words, in situations where the CPU workload can not be predicted accurately, it is better to lower the predicted inaccurate CPU workload.

#### 5.3 Paper III: Scalable Heterogeneous CPU-GPU Computations for Unstructured Tetrahedral Meshes

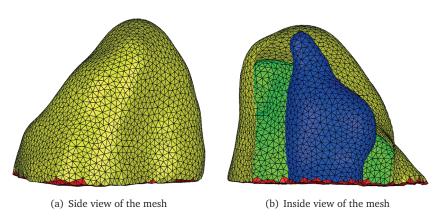

Figure 3: The mesh used in an unpublished version of Paper III, models a healthy male human heart acquired by MRI. Image courtesy of Johannes Langguth.

Paper III investigates heterogeneous CPU+GPU computations on an unstructured tetrahedral mesh by solving the diffusion equation using a cell-centered Finite Volume Method. The tetrahedral mesh representing a healthy male human heart served as a test instance, consisting of 115 million tetrahedrons. The mesh is illustrated in Figure 3. Additionally, some best practices for developing heterogeneous CPU+GPU codes that can be of help to other scientists are also presented.

We give detailed advice including how to handle multiple GPUs per node, how the different tasks on the CPU should be programmed and how to statically adjust the CPU workload ratio in conjunction with an increasing number of GPUs per node.

The methodologies and ideas presented in Paper III are similar to those presented in Paper II, but applied to another scientific domain. Moreover, if a compute node is equipped with multiple GPUs per node, the technique from Paper I, where one CPU thread is created for each GPU is used. A stiff challenge that many computational scientists face when working on unstructured meshes arises from indirect and irregular memory accesses. The irregular nature of the problem also poses a challenge with respect to

workload-partitioning, load balancing and the inherently more complex communication pattern. Another complicating factor with the irregular accesses is that they dramatically reduce the computational intensity, which quickly limits the scalability because of a low compute-to-communication ratio.

Both a heterogeneous CPU+GPU and a corresponding GPU-only implementation were investigated on the Stampede [62] and Wilkes [64] clusters using up to 128 GPUs. A homogeneous CPU-only version was also implemented to better assess the CPU's performance, and thus its contribution. Additionally, to establish an upper bound of the achievable performance, the MPI calls were commented out so that both inter and intranode communication were disabled. Before the experiments were conducted, the CPU workload ratio was computed statically by using the performance model presented in Paper II.

Strong scaling experiments on 128 nodes of Stampede showed that the heterogeneous CPU+GPU implementation consistently outperformed the GPU-only implementation, while realizing 95% of the upper bound. Similar results were also observed for 64 nodes on the Wilkes cluster when a single GPU was used per node. However, when both GPUs on each Wilkes node were used, the GPU-only implementation was faster than the heterogeneous CPU+GPU implementation. In the dual GPU configuration, one MPI process was spawned for each GPU. A consequence of this process layout was that the number of available CPU cores was divided equally between the two MPI processes, which significantly weakened the CPU's contribution.

Our investigations showed that when both GPUs on each Wilkes node were used, the access to fewer CPU cores and higher intra-node communication overhead became the performance limiter. Like in Paper II, the workload ratio predicted by the performance model was within the vicinity of the observed best results. Similarly, the experimental performance results presented in Paper III validate the viability of heterogeneous CPU+GPU computing even on unstructured grids.

# 5.4 Paper IV: Panda: A Compiler Framework for Concurrent CPU+GPU Execution of 3D Stencil Computations on GPU-accelerated Supercomputers

A distinct drawback of the heterogeneous CPU+GPU computing technique demonstrated in Papers II and III is the tedious and often error-prone implementation process associated with it. Heterogeneous CPU+GPU codes require that the same computation and communication functions are replicated on both of the processing units. In other words, the same functions on the CPU must be implemented for the GPU and vice versa. Another complicating factor is the complex intra-node communication that takes places between the two processing units and the workload-partitioning strategy employed to divide the computational workload between the CPU and the GPU. This partitioning requires careful attention to many programming details.

Paper IV introduces a novel programming model and a domain-specific source-to-source compiler called Panda, which automatically parallelizes 3D stencil codes written in sequential C to a heterogeneous CPU+GPU form for execution on GPU clusters. The programming model provides a set of new compiler directives that serves as an interface,

5. Summary of papers Introduction

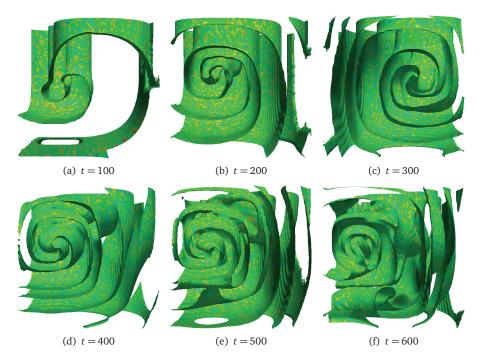

**Figure 4:** The Cardiac Electrophysiology Simulator visualized at different time steps, *t*. The figures show how electrical signals propagate through the cardiac tissue and create spiral shaped patterns.

which lets the user annotate parts of a serial C code that deal with time consuming 3D stencil computations. The annotations implicitly capture parallelism that guides the compiler to perform appropriate transformations for auto-generation of CPU+GPU code. Moreover, by keeping the number of directives to a minimum, the Panda programming model offers not only a simple, but yet a highly user-friendly interface that promotes productivity. Furthermore, general-purpose compilers that do not implement Panda directives will simply ignore them and as a result, users only need to maintain a single code base for their sequential and their parallel code.

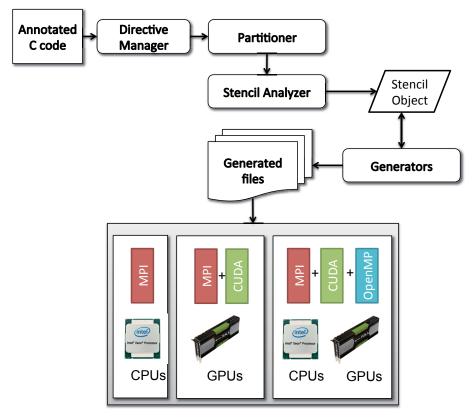

The Panda framework is implemented in C++ using the ROSE [29] compiler infrastructure and targets 3D stencils. Furthermore, the Panda framework employs a modular design where the different parts are compartmentalized. An overview of the Panda source-to-source compiler is illustrated in Figure 5. For brevity, several modules are excluded from Figure 5.

The Directive Manager module ensures that the input source file is correctly annotated. In addition, the role of the Directive Manager module is to extract information about the user specified compute arrays and their sizes. Based on the extracted information a Partitioner module will decompose the domain into smaller cuboids. Furthermore, a special Stencil Analyzer module will then analyze the annotated loop nests and search for nearest neighbor compute patterns. The result of the Stencil Analyzer module is then written into a Stencil object that is passed to the different generator modules that

Figure 5: A high-level overview of the Panda framework.

are responsible for generating the actual source files.

Two applications were used to assess the performance of our compiler framework. As the first application we used the well-known 3D Laplacian stencil kernel from Papers I and II, while the second application was a real-world 3D Cardiac Physiology Simulator, as illustrated in Figure 4. The former application was used for its interesting computation-to-communication characteristics, while the latter application was used to demonstrate Panda's ability to tackle more realistic code, including computations on the physical boundaries. In addition to the Panda auto-generated codes, highly optimized handwritten versions of the two applications mentioned above were also developed for the purpose of evaluating the effectiveness of Panda codes. Depending on the cluster configuration, the Panda generated code was able to realize close to 90% of the performance of the handwritten heterogeneous CPU+GPU code for both applications. Although the Panda generated code is not as fast as the handwritten code, our results indicate that the Panda generated code is still faster than the aggressively optimized handwritten codes where the computations are performed exclusively on the GPU. We thus believe that our autogenerated CPU+GPU code provides a satisfactory alternative to implementations that

6. Discussion Introduction

ignore the computational power of CPU and exclusively offload computations to the GPU. Panda's area of operation is currently limited to stencil computations on arrays that are logically represented as 3D. Moreover, it is also assumed that the annotated compute loops are parallelizable in such a way that the computed values can be updated concurrently. The narrowed domain of operation makes it possible to carry out effective optimizations at the expense of generality.

#### 6 Discussion

The programming methodology presented in Paper I highlights intra-node communication bottlenecks that arise within a compute node equipped with multiple GPUs. San Diego Supercomputer Center's latest HPC system, Comet [52], is an example of a Petascale machine that adopts this node configuration. Future systems such as ORNL Summit [42] indicate that this trend will continue. On the basis of the experimental results presented in Paper I, we believe that intra-node communication and the complex interactions between multiple GPUs per node will play an important role in both current and future systems. Hence, extending the methodology presented in Paper I could be worth pursuing.

A clear limitation with the programming methodology presented in Paper I is that it is currently limited to GPUs that are located on the same node. In other words, inter-node communication between multiple nodes equipped with multiple GPUs is not taken into consideration. An obvious extension would therefore be to have an MPI process wrap the programming technique presented in Paper I so that inter-node communication is realized.

In the context of heterogeneous CPU+GPU computations, the use of multiple threads to control each GPU, such as in Paper I could possibly impede the CPU's performance. An important finding in Papers II and III was that the number of CPU threads spent on computation was crucial for achieving high performance. Hence, it could be worth pursuing the use of logical threads such as Intel Hyper-Threading [19] technology as an alternative to threads that are each mapped to a physical CPU core. We are also aware that later CUDA versions now support non-blocking CUDA events, which could potentially mimic some of the functionality of the methodology presented in Paper I. However, the use of CUDA events comes at the expense of increased code complexity and reduced code readability because CUDA events require calls to at least three additional CUDA functions. Moreover, the use of CUDA events does not automatically address issues such as concurrent kernel launches.

We acknowledge that the methodology presented in Paper I requires attention to many intriguing programming details, which can be difficult to grasp. Hence, in order to make the techniques presented in Paper I accessible to more scientists, it could be worth investigating different ways to abstract its complexity. One possible idea could be to provide a library or C++ template that automatically hides the more tedious programming details.

The technique presented in Papers II and III uses a fine-grained approach to utilizing both CPU and GPU for computations. The experiments conducted in both of the papers demonstrate that a conjoined CPU+GPU approach increases the overall computational

Introduction 6. Discussion

speed. If the difference in the realistically achievable performance between CPUs and GPUs stays at the current level, combining CPUs and GPUs will remain an attractive alternative, and thus worth exploring.

Although the fine-grained threading approach of Papers II and III leads to a good overlap of computations and inter-node communication, intra-node communication is still an unresolved issue, as described in Paper III. Another weakness of the approach is when compute nodes are equipped with multiple GPUs. As both Paper II and III show, the introduction of additional GPUs widens the performance gap between the CPUs and the GPUs even further. To support two GPUs per node in Papers II and III, an MPI process was created for each GPU and the CPU cores were divided equally between the different MPI processes. The downside of this strategy is that the CPU's performance is substantially degraded, because each MPI process will have only access to half of the memory bandwidth and half of the shared cache [9].

A natural extension of the programming methodology presented in Papers II and III would be to implement the strategy presented in Paper I, as it minimizes the use of MPI processes and reduces intra-node communication overhead. One key feature of the methodology presented in Paper I was to use multiple CPU threads to control multiple GPUs. This would mean that a single MPI process would control multiple GPUs.

Although this thesis has focused solely on GPUs, the findings of Paper I-IV are also applicable to Xeon Phis. Currently, the difference in peak floating point capability between a CPU and a Xeon Phi is similar to the difference between a CPU and a GPU. Thus, a similar speedup should be expected in a heterogeneous CPU+Xeon Phi implementation too.

The first and foremost limitation of our work in Paper IV is its being domain-specific. Although such a limitation restricts the outreach of our work, we believe that our domain choice is large enough to carry out meaningful translations that would not be possible with a more generic approach.

Performance wise, one of the biggest performance limiters of the work presented in Paper IV is the lack of highly optimized CPU code when hybrid CPU+GPU code is generated. Fast CPU code is a necessity in order to narrow the computational performance gap between the CPU and the GPU. In the work presented so far, the CPU's straightforward compute loops are not modified, and as one of the conclusions of Paper II, the CPU's workload ratio must be lowered to catch up with the GPU. On the other hand, an aggressively handwritten CPU code that performs 3D cache blocking [38] in combination with optimal block sizes will mean that the CPUs will handle more computational work in a CPU+GPU implementation.

CPU optimization techniques have been an on-going research topic for many years and numerous works show that cache blocking [12, 30, 38, 51, 60, 68] is an effective strategy to improve the performance of stencil codes on the CPU. There are already many impressive frameworks [22, 61] and code-generators [4, 9, 16] that are capable of generating high-quality CPU code. Hence, instead of writing a new module in Panda, an alternative would be to review the possibility of adding support from an existing tool to generate optimized CPU code.

Another limitation of Panda is that it is unable to recognize and translate code on subscripted multi-dimensional arrays (e.g. U[i][j][k]). There are many reasons why

6. Discussion Introduction

Panda only supports flat arrays. First of all, serial C/C++ performance programmers tend to prefer flattened arrays. Moreover, flat arrays map perfectly to how (linear) memory is allocated in CUDA, which creates a 1:1 mapping, and thus simplifies the process of code generation. The use of multi-dimensional arrays complicates the CUDA translation, as it requires that the compiler flattens the arrays or that special CUDA data structures such as cudaPitchPtr are used. Furthermore, in many scientific codes, data are often not laid out contiguously in memory. Flat arrays rely on special *incrementors* that automatically compute the array index. We support non-contiguous data layout by identifying and transforming the incrementor. Panda is capable of automatically identifying these incrementors, and thus supporting arrays that are laid non-contiguous in memory.

Despite some of its drawbacks, subscripted multi-dimensional arrays are more widespread in codes written by domain scientists, as it is syntactically closer to the actual mathematical notation. Adding support for subscripted multi-dimensional arrays should not pose a major problem, but requires an additional flag so that critical translator modules such as the *Stencil Analyzer* module are made aware of the new data layout. A benefit of supporting multi-dimensional arrays is that it will make the process of performing stencil analysis less complicated.

Panda is able to recognize and analyze stencils with a wider reach than 6 points to its neighbors. However, code generation of MPI communication and halo boundary computation of the corners that have more than 6 neighbors, has not been implemented yet. So far, our focus has been on laying the foundation for a framework capable of auto-generating MPI, MPI+CUDA, and MPI+CUDA+OpenMP code.

One and two-dimensional codes are not supported because we have only focused on 3D problems, which pose the biggest challenge with respect to both communication and computations. However, there are many real-world applications that are one or two-dimensional, such as spherulitic crystallization and channel crystallization, two common problems in the field of polymer physics. In order to support one and two-dimensional problems, the *Directive Manager* must communicate the dimension of the problem, which can be detected by looking at the number of parameters passed to the size clause, to the *Stencil Analyzer* module. Once the *Stencil Analyzer* module has been made aware of the problem's dimension, it can perform analysis within an appropriate space.

Another limitation in Panda is the lack of support for parallel I/O and checkpointing. Parallel I/O is an important component in HPC applications when it comes to tasks such as visualization or reading user-input. The limitation of handling parallel I/O can be addressed by introducing a directive specifically for dealing with I/O, and a clause that lets the user to specify the rank identifier of one or a range of ranks. Currently, Panda does not support application-level checkpointing primarily due to the lack of parallel I/O support. In other words, before checkpointing can be supported, the limitations of parallel I/O must be resolved first. Once parallel I/O is supported, special directives can be developed to let the user indicate areas of interest for checkpointing.

Introduction 7. Conclusion

#### 7 Conclusion

The main goal of this thesis is to contribute to the improvement and development of novel programming methodologies and tools for computational scientists. Paper I focused on the complex interactions and intra-node communication between multiple GPUs that are located on the same node. It is highly anticipated that both upcoming heterogeneous Petascale [2, 42] and future Exascale [1] systems will adopt a node architecture where each node is densely populated with multiple manycore processors such as GPUs. In these systems, reducing the cost associated with intra-node communication will become crucial. We expect that the programming techniques detailed in Paper I will make an important contribution towards reducing intra-node communication costs, which arise when multiple GPUs are installed on the same node.

The focus of Paper II was on achieving higher compute performance by taking advantage of the increasing computational power offered by modern CPUs by performing concurrent CPU+GPU computations. A big challenge in heterogeneous CPU+GPU computing is to find an appropriate CPU workload ratio that is neither too high nor too low. We have derived a simple performance model for predicting balanced CPU workloads with CPU+GPU computing in mind. Experimental results of a simple 7-point 3D stencil benchmark application on a structured grid showed that our heterogeneous CPU+GPU codes were able to outperform a corresponding GPU-only implementation by a large margin and that our performance model did a good job of predicting a balanced CPU workload ratio. The contributions of Paper II are detailed insights into an advanced programming technique where task parallelism was used to make efficient use of CPUs and GPUs and an ancillary performance model to predict an appropriate CPU workload ratio.

Motivated by the performance results in Paper II, a more challenging application for performing heterogeneous CPU+GPU computations was chosen. The chosen application solves the diffusion equation using the finite volume method on tetrahedral meshes. Experimental results using up to 128 GPUs on the Stampede supercomputer showed that the heterogeneous CPU+GPU version was on average 43% faster than the GPU-only version. Paper III confirmed our findings from Paper II that conjoining the computational capacity of the CPU with the GPU increases the application performance. Moreover, Paper III contributes in giving detailed insights into the development of heterogeneous CPU+GPU applications for unstructured meshes.

Paper IV makes contributions in the development of a novel automated code generator for performing heterogeneous CPU+GPU computations. The tool, called Panda, is currently at the proof-of-concept stage and has many limitations, but is nonetheless capable of parallelizing simple 7-point 3D stencil codes written in sequential C. In order to assess the performance of the auto-generated code, a series of experiments were conducted using the 3D stencil benchmark from Paper II and a real-world application in cardiac modeling. For evaluation purposes, aggressively optimized versions of the two applications were handwritten. The first version performed heterogeneous CPU+GPU computations, while the second version performed computations exclusively on the GPU. Experiments showed that the Panda-generated code was able to realize 90% of the performance of the handwritten versions. However, an important finding was that the Panda-code was always able to outperform the handwritten GPU-only code. The promising results are achieved

7. CONCLUSION INTRODUCTION

primarily because Panda implements many generalized versions of the programming techniques unveiled in Papers II and III.

This thesis has thus shed some light on increasing the efficiency of memory-bound HPC applications by performing concurrent CPU+GPU computations and by providing computational scientists with a tool that can automatize the development of such applications.

#### Bibliography

- 1. Ang, J., R. Barrett, R. Benner, D. Burke, C. Chan, J. Cook, D. Donofrio, S. Hammond, K. Hemmert, S. Kelly, H. Le, V. Leung, D. Resnick, A. Rodrigues, J. Shalf, D. Stark, D. Unat, and N. Wright (2014, November). Abstract machine models and proxy architectures for exascale computing.

- 2. Argonne Leadership Computing Facility (2015). Aurora. http://aurora.alcf.anl. gov/. [Online; accessed 1-June-2015].

- 3. Augonnet, C., S. Thibault, R. Namyst, and P.-A. Wacrenier (2011, February). StarPU: A unified platform for task scheduling on heterogeneous multicore architectures. *Concurr. Comput.: Pract. Exper.* 23(2), 187–198.

- 4. Bandishti, V., I. Pananilath, and U. Bondhugula (2012, November). Tiling stencil computations to maximize parallelism. In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis*, pp. 40:1–40:11.

- 5. Bernaschi, M., M. Bisson, and D. Rossetti (2013, February). Benchmarking of communication techniques for GPUs. *Journal of Parallel and Distributed Computing 73*, 250–255.

- 6. Bosilca, G., A. Bouteiller, A. Danalis, T. Herault, P. Lemarinier, and J. Dongarra (2012). DAGuE: A generic distributed DAG engine for high performance computing. *Parallel Computing* 38(1–2), 37–51.

- 7. Brodtkorb, A. R., C. Dyken, T. R. Hagen, J. M. Hjelmervik, and O. O. Storaasli (2010, January). State-of-the-art in heterogeneous computing. *Sci. Program.* 18(1), 1–33.

- 8. Che, S., M. Boyer, J. Meng, D. Tarjan, J. W. Sheaffer, and K. Skadron (2008). A performance study of general-purpose applications on graphics processors using {CUDA}. *Journal of Parallel and Distributed Computing* 68(10), 1370–1380.

- 9. Christen, M., O. Schenk, and B. Burkhart (2011, May). PATUS: A Code Generation and Autotuning Framework for Parallel Iterative Stencil Computations on Modern Microarchitectures. In *Parallel Distributed Processing Symposium (IPDPS)*, 2011 IEEE International, pp. 676–687.

- 10. Datta, K., S. Kamil, S. Williams, L. Oliker, J. Shalf, and K. Yelick (2009). Optimization and performance modeling of stencil computations on modern microprocessors. *SIAM Review* 51(1), 129–159.

- 11. Diaz, J., C. Munoz-Caro, and A. Nino (2012, August). A survey of parallel programming models and tools in the multi and many-core era. *IEEE Trans. Parallel Distrib. Syst.* 23(8), 1369–1386.

- 12. Frigo, M. and V. Strumpen (2005). Cache oblivious stencil computations. In *Proceedings* of the 19th Annual International Conference on Supercomputing, pp. 361–366.

- 13. Gillberg, T., M. Sourouri, and X. Cai (2012, June). A new parallel 3d front propagation algorithm for fast simulation of geological folds. In *Proceedings of the International Conference on Computational Science*, *{ICCS} 2012*, pp. 947–955.

- 14. Grosser, T., A. Cohen, J. Holewinski, P. Sadayappan, and S. Verdoolaege (2014, February). Hybrid hexagonal/classical tiling for GPUs. In *Proceedings of Annual IEEE/ACM International Symposium on Code Generation and Optimization*, pp. 66:66–66:75.

- 15. Hammarlund, P., A. J. Martinez, A. A. Bajwa, D. L. Hill, E. Hallnor, H. Jiang, M. Dixon, M. Derr, M. Hunsaker, R. Kumar, R. B. Osborne, R. Rajwar, R. Singhal, R. D'Sa, R. Chappell, S. Kaushik, S. Chennupaty, S. Jourdan, S. Gunther, T. Piazza, and T. Burton (2014). Haswell: The fourth-generation intel core processor. *IEEE Micro* 34(2), 6–20.

- 16. Henretty, T., R. Veras, F. Franchetti, L.-N. Pouchet, J. Ramanujam, and P. Sadayappan (2013, June). A stencil compiler for short-vector simd architectures. In *Proceedings of the 27th International ACM Conference on International Conference on Supercomputing*, pp. 13–24.

- 17. Holewinski, J., L.-N. Pouchet, and P. Sadayappan (2012). High-performance Code Generation for Stencil Computations on GPU Architectures. In *Proceedings of the 26th ACM International Conference on Supercomputing*, pp. 311–320.

- 18. Huang, C., G. Zheng, L. Kalé, and S. Kumar (2006, March). Performance evaluation of adaptive mpi. In *Proceedings of the Eleventh ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming*, pp. 12–21.

- 19. Intel Corporation (2015). Intel Hyper-Threading Technology. http://www.intel.com/content/www/us/en/architecture-and-technology/hyper-threading-technology.html. [Online; accessed 27-September-2015].

- 20. Jacobsen, D., J. Thibault, and I. Senocak (2010, January). An MPI-CUDA implementation for massively parallel incompressible flow computations on multi-GPU clusters. In *Proceedings of the 48th AIAA Aerospace Sciences Meeting*.

- 21. Ji, F., A. M. Aji, J. Dinan, D. Buntinas, P. Balaji, W.-C. Feng, and X. Ma (2012, May). Efficient intranode communication in GPU-accelerated systems. 2012 IEEE 26th International Parallel and Distributed Processing Symposium Workshops & PhD Forum, 1838–1847.

- 22. Kamil, S., C. Chan, L. Oliker, J. Shalf, and S. Williams (2010, April). An auto-tuning framework for parallel multicore stencil computations. In *Parallel Distributed Processing (IPDPS)*, 2010 IEEE International Symposium on, pp. 1–12.

- 23. Khronos Group (2015). OpenCL the open standard for parallel programming of heterogeneous systems. https://khronos.org/opencl/. [Online; accessed 25-May-2015].

- 24. Kim, N., T. Austin, D. Baauw, T. Mudge, K. Flautner, J. Hu, M. Irwin, M. Kandemir, and V. Narayanan (2003, Dec). Leakage current: Moore's law meets static power. *Computer 36*(12), 68–75.

- 25. Kjolstad, F. B. and M. Snir (2010, March). Ghost cell pattern. In *Proceedings of the 2010 Workshop on Parallel Programming Patterns*, pp. 4:1–4:9.

- 26. Krishnasamy, E., M. Sourouri, and X. Cai (2015, June). Multi-GPU implementations of parallel 3D sweeping algorithms with application to geological folding. In *Proceedings of the International Conference on Computational Science*, *{ICCS} 2015*, pp. 1494–1503.

- 27. Langguth, J. and X. Cai (2014, December). Heterogeneous CPU-GPU computing for the finite volume method on 3D unstructured meshes. In *Parallel and Distributed Systems (ICPADS)*, 2014 20th IEEE International Conference on, pp. 191–199.

- 28. Langguth, J., M. Sourouri, G. T. Lines, S. B. Baden, and X. Cai (2015, July). Scalable heterogeneous CPU-GPU computations for unstructured tetrahedral meshes. *Micro, IEEE 35*(4), 6–15.

- 29. Lawrence Livermore National Laboratory (2015). ROSE compiler infrastructure. http://rosecompiler.org. [Online; accessed 04-June-2015].

- 30. Lee, V. W., C. Kim, J. Chhugani, M. Deisher, D. Kim, A. D. Nguyen, N. Satish, M. Smelyanskiy, S. Chennupaty, P. Hammarlund, R. Singhal, and P. Dubey (2010). Debunking the 100X GPU vs. CPU myth: An evaluation of throughput computing on CPU and GPU. In *Proceedings of the 37th Annual International Symposium on Computer Architecture*, pp. 451–460.

- 31. Levesque, J. M., R. Sankaran, and R. Grout (2012, November). Hybridizing S3D into an exascale application using OpenACC: An approach for moving to multi-petaflops and beyond. In *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis*, pp. 15:1–15:11.

- 32. Maruyama, N. and T. Aoki (2014, January). Optimizing stencil computations for nvidia kepler GPUs. In *Proceedings of the 1st International Workshop on High-Performance Stencil Computations*, pp. 89–95.

- 33. McCalpin, J. D. (1995, December). Memory bandwidth and machine balance in current high performance computers. *IEEE Computer Society Technical Committee on Computer Architecture (TCCA) Newsletter*, 19–25.

- 34. Message Passing Interface Forum (2012, September). MPI: A Message-Passing Interface Standard, Version 3.0. High Performance Computing Center Stuttgart (HLRS).

- 35. Micikevicius, P. (2009, March). 3D finite difference computation on GPUs using CUDA. In *Proceedings of 2nd Workshop on General Purpose Processing on Graphics Processing Units GPGPU-2*, pp. 79–84.

- 36. Mittal, S. and J. S. Vetter (2015). A Survey of CPU-GPU Heterogeneous Computing Techniques. *ACM Comput. Surv.* 47(4).

- 37. MVAPICH (2015). MPI over InfiniBand, 10GigE/iWARP and RDMA over Converged Ethernet (RoCE). http://mvapich.cse.ohio-state.edu. [Online; accessed 25-September-2015].

- 38. Nguyen, a., N. Satish, J. Chhugani, C. K. C. Kim, and P. Dubey (2010, November). 3.5-D Blocking Optimization for Stencil Computations on Modern CPUs and GPUs. In *Proceedings of 2011 International Conference for High Performance Computing, Networking, Storage and Analysis*, pp. 1–13.

- 39. Nguyen, T., P. Cicotti, E. Bylaska, D. Quinlan, and S. B. Baden (2012, November). Bamboo: translating MPI applications to a latency-tolerant, data-driven form. In *Proceedings of the 2012 International Conference on High Performance Computing, Networking, Storage and Analysis*, pp. 39:1–39:11.

- 40. NVIDIA (2015a). CUDA C programming guide. http://docs.nvidia.com/cuda/cuda-c-programming-guide/. [Online; accessed 25-May-2015].

- 41. NVIDIA (2015b). NVIDIA GPUDirect. https://developer.nvidia.com/gpudirect. [Online; accessed 04-March-2015].

- 42. Oak Ridge Leadership Computing Facility (2015). Summit. https://olcf.ornl.gov/summit/. [Online; accessed 29-May-2015].

- 43. OpenACC Directives for Accelerators (2015). The OpenACC Application Program Interface. http://openacc-standard.org. [Online; accessed 23-May-2015].

- 44. OpenMP Architecture Review Board (2015). OpenMP Application Program Interface. http://openmp.org. [Online; accessed 23-May-2015].

- 45. OpenMPI (2015). Open Source High Performance Computing. http://http://www.open-mpi.org. [Online; accessed 25-September-2015].

- 46. Phillips, E. H. and M. Fatica (2010, April). Implementing the Himeno benchmark with CUDA on GPU clusters. In *Parallel Distributed Processing (IPDPS)*, 2010 IEEE International Symposium on, pp. 1–10.

- 47. Playne, D. P. and K. A. Hawick (2011, July). Asynchronous communication for finite-difference simulations on GPU clusters using CUDA and MPI. In *International Conference on Parallel and Distributed Processing Techniques and Applications*, pp. 169–174.

- 48. Potluri, S., H. Wang, D. Bureddy, A. K. Singh, C. Rosales, and D. K. Panda (2012, May). Optimizing MPI communication on multi-GPU systems using CUDA inter-process communication. In *Parallel and Distributed Processing Symposium Workshops PhD Forum (IPDPSW)*, 2012 IEEE 26th International, pp. 1848–1857.

- 49. Ragan-Kelley, J., C. Barnes, A. Adams, S. Paris, F. Durand, and S. Amarasinghe (2013). Halide: A language and compiler for optimizing parallelism, locality, and recomputation in image processing pipelines. In *Proceedings of the 34th ACM SIGPLAN Conference on Programming Language Design and Implementation*, pp. 519–530.

- 50. Rietmann, M., P. Messmer, T. Nissen-Meyer, D. Peter, P. Basini, D. Komatitsch, O. Schenk, J. Tromp, L. Boschi, and D. Giardini (2012, November). Forward and adjoint simulations of seismic wave propagation on emerging large-scale GPU architectures. In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis*, pp. 38:1–38:11.

- 51. Rivera, G. and C.-W. Tseng (2000). Tiling optimizations for 3D scientific computations. In *Proceedings of the 2000 ACM/IEEE Conference on Supercomputing*.

- 52. San Diego Supercomputer Center HPC Systems (2015). http://www.sdsc.edu/services/hpc/hpc\_systems.html#comet. [Online; accessed 25-September-2015].

- 53. Satish, N., C. Kim, J. Chhugani, and P. Dubey (2012, November). Large-scale energy-efficient graph traversal: A path to efficient data-intensive supercomputing. In *Proceedings of the International Conference on High Performance Computing, Networking, Storage and Analysis*, pp. 14:1–14:11.

- 54. Schäfer, A. and D. Fey (2011, June). High performance stencil code algorithms for GPGPUs. In *Proceedings of 2011 International Conference on Computational Sciences (ICCS)*, Volume 4, pp. 2027–2036.