### Hardware context switching on FPGAs

Sindre Georgsen

Department of Physics University of Oslo

31st March 2014

### **Abstract**

FPGAs have the ability to replace its hardware modules without disrupting the execution of the other modules of the system. This is called *dynamic partial reconfiguration*. The capability to dynamically replace a hardware module with another, while the rest of the system is still running, could have a major impact on a design in such way that a smaller device can be used to implement a great and complex system. The reconfiguration attribute would become even more advantageous if the modules were allowed to *pause* so that the module didn't have to start at the beginning each time it was reintroduced to the system, it could resume from where it was, when replaced. This feature of partial reconfiguration is called *context switching*. Context switching must be able to preserve a modules internal state and its memory contents in order for the module to continue from where it was, in the execution time-domain, when reintroduced.

A challenge of the partial reconfiguration property is that it is time consuming, especially if frequent context switching is taking place. In this thesis, a bitstream manipulator module is implemented in *hardware* to decrease the time consumption of context switching. The module creates a new partial configuration file based on the initial configuration file, readback file of the captured flip-flop values, and the masking file generated by the Xilinx tool ISE. An external memory is the module repository, which holds all necessary and generated files for each partial module. It is this methodology that decreases the time consumption of context switching.

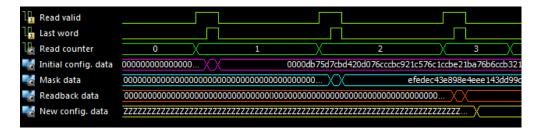

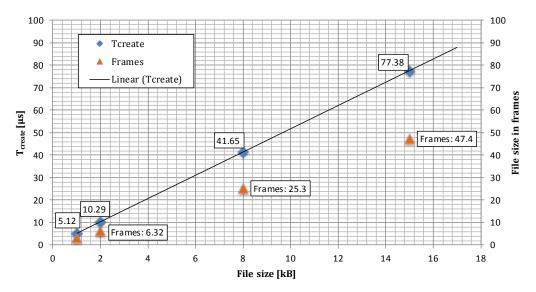

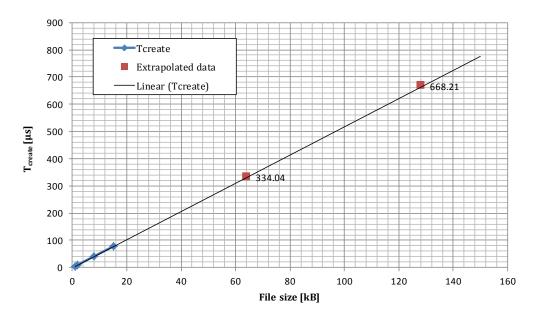

Simulation shows that the system performance of the process of creating a new partial configuration file is *three orders of magnitude* faster compared to the most relevant research work. The creation of a new partial configuration file is measured to 5.12  $\mu$ s for a file size of 1 kB (1024 bytes), and 47.7  $\mu$ s for a file size of 15 kB. The results are promising, and further investigation will probably result in a step closer to realizing a satisfactory partial reconfigurable system that includes context switching.

### **Preface**

When choosing a master project I had two options, either contact companies in the electronic industry, and ask if they had any projects suited for a master student, or I could choose a project given by a research group at the university. I checked for available projects at the university, and I found a few projects related to FPGA and reconfiguration. I read the description of the projects and I was immediately fascinated by the one titled 'High speed context switching on FPGAs'. My supervisor warned me that the project might be comprehensive, but I enjoy a challenge very much so I chose the project, and began enthusiastically.

A Spartan-6 device was chosen because of its relatively small architecture, and it is a low-cost device. I spent couple of weeks searching for articles and documentation on the subject of partial reconfiguration and context switching, and another two weeks trying to figure out the composition of the configuration file; which bit in the configuration file corresponds to which flip-flop in the device. I discovered that the manufacturer of the FPGA device is not so eager to share information about the Spartan-6 configuration. My supervisor and I made a choice; Spartan-6 was unsuited for the tasks at hand due to lack of documentation and the limited time span of the project. Virtex-6 suited better because of its capability to perform a capture of registers.

Most previous work on the subject so far has used an embedded CPU to control and to initiate the reconfiguration and context switching process. I've already had an idea of how the system should work; using external memory and make the bitstream manipulation module interact directly with the memory, *without* the use of a CPU. This approach would make the context switching process go faster.

Although Xilinx provides an IP core for controlling the external DDR3 memory, the documentation for it was not that impressive, some information was directly contradicting, and some information was not related to the current IP version. Due to poor documentation I spent a considerable amount of time going through forum threads searching for answers. It took me about two months to finally achieve a working memory controller that suited my needs. I was now about half way into the project with regards to time, and I realized that I had to moderate my goals, and even abandon a goal in order to produce some results. I focused on bitstream manipulation since that was in fact the main goal of the project. Implementation of a partial reconfigurable region is therefore not included, and it is assumed that is available. By doing these cutbacks I managed to generate some valuable results.

I would like to thank my supervisor, Professor Jim Tørresen, for being critical and for asking questions that challenged me. I would also thank PhD student Alexander Wold for giving me assistance when I desperately needed it.

## Contents

| A | bstra  | ict   |                                             | i   |

|---|--------|-------|---------------------------------------------|-----|

| P | refac  | e     |                                             | iii |

| L | ist of | figu  | ires                                        | ix  |

| L | ist of | tabl  | les                                         | xi  |

| 1 | In     | troc  | luction                                     | 1   |

|   | 1.1    | Sc    | ope of the thesis                           | 2   |

|   | 1.2    | Ch    | apter overview                              | 2   |

| 2 | Ва     | ackg  | round and theory                            | 5   |

|   | 2.1    | Ch    | apter overview                              | 5   |

|   | 2.2    | Fie   | eld programmable gate array                 | 5   |

|   | 2.3    | Co    | onfiguration                                | 7   |

|   | 2.4    | Pa    | rtial Reconfiguration                       | 8   |

|   | 2.     | 4.1   | Static region                               | 9   |

|   | 2.     | 4.2   | Partial region                              | 9   |

|   | 2.5    | Co    | ntext switching                             | 10  |

|   | 2.     | 5.1   | Context switching in software               | 10  |

|   | 2.     | 5.2   | Hardware context switching                  | 10  |

|   | 2.6    | Xil   | linx Virtex-6 FPGA configuration            | 12  |

|   | 2.     | 6.1   | Configuration interfaces                    | 12  |

|   | 2.     | 6.2   | Configuration frames and frame addressing   | 14  |

|   | 2.     | 6.3   | Configuration packets                       | 15  |

|   | 2.     | 6.4   | Configuration registers                     | 16  |

|   | 2.     | 6.5   | Configuration readback and register capture | 18  |

|   | 2.     | 6.6   | Xilinx ISE configuration options            | 19  |

| 3 | Re     | elate | ed research                                 | 21  |

|   | 3.1    | Ch    | apter overview                              | 21  |

|   | 3.2    | Re    | esearch papers                              | 21  |

|   | 3.3    | Su    | mmary                                       | 24  |

| 4 | T      | 1 .   | montation                                   | 25  |

| 7 | Ril | alioc | ranhy                                      | 50 |

|---|-----|-------|--------------------------------------------|----|

|   | 6.3 | .4    | Use Enhanced ICAP hard macro               | 57 |

|   | 6.3 | .3    | Increase DDR3 memory controller efficiency | 56 |

|   | 6.3 | .2    | Advanced CSMC with a scheduler             | 56 |

|   | 6.3 | .1    | Complete the design                        | 56 |

|   | 6.3 | Fut   | cure work                                  | 56 |

|   | 6.2 | Cor   | nclusion                                   | 55 |

|   | 6.1 | Cha   | apter overview                             | 55 |

| 6 | Co  | nclu  | sion and future work                       | 55 |

|   | 5.5 | Cor   | nparison                                   | 52 |

|   | 5.4 | Me    | asurements                                 | 50 |

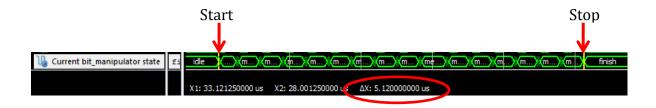

|   | 5.3 | DM    | IC and BMM simulation                      | 49 |

|   | 5.2 | Sim   | nulation set-up                            | 47 |

|   | 5.1 | Cha   | apter overview                             | 47 |

| 5 | Sin | nula  | tion and measurements                      | 47 |

|   | 4.6 | .7    | ICAP instruction memory module             | 45 |

|   | 4.6 |       | Data width converter                       | 45 |

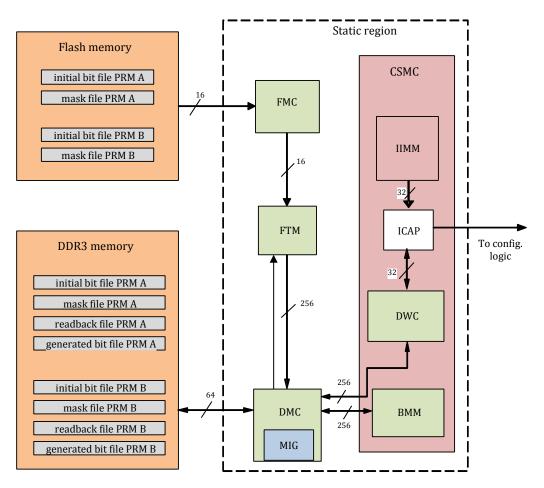

|   | 4.6 |       | Bitstream manipulator module               | 42 |

|   | 4.6 |       | File transfer module                       | 40 |

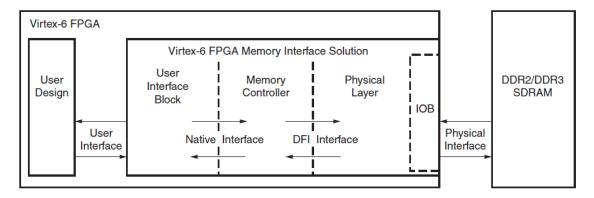

|   | 4.6 |       | DDR3 memory controller                     | 34 |

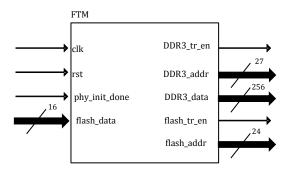

|   | 4.6 |       | Flash memory controller                    | 34 |

|   | 4.6 |       | Context switching main controller          | 33 |

|   | 4.6 |       | dule descriptions                          | 33 |

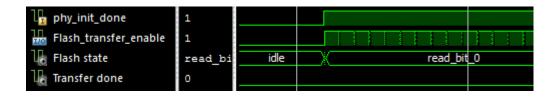

|   | 4.5 | .2    | System operation                           | 32 |

|   | 4.5 | .1    | Data flow                                  | 32 |

|   | 4.5 | Imp   | plemented system                           | 30 |

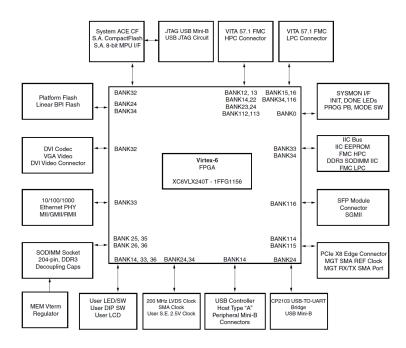

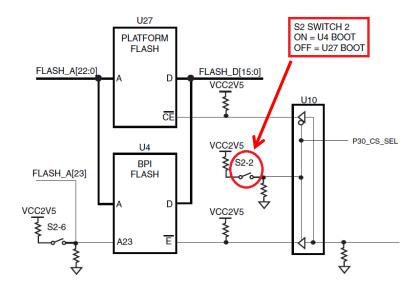

|   | 4.4 | .4    | ML605 configuration mode switch            | 30 |

|   | 4.4 | .3    | SDRAM memory                               | 29 |

|   | 4.4 | .2    | Flash memory                               | 29 |

|   | 4.4 | .1    | Virtex-6 XC6VLX240T-1 device               | 29 |

|   | 4.4 | Hai   | rdware platform                            | 28 |

|   | 4.3 | Sys   | tem overview                               | 26 |

|   | 4.2 |       | etem Concept                               | 25 |

|   | 4.1 | Cha   | apter overview                             | 25 |

# List of figures

| 2.1 - Simplified architecture of an FPGA                                        | 5  |

|---------------------------------------------------------------------------------|----|

| 2.2 - Embedded hard core CPU (a), and Embedded RAM and DSP (b)                  | 6  |

| 2.3 - SRAM based LUT                                                            | 6  |

| 2.4 - Uniform clock distribution                                                | 7  |

| 2.5 - Configuration sequence                                                    |    |

| 2.6 - Different styles of partial reconfigurable regions                        |    |

| 2.7 - Time and logic overhead for hardware checkpointing techniques             |    |

| 2.8 - Virtex-6 configuration architecture.                                      |    |

| 2.9 - Data from an actual configuration file for a Virtex-6 device              |    |

| 2.10 - Misalignment of file contents                                            | 19 |

| 4.1 - Concept of partial reconfiguration with context switching                 | 25 |

| 4.2 - Time multiplexed hardware sharing                                         |    |

| 4.3 - Details of the context switching in figure 4.2                            | 26 |

| 4.4 - The four phases of operations of the system                               |    |

| 4.5 - ML605 block schematic                                                     | 28 |

| 4.6 - Flash memory selector                                                     |    |

| 4.7 - Implemented system and data flow                                          |    |

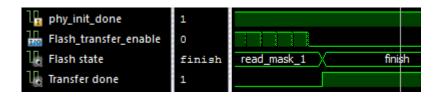

| 4.8 - File transfer begins when the DDR3 initialization and calibration is done | 32 |

| 4.9 - The transfer_done signal indicates the completion of file transfer        |    |

| 4.10 - MIG interfaces                                                           |    |

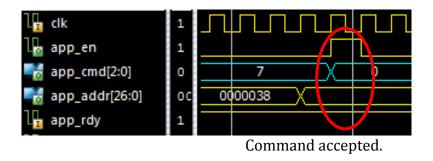

| 4.11 - Command path                                                             |    |

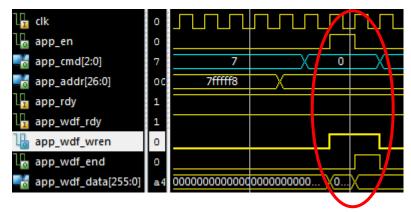

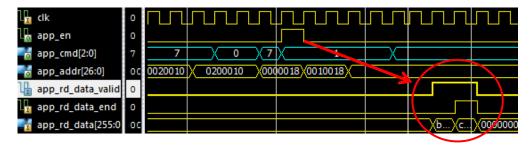

| 4.12 - Write path                                                               |    |

| 4.13 - Read path                                                                |    |

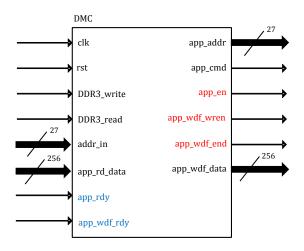

| 4.14 - I/O ports of the DMC                                                     |    |

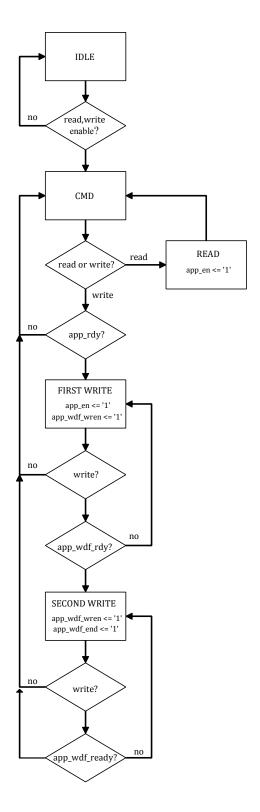

| 4.15 - State machine for DMC                                                    |    |

| 4.16 - The file transfer module and its ports.                                  |    |

| 4.17 - Start-up counter inhibits writing invalid data to DDR3                   | 41 |

| 4.18 - Invalid data between files                                               |    |

| 4.19 - Valid data between files.                                                |    |

| 4.20 - Process of creating new partial configuration file                       |    |

| 4.21 - Calculating the DDR3 file end address                                    |    |

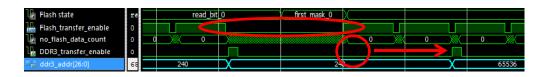

| 4.22 - Equation 2.1 realized in hardware                                        |    |

| 4.23 - Simplified ASM of the bitstream manipulator FSM                          | 44 |

| 5.1 - Example design provided by the MIG IP core                                |    |

| 5.2 - Delay from read command is given till the data is available               |    |

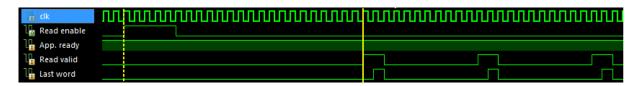

| 5.3 - De-assertion of app_rdy after reading from three addresses                |    |

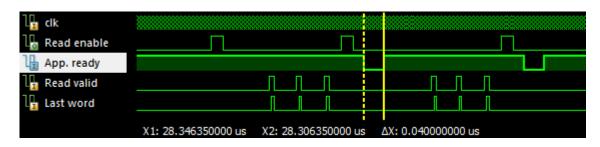

| 5.4 - Storing data in local registers                                           |    |

| 5.5 - Measurement method                                                        |    |

| 5.6 - Plot of the result from the simulation data                               |    |

| 5.7 - Plot of the extrapolated data                                             | 51 |

## List of tables

| 2.1 - Configuration pins                                                    | 13 |

|-----------------------------------------------------------------------------|----|

| 2.2 - Frame address format                                                  | 15 |

| 2.3 - Configuration packet, type 1.                                         | 15 |

| 2.4 - Configuration packet, type 2.                                         | 15 |

| 2.5 - Configuration register operations                                     |    |

| 2.6 - Configuration registers essential for reconfiguration                 | 16 |

| 2.7 - Essential instructions in the CMD register related to reconfiguration | 16 |

| 2.8 - Example of decoding the configuration file                            | 18 |

| 3.1 - Context switching requirements                                        | 21 |

| 3.2 - Summary of essential parameters.                                      |    |

| 4.1 - Configuration mode switch settings                                    | 30 |

| 4.2 - Control signals for read operation of the flash memory                | 34 |

| 4.3 - Control and status signals from the MIG user interface                |    |

| 5.1 - Available options for reducing the simulation time                    | 48 |

| 5.2 - Meausrement results                                                   | 50 |

| 5.3 - Extrapolated data                                                     |    |

| 5.4 - Data rate of the creating new bit file process                        | 52 |

| 5.5 - Measurements from relevant research                                   |    |

| 5.6 - Results from A. Morales                                               |    |

|                                                                             |    |

### ${f 1}$ Introduction

Field programmable gate array (FPGA) is a highly flexible integrated circuit that is programmable in the field. With an FPGA, complex digital circuits can be realized, and true parallelism is one of its many strengths. Another feature is *partial reconfiguration* (PR); meaning that parts of the FPGA can be reprogrammed, or reconfigured, in the field while the rest of the FPGA is running. The same reconfigurable area can be reconfigured many times over and that enables timesharing of hardware resources, i.e. two or more digital circuits can share the same area, on the FPGA, over time.

PR can be used in many different ways. For instance, a design may operate with several modes where each mode may demand a specialized module, and when that mode is activated the partial reconfigurable area is configured with the required module. Another possibility is when a design has more than one start-up configuration and a selector determines which configuration should be used. A third possibility is that two or more modules continuously switch turns running on the partial reconfigurable region (PRR). The currently running module can then be paused before it is swapped with another module. Pausing a module means that the modules internal states, i.e. its register values, are stored. The stored information can then be retrieved when the modules is swapped back in, so that the module does not have to begin from the start again. This method is called *context switching*. A more comprehensive discussion on context switching can be found in chapter 2.5.

Although PR has been available for many years, it has not yet been adopted by the industry on a large scale. A major contributing factor to its unfavorable status is that the process of reconfiguring the targeted area on the FPGA is time consuming and may be cumbersome to implement. The speed of partial reconfiguration is in many cases the essential factor, but there may be situations where the switching frequency is of less importance as exemplified in the 'mode' example above. However, there are benefits associated with PR and context switching. By sharing hardware resources, a smaller device can be used, and hence reduce the cost, mutual exclusive modules may be implemented on the same device, among others.

There has been extensive research on the subject in academia for several years and it has progressed a lot since it was first introduced, see chapter 3.2 for the most relevant research related to partial reconfiguration in general and context switching in particular. There are two main methods of partial reconfiguration that includes context switching. One is to use a soft core embedded microprocessor like the MicroBlaze and write software that will perform all operations needed. This is the most widely used approach. The other is to design a hardware version without the use of a microprocessor. The latter is the approach chosen for this thesis on context switching. This choice was made for the following two reasons. First, the hardware approach has not, to my knowledge, been investigated thoroughly enough and I think there is a potential for reducing the overall time consumption of the reconfiguration process compared to the software approach. Secondly, I wanted to gain experience in

VHDL, and to keep the abstraction level as low as possible in order to gain a greater understanding of an FPGA.

#### 1.1 Scope of the thesis

Three main goals were given in the thesis description, and are as follows:

- 1) Design a hardware module for filtering out the state out of configuration readback data from an FPGA.

- 2) Development of techniques for setting back a modules state.

- 3) Design and implementation of a demo system.

The first two goals must be defined more precisely in order to keep the tasks at hand as simple as possible due to limited duration of the thesis. They are also intertwined in such way that the second is dependent on the first. The first goal is, in here, defined to perform a capture of the internal registers of the partial reconfigurable module (PRM) at that point in time when it is ready for replacement, determined by a context switching main controller (CSMC). The captured data is then read back from the FPGAs internal configuration memory and stored in an external memory. The second goal is defined as constructing a *new* configuration file that contains the register information from the previously stored readback data. Both tasks include accessing an external memory for reading and storing of said data.

The third goal was unfortunately not reached. It is therefore assumed that the PRR has already been implemented, and that two PRMs are available. Further, all measurements given in chapter 5.4 are based on simulations rather than actual results from a demo system. These measurements are then extrapolated in order to give an accurate estimation beyond simulation results.

One issue regarding partial reconfiguration is security. To limit the extent of the thesis, this subject is not part of the thesis. See [1], [2] and [3] for a discussion on the security aspect.

#### 1.2 Chapter overview

#### Chapter 2 Background and theory

This chapter starts with a short description on the architecture of an FPGA. In section 2.3 a brief explanation of FPGA configuration is given. The chapter continues with the theory behind partial reconfiguration in section 2.4, and context switching in section 2.5. The final section goes deeper into configuration of a Virtex-6 FPGA with a description on configuration frames, packets and registers. This section also gives an example on how to decode a bitstream.

#### **Chapter 3** Relevant research

As mentioned in the introduction there has been extensive research on the subject of partial reconfiguration, but not as much on the issue of context switching. The most relevant work, to my knowledge, compared to this thesis is presented here. They are listed in order of increasing relevance.

#### **Chapter 4** Implementation

This chapter first explains the concept of the system that has been designed for this master thesis. Then follows an overview of the system, in section 4.3, where a functional explanation is given. The chapter continues to give a short description of the hardware platform used in the project. In section 4.5 the implemented system is described, the section gives an overview on the data flow, and an operational description is given. In the final section a detailed description on the implemented modules is given. Simulation captures and excerpt of the code is given when it is necessary to highlight a problem or to illustrate how they were solved.

#### **Chapter 5** Simulation and measurements

This chapter gives a description of the simulation environment and how the simulation was performed. Section 5.2 gives a detailed description on the set-up of the simulation. Section 5.3 takes a closer look at how the DMC and DDR3 memory responds to read requests from the BMM. Measurements and results are given in section 5.4, this section also includes some equation needed to calculate parameters related to configuration frames and timing. The results are plotted in a graph and data extrapolation is used to give a precise timing estimate beyond simulation. The final section compares the simulated results width previously conducted experiments from other relevant work mentioned in chapter 3.2.

#### **Chapter 6** Conclusion and future work

This chapter provides a conclusion of the work presented in the thesis. It also gives a few suggestions on how to improve the system in order to increase its functionality and effectiveness.

# **2** Background and theory

#### 2.1 Chapter overview

This chapter starts with a short description on the architecture of an FPGA. In section 2.3 a brief explanation of FPGA configuration is given. The chapter continues with the theory behind partial reconfiguration in section 2.4, and context switching in section 2.5. The final section goes deeper into configuration of a Virtex-6 FPGA with a description on configuration frames, packets and registers. This section also gives an example on how to decode a bitstream.

#### 2.2 Field programmable gate array

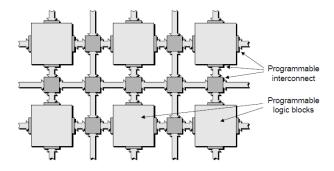

An FPGA consists of a matrix of programmable logic blocks which can be connected together through programmable interconnects. A network of wires, both horizontally and vertically, are situated between the logic blocks, see Figure 2.1. In addition, there are programmable input and outputs used for communication with external components. This makes the FPGA highly flexible and complex digital circuits can be realized. Bitcoin miner, software defined radio, advanced digital filters, video and image processing, and high performance parallel computing are some few examples.

Figure 2.1 - Simplified architecture of an FPGA [4]

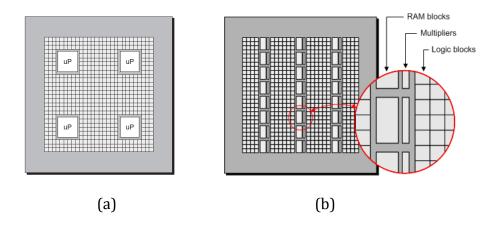

In addition to the logic blocks and the interconnects, an FPGA may contain dedicated embedded circuits such as digital signal processors (DSP), block RAM (BRAM) and even a hard core microprocessor, as illustrated in figure 2.2 This makes the FPGA highly versatile and powerful.

Figure 2.2 - Embedded hard core CPU (a), and Embedded RAM and DSP (b) [4]

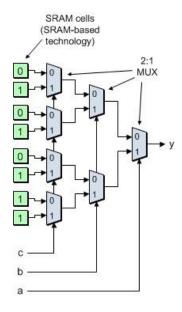

Each logic block, or configurable logic block (CLB) as Xilinx calls them, consists of slices and each slice contains logic cells, which comprises flip-flops and look-up tables (LUT), usually twice as many flip-flops as LUTs. Most modern FPGA devices are static RAM (SRAM) based; the LUTs are SRAM cells that hold the desired logical values corresponding to the implemented function, see figure 2.3.

Figure 2.3 - SRAM based LUT.

There are different types of slices, each with different complexity and functionality. For the Xilinx Virtex-6 device used in this thesis, there are only two slice types, called SLICEL and SLICEM. The first one, SLICEL, is the simplest one with four LUTs and eight flip-flops. Additionally, it has the ability for a carry signal to and from adjacent slices. SLICEM have the same functionality as a SLICEL but in addition the LUTs may be used as distributed RAM (256-bit) or as shift registers (128-bit). Each LUT in the Virtex-6 device is a six-input LUT which can be split into two five-input LUTs [5].

A numerous, sometimes thousands, CLBs are necessary to implement complex digital circuits and all these CLBs must be connected to each other. To accomplish this, there

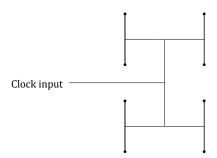

are programmable interconnecting switch boxes adjacent to the CLBs. The configuration of these switch boxes determines which CLBs are connected to each other. To accommodate the clocking of the flip-flops there are dedicated clock paths organized in such way that each end point of the path has the same delay as all the others. This can be accomplished by routing the clock paths in an H-tree or similar, which gives a uniform clock distribution. Figure 2.4 shows an example of a simple clock distribution network where each endpoint, represented by the dots, has equal path length.

Figure 2.4 - Uniform clock distribution.

An FPGA is divided in clock regions, each region with its own dedicated clock distribution network. In the Virtex-6 device used in this thesis there are in total of 12 clock regions. There are 32 global clock lines that can reach the entire FPGA, in all of the clock regions. In addition, each clock region has up to six regional clock trees [6].

While modern computers have a central processing unit (CPU) that operates at frequencies up to approximately 3.5 GHz, the operation frequency of an FPGA design varies widely depending on the implemented design and the FPGA device. But it is far lower than the CPU frequency. In a computer, all internal components of the CPU are placed at a fixed location and the placement is optimized to minimize the internal routing in order to achieve the lowest possible path delay, i.e. highest possible frequency. This differs from an FPGA; although all CLBs, flip-flops, I/Os, embedded components and the internal routing network are at fixed positions on the die, the routing path between modules may become long due to the interconnecting switch boxes that connect CLBs and other components to each other. The longest path in a design can therefore vary and hence the frequency varies accordingly.

In order to load an FPGA device with a design, the device need to be configured, i.e. all SRAM cells need to obtain their logic state, all flip-flops must be configured with their initial state, all BRAM used must be initialized with their intended data. This is done by uploading a *configuration file*, also known as the *bitstream*, to the FPGA. The next section gives a detailed description of FPGA configuration.

#### 2.3 Configuration

The configuration data is stored in CMOS configuration latches (CCLs) [7]. Since SRAMs and CCLs are volatile, i.e. its value are lost at power down, an FPGA must be configured each time the power is applied. It is therefore necessary to have a memory

device connected to the FPGA that holds the configuration file(s) so the FPGA can be configured at power up in the field. The configuration file, or bitstream, consists of several commands in addition to the configuration data. The commands control the configuration process. A detailed description of the relevant commands can be seen in section 2.6.4. The configuration file is produced by the integrated development environment (IDE) tool and has the file extension of .BIT or .BIN.

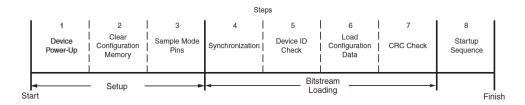

File size of the ML605 board Virtex-6 device configuration file is  $\sim$ 70 Mbit ( $\sim$ 8.8 MB) according to [7]. When a configuration is complete the configuration interface on the FPGA side asserts a DONE signal, see section 2.6.1, indicating the configuration has completed with success. The configuration process of a Xilinx Virtex-6 device undergoes a specific configuration sequence with two phases; setup and bitstream loading. Figure 2.5 shows the sequence and its steps. The setup phase consists of three steps. The first step is to check availability of voltage power required by the device. The second step is to clear the configuration memory. Final step of the setup phase is to sample the mode pins that determines the configuration interface, the configuration clock (CCLK) also starts at this step. See table 4.1 for mode pin settings.

Next phase is the bitstream loading which consists of four steps. First step is synchronization. A 32-bit synchronization word in the bitstream is detected and tells the configuration logic that a configuration is about to commence. Before the synchronization word there is a bus width detection pattern that tells the configuration logic the bus width of the configuration data. Any data in the configuration file before the bus width pattern is ignored. The synchronization word is  $0\times AA995566$ . Next step is to do a check of device ID to prevent configuration with a bitstream that is formatted for another device. After the device ID check configuration commands and data are uploaded to the device. Final step of the bitstream loading phase is a cyclic redundancy check (CRC). As the configuration data is uploaded the device calculates a CRC value. At the end of the bitstream a CRC command is issued followed by a CRC expected value. If the calculated value does not match the expected value the configuration is aborted. After the bitstream loading phase the bitstream instructs the device to perform the startup sequence, which is described in [8].

Figure 2.5 - Configuration sequence

#### 2.4 Partial Reconfiguration

FPGAs are flexible in the sense they can be *reconfigured*, i.e. uploading another configuration file, on-site. To perform the reconfiguration the FPGA has to shut down in order to load a new configuration file. The whole FPGA is then reconfigured. *Partial reconfiguration* (PR) is the ability to reconfigure only parts of the. *Passive* PR means

all clocks, and hence the whole system, are suspended during reconfiguration. *Active* PR means the rest of the system is running while reconfiguration takes place. The latter is also known as 'run-time reconfiguration', 'dynamic partial reconfiguration' or as 'hardware multitasking'. In order to perform a partial reconfiguration it is necessary to partition the FPGA fabric into a static region and a partial region. The partial region can be reconfigured while the design in the static region is running. The partial region may take any size of the fabric. Partial reconfiguration enables three dimensional hardware space where different designs share the same area over time. Some benefits of partial reconfiguration are listed below.

- Implementation of a bigger system onto a smaller FPGA device if the system can be divided into smaller independent designs.

- Improved fault tolerance with the ability to reconfigure the damaged module

- Mutual exclusive designs may use the same device

- Faster startup time as only the static region needs to start first. The PR region with its modules may start at a later time

- Custom CPU instruction for a soft core microprocessor may be implemented when necessary [9]

A challenge with partial reconfiguration is that it takes a considerable amount of time to perform a reconfiguration. The bigger the partial region that is to be reconfigured the longer time it takes to reconfigure.

#### 2.4.1 Static region

The static region may contain modules that are needed throughout the entire cycle of operation of the system such as a soft core microprocessor, a reconfiguration controller or others. These modules will never be interrupted or stopped due to partial reconfigurations.

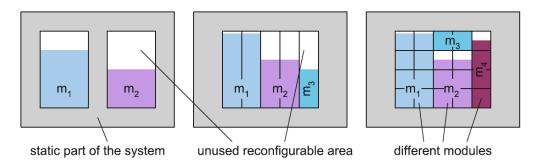

#### 2.4.2 Partial region

There are three different *styles* of PRR. These styles have various complexities and the simplest one is a *single island style*. This style is just one island on the fabric surrounded by the static region as seen in figure 2.6. The size of the island may vary but cannot be lower than the height of one clock region, or a frame. With island style, internal fragmentation may become an issue. Internal fragmentation is the PRR's resources not used if the module has a smaller footprint than the size of the island itself. Only one PRM can be situated in an island at any given time. Multiple islands may be implemented on the same FPGA.

Figure 2.6 - Different styles of partial reconfigurable regions  $\left[10\right]$

Slot style partial region may resemble the island style, but it is narrower as a slot may refer to a column or a frame. These slots may have greater height than the height of a frame, just as the island style. They may even span the whole height of the FPGA. The issue of fragmentation becomes less with a slot style region as a multiple slots may host one PRM and the utilization of slots then becomes higher compared to an island style region. On the other hand, slot style region may suffer from external fragmentation due to the fact that a narrow slot may not include all logic resources, i.e. BRAM, DSP or others. Depending on a modules requirements a slot may therefore become completely unused.

Grid style is the most complex style but gives the most flexibility. Each grid block is in its own a partial reconfiguration area. A partial module may have a foot print of several grid blocks but two modules cannot share the same block. So internal fragmentation still exists but is even less than in the slot style.

#### 2.5 Context switching

One problem with partial reconfiguration is that whenever a module is reintroduced into the partial region it starts off from the beginning, i.e. the module's progress is not recorded so that it can be resumed from where it was when it was replaced. Context switching addresses this problem. As mentioned in the introduction, context switching is the capability to preserve a modules internal state for later resumption at that point in time where the module was replaced.

#### 2.5.1 Context switching in software

A computer, with one CPU core, can apparently perform several tasks simultaneously, i.e. applications run in parallel. This is however not the case. The computer switches between processes at a timely fashion. To accomplish this, the CPU, in cooperation with the operating system, has to perform a context switch each time it switches process. Context switch means to save a process' state into memory, from here on out called context save (CS), and then restore those states when the process resumes, from here on out called context restore (CR). This enables multiple processes to share a single CPU. A context is defined to be the contents of a CPUs registers and program counter at any point of time [11]. For the CPU to know when to save the running process' state and which process to switch to there are different triggers. The running process can make itself trigger a switch, e.g. by timeout or by waiting for another process' flag, an interrupt may also trigger a switch,

#### 2.5.2 Hardware context switching

Context switch in a hardware design is not that different from a software context switch. But what constitutes a modules context? In essence the only context available must be that information that is due to sequential logic, i.e. registers, and local RAM inside the module. Combinatorial logic cannot be preserved. Combinatorial circuits are realized with LUTs, multiplexers and latches. Information from these elements is not available unless they are registered through a flip-flop. It is therefore imperative that the design of a partial reconfiguration module includes registers wherever information needs to be passed on to the next run. The designer must also avoid inferring latches as output of a latch is not clocked. Before any CS can begin all clocks of that particular partial reconfiguration module must be halted to avoid saving of

invalid data. If the module uses more than one clock the module must be halted in between the cycles of the slowest clock. [12] lists other requirements. There are two ways to extract information from a module, by *hardware checkpoints* and by *configuration readback with register capture*. The latter is discussed in section 2.6.5 and hardware checkpointing is discussed in next section.

#### 2.5.2.1 Hardware checkpointing

Hardware checkpointing is a way to store a modules state during normal operation, in other words an image capture of the module at run-time. There are different methods to accomplish checkpointing, three which are described in [13], were a definition is given as: "A checkpoint is a set of data items representing the image of the last error-free state of a module of computation from which in case of the occurrence of a fault may be restored." These data items are output (0), input (1), state (S), state transition function  $(S_f)$ , output function  $(O_f)$  and initial state  $(S_0)$ , half of which is necessary for checkpointing; (0), (0), (0), and (0), a

#### 1) Memory mapped state access

Memory mapped state access utilizes a memory space in a CPU to store a modules states. The present value is fed back to the module while executing a checkpoint. This is achieved by integrating a checkpoint flip-flop into a read/write memory of the CPU.

#### 2) Scan chain based state access

This technique is based on a long chain of flip-flops connected together as a shift register. A multiplexer in front of each flip-flop switches between normal operation and shift register. Chain ends are connected together to from a ring shift register.

#### 3) Shadow scan chain based state access

Duplicating all the flip-flops is another way to take a snapshot of the module. That is what shadow scan chain does. These duplicates are used for the checkpointing only and, as in scan chain, they are arranged in a ring. The overhead for this technique is tremendous as one flip-flop in the module demands another flip-flop for checkpointing. The advantage is that it only takes one clock cycle to perform the checkpointing.

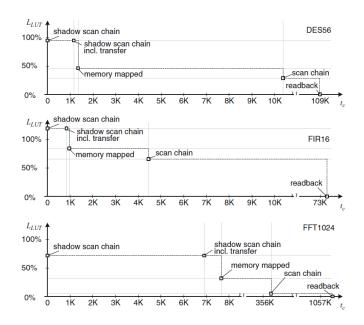

Hardware checkpointing demands added hardware to the PRMs and hence adds logic overhead. Figure 2.7 illustrates the difference in both logic overhead and time overhead between the three hardware checkpointing techniques and compares them to configuration readback.  $L_{LUT}$  denotes extra LUTs in the PRM required for implementing the respective technique, and  $t_{\rm c}$  denotes time overhead in terms of clock cycles. It is seen that for the extremes the shadow scan chain provides close to none overhead in time and close to 100% logic overhead. Readback is completely opposite, almost none logic overhead and a huge overhead in time. In between there are scan chain and memory map.

Figure 2.7 - Time and logic overhead for the different hardware checkpointing techniques [10]

#### 2.5.2.2 Bitstream manipulation

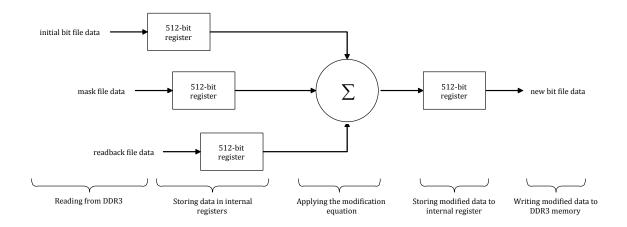

Bitstream manipulation is the key point when state extraction, or context save, is performed by configuration readback and register capture. In order to restore a PRM with its context from a previous run, the partial reconfigurable region, where the module is placed, must be uploaded with an updated partial bitstream. Generation of this new and updated partial configuration file is accomplished by masking the necessary bits in both the readback file and the initial partial configuration file. That means three files are used to create a new partial configuration file; the initial bit file, the mask file and the readback capture file. The initial bit file contains the module with its initial states, the readback capture file contains register data at point of capture and the mask file contains information of which bits in these two files are configuration data. According to [14] the creation of the new partial configuration file is done by the modification algorithm in equation 2.1. Next section gives details of the mask file.

New partial config. file = (readback file \* mask file) + (initial bit file \* (NOT mask file)) 2.1

#### 2.6 Xilinx Virtex-6 FPGA configuration

#### 2.6.1 Configuration interfaces

The configuration file can be uploaded to the FPGA through four different interfaces. Either by a serial peripheral interface (SPI), bus-width parallel interface (BPI), SelectMAP interface or by JTAG interface. For *reconfiguration* purposes the Internal Configuration Access Port (ICAP) is used, or if the reconfiguration is controlled by an external device the SelectMAP interface is used. A brief description of these interfaces will be given below. In newer FPGAs with integrated embedded microprocessors,

such as the Zynq all programmable system on chip (SoC) from Xilinx, there is also a fifth configuration port, the processor configuration access port (PCAP). This port will not be covered here but see [15] for more information. All interfaces share the same dedicated configuration pins, some of them are shown in table 2.1. All details of the pins are described in [7].

Table 2.1 - Configuration pins

| Pin name   | I/0            | Description                                 |

|------------|----------------|---------------------------------------------|

| MODE [2:0] | Innut          | Determines configuration mode. Sampled      |

|            | Input          | on the rising edge of INIT_B                |

| CCLK       | Output         | Configuration clock source for all          |

|            |                | configuration modes except JTAG             |

| DONE       | Bi-directional | Active high signal indicating configuration |

|            |                | is complete.                                |

|            |                | 0 = FPGA not configured                     |

|            |                | 1 = FPGA configured                         |

| PROGRAM_B  | Input          | Active-low full-chip reset                  |

| D [15:0]   | Bi-directional | BPI input / SelectMap input / output.       |

#### 2.6.1.1 Serial Peripheral Interface (SPI)

This interface is used when the configuration file resides in a serial flash memory. The FPGA device provides clock for the flash, and default memory address always starts from zero. The flash can be programmed through the Xilinx tool iMPACT.

#### 2.6.1.2 Bus-width Peripheral Interface (BPI)

This interface is used when the configuration file resides in a parallel flash memory. Bus widths of 8 or 16 are supported. The bus width is auto detected via the bitstream. BPI-Up mode sets the starting address to zero and increments it by 1 until DONE signal is asserted. BPI-Down mode set the starting address to memory end address and decrements it by 1 until DONE signal is asserted. The flash can be programmed through the Xilinx tool iMPACT.

#### 2.6.1.3 **SelectMAP**

This interface provides data bus widths of 8, 16 or 32 bits. The data bus is also bidirectional and is therefore used for bitstream readback. As with the BPI interface the bus width is auto detected. The interface is synchronous.

#### 2.6.1.4 JTAG

Xilinx Virtex-6 devices supports IEEE 1149.1 standard of Test Access Port and Boundary-Scan architecture which are commonly referred to as JTAG. Configuring an FPGA by this method is quite slow as the frequency of the JTAG interface is often low and the fact that it is a serial interface. Its upside is that it can be used by debugging software like ChipScope Pro to get access to internal test signals, defined by the user, within the FPGA to provide a debugging platform.

#### 2.6.1.5 ICAP

ICAP is the internal configuration port used for readback and reconfiguration. It is similar to the SelectMAP port but has no physical ports connected to the outside world. It acts solely internal and is therefore the configuration port of choice regarding partial reconfiguration. The ICAP interface is a Xilinx primitive, meaning that it can be instantiated in the VHDL or Verilog code. The ICAP supports 16 and 32-

bits data bus. According to Xilinx documentation, the ICAP clock can only run at frequency of 100 MHz which corresponds to a data rate of 3200Mb/s (400 MB/s). The low clock frequency is the main reason for slow reconfiguration.

#### 2.6.1.5.1 Enhanced ICAP

There have been some attempts at overclocking the ICAP clock with great success. In [16] the authors managed to overclock the ICAP clock up to 500-550 MHz giving a data rate between 2000-2200 MB/s. This is five times faster than original speed and it significantly reduces the configuration speed. However, the measured data rate is accomplished writing the configuration only. When performing readback the authors didn't overclock the ICAP clock in order to prevent corruption of the readback data. The authors used Virtex-4 and Virtex-5 in their experiments and not a Virtex-6 device. So the overclocking has not, to my knowledge, been confirmed to be working on Virtex-6, but it is reasonable to assume that it will since there is no difference between the ICAP primitive from Virtex-4 and Virtex-6.

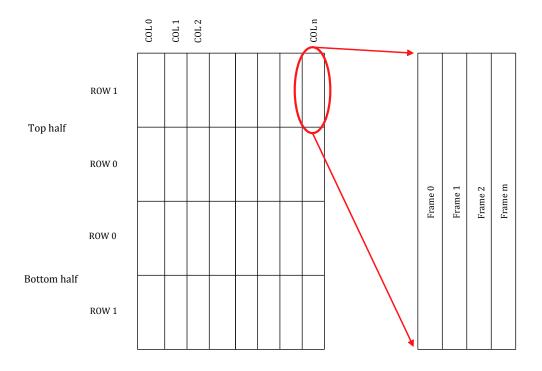

#### 2.6.2 Configuration frames and frame addressing

The configuration data is organized in frames, the smallest addressable configuration segments. The FPGA logic space is arranged in rows and columns, and in addition it is divided into top half and bottom half [8]. A row has the height of one column, which corresponds to the height of one clock region. Top and bottom half each contains several rows, vertically aligned, each row contains several columns, horizontally aligned, and each column contains several frames, also horizontally aligned, as seen in figure 2.8 below.

Figure 2.8 - Virtex-6 configuration architecture.

In the center of a row lies a horizontal clock row (HROW). A configuration frame spans the height of 40 CLBs, 20 above HROW and 20 below. Each frame has a unique 24-bit address that can be divided into five sections as seen in table 2.2 below. The 24-bit address is sent as a 32-bit word and hence the eight MSBs are unused. All frames have identical length of eighty one 32-bits words, or 2592 bits. The XC6VLX240T-1 device has a total of 28488 configuration frames and additional 583 32-bit words used for configuration commands [7]. A write to the frame address register (FAR), a section is dedicated to configuration registers, determines which frames to read from or write data to.

Table 2.2 - Frame address format

| Address type   | Bit index | Description                                             |

|----------------|-----------|---------------------------------------------------------|

| Block          | [23:21]   | Valid block types are CLB, I/O, CLK (000), block RAM    |

|                |           | content (001), and CFG_CLB (010). A normal              |

|                |           | bitstream does not include type 010.                    |

| Top / Bottom   | [20]      | Select between top-half rows (0) and bottom-half        |

|                |           | rows (1).                                               |

| Row Address    | [19:15]   | Selects the current row. The row addresses              |

|                |           | increments from center to top, and then resets and      |

|                |           | increments from center to bottom.                       |

| Column Address | [14:7]    | Selects a major column, such as a column of CLBs.       |

|                |           | Column addresses start at 0 on the left and increase to |

|                |           | the right.                                              |

| Minor Address  | [6:0]     | Selects a frame within a major column.                  |

#### 2.6.3 Configuration packets

All data, either configuration data or configuration commands, are sent to the configuration control logic by means of *data packets*. There are two types of packets, type 1 packets are used to read or write the configuration registers, and type 2 packets are used to write long blocks of data [7]. Type 2 packets must always be preceded by a type 1 packet. Table 2.3 below shows the format of type 1 packets and table 2.4 shows the format of type 2 packets, where x denotes a bit, and R denotes a reserved bit, this applies for both tables on configuration packets. Table 2.5 shows which operation codes are available.

Table 2.3 - Configuration packet, type 1.

| Packet type | op. code | conf. reg. address | reserved | word count |

|-------------|----------|--------------------|----------|------------|

| [31:29]     | [28:27]  | [26:13]            | [12:11]  | [10:0]     |

| 001         | XX       | RRRRRRRR           | RR       | xxxxxxxxx  |

Table 2.4 - Configuration packet, type 2.

| Packet type | op. code | word count                |

|-------------|----------|---------------------------|

| [31:29]     | [28:27]  | [26:0]                    |

| 010         | XX       | xxxxxxxxxxxxxxxxxxxxxxxxx |

Table 2.5 - Configuration register operations.

| op. code | function             |

|----------|----------------------|

| 00       | no operation (NO-OP) |

| 01       | read                 |

| 10       | write                |

| 11       | reserved             |

#### 2.6.4 Configuration registers

A configuration command is either a read from the configuration register or a write to the registers. Table 2.6 below shows which registers are essential for reconfiguration purposes of a Virtex-6 device. All configuration registers are described in detail in [7].

Table 2.6 - Configuration registers essential for reconfiguration.

| Name | R/W   | address | Description                                     |

|------|-------|---------|-------------------------------------------------|

| FAR  | r/w   | 00001   | Frame Address Register                          |

| FDRI | write | 00010   | Frame Data Reg. Input, write configuration data |

| FDRO | read  | 00011   | Frame Data Reg. Output, read configuration data |

| CMD  | r/w   | 00100   | Command Register                                |

The FAR register is explained in the section on configuration frames above. A write to the FDRI register tells the configuration logic that configuration data are about to be sent to the frame address specified in the FAR register The FDRO register provides readback data when readback has been set up. The read starts from the frame address specified in the FAR register and then auto increments until number of words specified in the word count is reached.

The CMD register instructs the configuration logic to perform configuration functions. The instruction present at the CMD register is executed each time the FAR register is loaded with a new value. Table 2.7 shows which instructions are essential for reconfiguration and readback.

Table 2.7 - Essential instructions in the CMD register related to reconfiguration.

| Command  | Code  | Description                                        |

|----------|-------|----------------------------------------------------|

| WCFG     | 00001 | Writes Configuration Data: used prior to writing   |

|          |       | configuration data to the FDRI.                    |

| RCFG     | 00100 | Reads Configuration Data: used prior to reading    |

|          |       | configuration data from the FDRO.                  |

| START    | 00101 | Begins the Startup Sequence: initiates the startup |

|          |       | sequence. The startup sequence begins after a      |

|          |       | successful CRC check and a DESYNC command are      |

|          |       | performed.                                         |

| GCAPTURE | 01100 | Pulses GCAPTURE: Loads the capture cells with the  |

|          |       | current register states.                           |

An example of commands is given in table 2.8. This example is an excerpt taken from an actual configuration file for the ML605 Virtex-6 device. The example shows how to decode the configuration data present in the configuration file. The data is broken down do match the format of the specific packet type and then decoded. Marked data in the figure 2.9 shows the configuration commands and data used in the example.

| Offset(d) | 00       | 04       | 08       | 12       | 16       | 20       | 24       | 28       |

|-----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 00000000  | FFFFFFFF | FFFFFFF  | 000000BB | 11220044 | FFFFFFFF | FFFFFFF  | AA995566 | 20000000 |

| 00000032  | 30020001 | 00000000 | 30008001 | 00000000 | 20000000 | 30008001 | 00000007 | 20000000 |

| 00000064  | 20000000 | 30022001 | 00000000 | 30026001 | 00000000 | 30012001 | 02003FE5 | 3001C001 |

| 00000096  | 00000000 | 30018001 | 04250093 | 30008001 | 00000009 | 20000000 | 3000C001 | 00000001 |

| 00000128  | 3000A001 | 00000101 | 3000C001 | 00000000 | 30030001 | 00000000 | 20000000 | 20000000 |

| 00000160  | 20000000 | 20000000 | 20000000 | 20000000 | 20000000 | 20000000 | 30002001 | 00000000 |

| 00000192  | 30008001 | 00000001 | 20000000 | 30004000 | 502335C8 | 00000000 | 00000000 | 00000000 |

| 00000224  | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |

| 00000256  | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |

| 00000288  | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |

| 00000320  | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 | 00000000 |

Figure 2.9 - Data from an actual configuration file for a Virtex-6 device.

Note that the format of the command is decided by the packet type. The word count gives how many configuration packets are connected to the configuration command. When the word count in a type 1 packet is set to zero a packet of type 2 is following as seen in the example above. A packet of type 2 must always be preceded by a packet of type 1. The 32-bit word  $0 \times 20000000$  in the example corresponds to a type 1 packet with operation code 00 which means that is an NO-OP command and the configuration control logic does not execute a command for one clock cycle. The last command tells the configuration control logic that the next 2370528 words are configuration data. This corresponds to 28488 configuration frames and hence configuration for the whole device.

Table 2.8 – Example of decoding the configuration file.

| Data in hex:                                                                         | 30008001    | 30008001                                    |                |    |             |  |  |

|--------------------------------------------------------------------------------------|-------------|---------------------------------------------|----------------|----|-------------|--|--|

| Data in binary:                                                                      | 00110000000 | 001100000000001000000000000000000000000     |                |    |             |  |  |

| Format:                                                                              | Packet type | Packet type op.code address res. word count |                |    |             |  |  |

| Data broken up accordingly to fit the format given by three first bit (packet type): | 001         | 10                                          | 00000000000100 | 00 | 00000000001 |  |  |

| Decoded command:                                                                     | Type 1      | write                                       | CMD register   | -  | 1 word      |  |  |

Then follows 32-bits of data connected to the command above

| Data in hex:            | 00000001                                |                          |  |

|-------------------------|-----------------------------------------|--------------------------|--|

| Data in binary:         | 000000000000000000000000000000000000000 |                          |  |

| Instruction in CMD reg: | WCFG                                    | Write configuration data |  |

Next command in the configuration file follows

| Data in hex:                                                                         | 20000000     |                                             |                |    |             |  |  |

|--------------------------------------------------------------------------------------|--------------|---------------------------------------------|----------------|----|-------------|--|--|

| Data in binary:                                                                      | 001000000000 | 001000000000000000000000000000000000000     |                |    |             |  |  |

| Format:                                                                              | Packet type  | Packet type op.code address res. word count |                |    |             |  |  |

| Data broken up accordingly to fit the format given by three first bit (packet type): | 001          | 00                                          | 00000000000000 | 00 | 00000000000 |  |  |

| Decoded command:                                                                     | Type 1       | no-op                                       | (CRC register) | -  | -           |  |  |

The above command is a NO-OP operation, and next command follows

| Data in hex:                                                                         | 30004000     |                                             |                |    |             |  |

|--------------------------------------------------------------------------------------|--------------|---------------------------------------------|----------------|----|-------------|--|

| Data in binary:                                                                      | 001100000000 | 0011000000000010000000000000000000          |                |    |             |  |

| Format:                                                                              | Packet type  | Packet type op.code address res. word count |                |    |             |  |

| Data broken up accordingly to fit the format given by three first bit (packet type): | 001          | 10                                          | 00000000000010 | 00 | 00000000000 |  |

| Decoded command:                                                                     | Type 1       | write                                       | FDRI register  | -  | -           |  |

Then follows 32-bits of data connected to the command above

| Data in hex:                                                                         | 502335C8                                  |                                 |                             |  |  |  |

|--------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------|-----------------------------|--|--|--|

| Data in binary:                                                                      | 010100000010                              | 010100000100011001101111001000  |                             |  |  |  |

| Format:                                                                              | Packet type                               | Packet type op. code word count |                             |  |  |  |

| Data broken up accordingly to fit the format given by three first bit (packet type): | 010                                       | 10                              | 000001000110011010111001000 |  |  |  |

| Decoded command:                                                                     | Type 2 write 2307528 words (28488 frames) |                                 |                             |  |  |  |

#### 2.6.5 Configuration readback and register capture

As mentioned earlier, it is possible to perform a so-called readback of configuration data. This means that the configuration memory can be read and outputted. Readback may be used to perform a verification of configuration, to correct a single event upset (SEU), for debugging purposes, or, as in this case, to perform partial reconfiguration with context switching. The readback function is performed at users' request. The initiator must send a sequence of configuration commands to the configuration control logic in order to perform a readback. The command sequence can be found in [7]. The user may use external devices as a microprocessor, another FPGA system or

the FPGA itself to send the command sequence. The commands have the same encoding as seen in the example in the previous section. When a readback is initiated the first frame of data is a *pad-frame*, which contains no data of interest, and must be discarded, see section on mask file below.

The value present at each flip-flop in a LUT can be captured and read back from the device. An instruction, GCAPTURE, in the CMD register initiates the capture and the flip-flop value is transferred to the configuration memory. The value resides in the memory location normally used for programming that specific flip-flop. The command sequence for readback capture requires an additional step compared to a normal readback, and that is to set the GCAPTURE instruction. There is another method to transferring the flip-flop value to the configuration memory; instantiate the CAPTURE\_VIRTEX6 primitive and assert the CAP input; the flip-flop value is then sampled and stored in the configuration memory at the next rising edge of the primitives clock [7]. The primitive has two operations: one-shot or continuous. One-shot captures the flip-flop values once.

#### 2.6.6 Xilinx ISE configuration options

There are options in the Xilinx tool ISE that need to be set in order to enable the reconfiguration capability. In process properties for the 'Generate Programming File' process there is a category named 'Readback Options'. Here is the security option of enabling or disabling readback and reconfiguration. It must be set to 'Enable Readback and Reconfiguration'. In addition, there are two other options available that is necessary to accomplish reconfiguration by means of the proposed system in this thesis: 'Create ReadBack Data Files' and 'Create Mask File'.

#### 2.6.6.1 Mask file

In order to extract register information from the readback data, we need to know where in that data the information is located. The mask file generated by the ISE tool masks which bit in the readback data that are actual configuration data and not configuration commands or other data. Mask file has the file extension .MSK. This file is used to create a new partial configuration file, in compliance with equation 2.1, for the PRM that have been replaced. The content of the mask file does not match the readback data as seen in figure 2.10. It is therefore necessary to discard unwanted data from the readback data.

Figure 2.10 – Misalignment of file contents [7].

## 3 Related research

#### 3.1 Chapter overview

As mentioned in the introduction there has been extensive research on the subject of partial reconfiguration, but not as much on the issue of context switching. The most relevant work, to my knowledge, compared to this thesis is presented here. They are listed in order of increasing relevance.

#### 3.2 Research papers

"Multitasking on FPGA coprocessors" [12]. The paper discusses requirements for context switching, or multitasking as the authors describe it. The paper focuses on context switching by means of bit stream read back and is therefore highly relevant. The requirements are listed in table 3.1 below.

Table 3.1 - Context switching requirements.

- 1 The FPGA must provide a readback bit stream that contains the *current* state of all registers and internal memory.

- 2 Each register and memory bits in the FPGA must be able to preset or reset when a module is restored.

- 3 Configuration and readback must be sufficiently fast to keep switching time as low as possible.

- 4 Freezing the modules clock is necessary in order to take a capture of the registers and memory elements.

- 5 If the module uses more than one clock the module must be interrupted only between cycles of the slowest clock.

- 6 To avoid invalid data the clock must be stopped when it is safe, i.e. not when there is a memory addressing phase.

- 7 The modules that are switched cannot contain latches or registers by means of combinatorial logic loops as states of these types cannot be accessed.

- 8 If an external data source, or destination, is connected to the switching module the communication between the module and the external source/destination must be halted until the module is restored.

They also propose a client-server model of a hardware management unit (HMU) where the HMU is the server and the partial reconfiguration regions are the clients. The HMU is necessary to control the context switching. The setup included in this paper requires an external CPU that handles the reconfiguration process (the CPU act as HMU). No results were presented.

"Efficient hardware checkpointing: concepts, overhead analysis and implementation", [13]. This paper presents a tool, STATEACCESS, which utilizes hardware checkpointing to recover a module's state in case of an operational fault. Hardware checkpointing adds some hardware to an existing module in form of a checkpointing finite state machine (CFSM). The main purpose of hardware checkpointing is to regularly take 'snapshots' of the internal states of a module in a fault-free operation in order to restore the module when a fault occurs. The paper also considers three different methods to perform hardware checkpointing which are; i) Memory-Mapped state access (MM), ii) Scan Chain based state access (SC) and iii) Shadow Scan Chain based state access (SHC). These methods provide four types of overheads defined by the authors: hardware overhead H (in terms of extra flip-flops and LUTs), performance reduction R (reduction of maximal clock frequency), time-overhead C (increase in execution time) and latency L (time for a complete checkpoint arrives at the rollback device). MM integrated the checkpointing flip-flops into a memory space of a CPU. With SC the flip-flops are chained together through a long shift-register chain where each flip-flop has a multiplexer associated that switches between normal operation and shift-register operation. The last method, SHC is actually a state copy. For every state-register in a module there exists another register that copies the state. This creates a massive hardware overhead. The authors tested hardware checkpointing on three different modules, (a) DES56 cryptographic IP core, (b) 16 tab FIR filter and (c) FFT/IFFT coprocessor. The paper reported following hardware overhead. 2%-11% increase in flip-flops and 32%-83% increase in LUTs for MM, 4%-12% increase in flip-flops and 5%-66% increase in LUTs for SC, and finally 103%-122% increase in flip-flops and 72%-121% increase in LUTs for SHC. Hardware checkpointing is implemented in design flow and does not consider context save and restore through bitstream readback.

"Context saving and restoring for multitasking in reconfigurable systems", [17]. This paper proposes a combined software and hardware solution to context switching. It utilizes the bitstream readback functionality and extracts register information from the bitstream (State Extraction Filter). This information is then used to produce a new partial configuration file that contains the information of the registers and memory elements (State Inclusion Filter). Another benefit of this system is that it contains a database of which configuration frames that holds the value of a register or a memory bit. That means that it isn't required to perform a read back of all the configuration frames within the partial region but only the frames that contains the register and memory elements. This significantly reduces the overall context switching time in comparison to reading all the frames. The main focus of the paper is to develop a system that relocates the saved module to another part of the device. The implemented system includes a previously made relocation filter, REPLICA, from the same authors. They implemented the system on an XCV2000E (Virtex-E) and their test result shows a total relocation time (including state extraction and state

inclusion, also known as context save and context restore) between 0.4 ms and 14.8 ms with a partial bit stream size ranging from 9.3 kB to 331.7 kB.

"A novel mechanism for effective hardware task preemption in dynamically reconfigurable system" [18]. This paper presents a tool, BitFormatter, that analysez the configuration file for each PRM. The tool then generates a DPRS Bitstream Format (DBF) file that contains a State Data Descriptor Table (SDDT). The table contains information about which frames the PRM's state information is situated in, and that frame's FAR value. When readback capture is initiated only those frames listed in the SDDT are captured. These frames are then written into their corresponding location in the initial configuration file. Restoring the same PRM is done by loading the FPGA with the modified bitstream. The authors used a Virtex-4 device in their experiments and an embedded CPU to control the reconfiguration process. Since only a few frames are read, compared to the total number of frames in the PRR, the readback process is fairly fast. Their test results shows a readback time of only 60.11 μs for a readback file of 3.68 kB, and a reconfiguration time of 536.9 μs for a modified configuration file of 158.83 kB. Modification time was not directly measured, but a comment on the issue was given; 'slightly more than 1 ms (...)'

"Hardware context-switch methodology for dynamically partially reconfigurable systems" [19]. The paper presents a hardware system that performs context switching. This system is similar to [17] except that instead of a CPU all work is done by means of hardware and without the relocation filter. The database in this system contains information about frame address and bit index. This information is derived from the logic allocation file generated by BitGen. The register information is extracted from the file, and with the frame address information, this constitutes the database contents. Whereas [17] used a CPU to perform the read operations, the system proposed in this paper use a command ROM to store the configuration commands needed. In experiments the authors used XC2V1000 and XC2VP20 devices. The presented results in this paper are not directly comparable.

"On-chip context save and restore of hardware tasks on partially reconfigurable FPGAs" [14]. This paper proposes an autonomous software based on-chip context save and restore (CSR). They used a MicroBlaze soft core embedded processor with a Linux-like operating system based on BusyBox. The process of context switching consist of three main steps. First is to save the context (CS), which means to initiate capture of flip-flops. Next, the captured data is merged with the initial bitstream to make a new partial bitstream; this process involves bitstream manipulation with mask file, captured file and the initial bit file. The last step is context restore (CR) which is to send the new merged bit file to the PRR. In compliance with requirements presented by [12], the PRR clock is halted during the entire CSR. Their experiment was performed on a Virtex-5 device and they tested the system on PRRs that ranged from one to twelve columns. They only measured how long the intermittent processes lasted. There are four different time measurements.  $T_{CS}$ ,  $T_{merge}$  and  $T_{CR}$ where 'CS' is the context save process, 'merge' is the process of creating new partial configuration file, and the 'CR' is the context restore process. For a PRR of twelve columns and a PRM flip-flop count of 1920 the reported times where:  $T_{CS} = 13.06$  ms,  $T_{merge} = 19.39 \text{ ms}$  and  $T_{CR} = 13.23 \text{ ms}$ .

## 3.3 Summary

Table 3.2 below gives a summary of the research papers above. The table shows which device was used, which techniques was used for extracting the states, and if the reconfiguration controller were implemented in software (CPU) or in hardware.

Table 3.2 - Summary of essential parameters.

| Author | Device    | State Extr. Tech. <sup>1</sup> | HW/CPU <sup>2</sup> |

|--------|-----------|--------------------------------|---------------------|

| [13]   | Virtex-II | Hardware checkpoints           | -                   |

| [17]   | Virtex-E  | Bitstream manipulation         | Both <sup>3</sup>   |

| [18]   | Virtex-4  | Bitstream manipulation         | CPU                 |

| [19]   | Virtex-II | Bitstream manipulation         | HW                  |

| [14]   | Virtex-5  | Bitstream manipulation         | CPU                 |

<sup>&</sup>lt;sup>1</sup> State extraction technique used.

<sup>&</sup>lt;sup>2</sup> Reconfiguration controlled by hardware or by CPU?

<sup>&</sup>lt;sup>3</sup> A combination of embedded CPU and hardware modules are used.

# 4 Implementation

## 4.1 Chapter overview

This chapter first explains the concept of the system that has been designed for this master thesis. Then follows an overview of the system, in section 4.3, where a functional explanation is given. The chapter continues to give a short description of the hardware platform used in the project. In section 4.5 the implemented system is described, the section gives an overview on the data flow, and an operational description is given. In the final section a detailed description on the implemented modules is given. Simulation captures and excerpt of the code is given when it is necessary to highlight a problem or to illustrate how they were solved.

## 4.2 System Concept

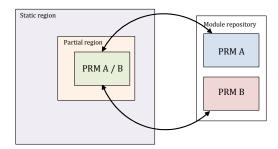

As described in the introduction, the foundation of the system in this thesis is based on two PRMs sharing the same PRR over time. Figure 4.1 below shows the system concept.

Figure 4.1 - Concept of partial reconfiguration with context switching

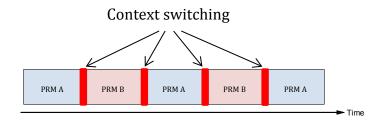

PRM A runs for a predetermined amount of time, and it is then switched with the PRM B. After the same amount of time the PRM A is reintroduced in to the PRR. Now it starts from where it was when it was replaced. Switching of PRMs continues as long as the FPGA is powered. As the figure 4.2 below shows, the PRMs are time multiplexed in the PRR. In-between execution time of PRMs, the system performs context save (CS) and context restore (CR).

Figure 4.2 - Time multiplexed hardware sharing

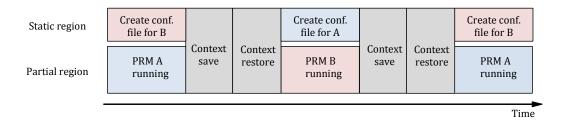

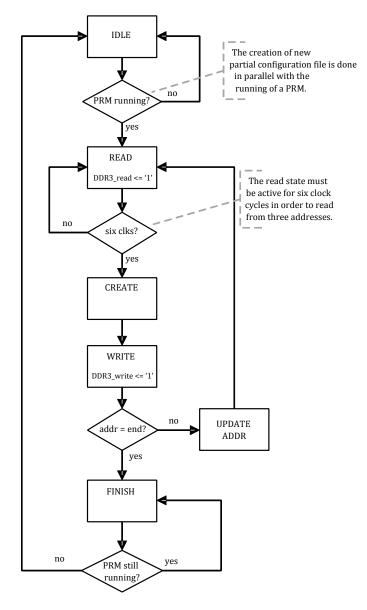

The creation of new partial configuration file is performed concurrently as the other PRM is executing, illustrated in figure 4.3. The CS and CR process occupies both the static region and the partial region. In the static region it writes and reads the readback and partial bitstream data to and from the memory. The partial region is halted when both CS and CR is in progress.

Figure 4.3 - Details of the context switching in Figure 4.2

## 4.3 System overview

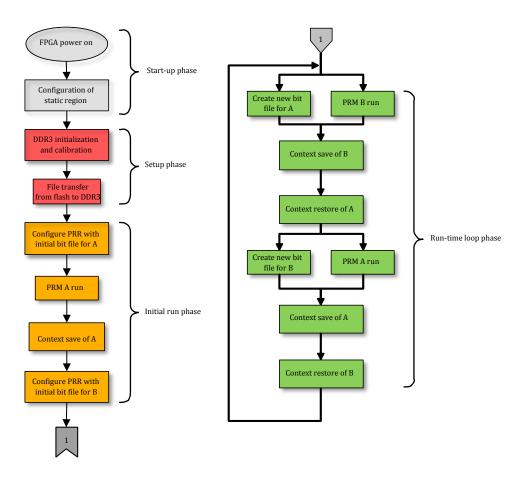

The system for switching between PRM A and PRM B can be described as four phases of operation, visualized in figure 4.4 on the next page.

Figure 4.4 – The four phases of operations of the system.

The start-up phase, marked as grey in the figure, consists of two stages:

- 1) Powering up the FPGA

- 2) Configuration of the static region

This phase is normal for any partitioned design. The partial region is not configured.

Next phase is the set-up phase, marked as red in the figure, and consists of two stages:

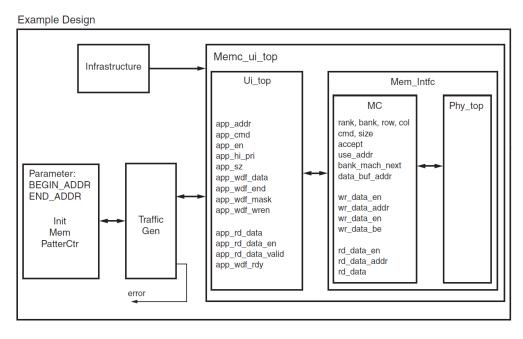

- 1) Initialization and calibration of the DDR3 memory

- 2) Transferring of files from the flash to the DDR3

Stage 1 is normal for the onboard DDR3 memory at every start-up, see [20] for more details. Duration of the initialization and calibration sequence is about 220  $\mu s$ . Since the generation of a new partial configuration file is depended on the mask file and the initial partial configuration file, these files must be uploaded from a computer to the onboard flash memory, via the Xilinx tool iMPACT. The flash memory is not suitable for context switching for reasons given in the next section. The files must therefore be transferred to the DDR3 memory. Immediately after completion of stage 1 the transferring of files starts. This stage continues until all the files are transferred.

The initial run phase, marked as orange, consists of four stages: