# SIGNAL PROCESSING USING CMOS-MEMS INTEGRATED RESONATORS

Ph.D. Thesis

Jan Erik Ramstad

March 20, 2012

#### © Jan Erik Ramstad, 2012

Series of dissertations submitted to the Faculty of Mathematics and Natural Sciences, University of Oslo No. 1178

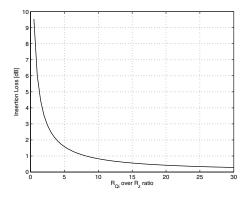

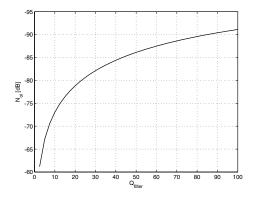

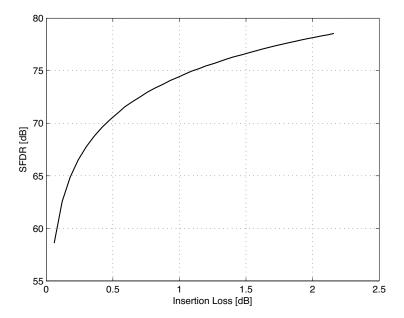

ISSN 1501-7710

All rights reserved. No part of this publication may be reproduced or transmitted, in any form or by any means, without permission.

Cover: Inger Sandved Anfinsen. Printed in Norway: AIT Oslo AS.

Produced in co-operation with Unipub.

The thesis is produced by Unipub merely in connection with the thesis defence. Kindly direct all inquiries regarding the thesis to the copyright holder or the unit which grants the doctorate.

### ABSTRACT

A central part of the ubiquitous computing world of today is Wireless Sensor Networks (WSN), consisting of node-based components in a mesh that detects the environment around it. The sensing and radio part of the WSN node are typically off-chip components which are needed in order to realize the required performance. This thesis sets forth to investigate how to use MicroElectroMechanical Systems (MEMS) resonators as signal processing units, directly integrated in Complementary Metal-Oxide Semiconductor (CMOS) technology. By integrating MEMS resonators directly with CMOS, one can omit some of the typical off-chip devices and thus enable more compact and cost-efficient WSN nodes.

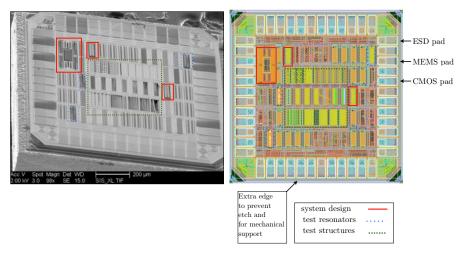

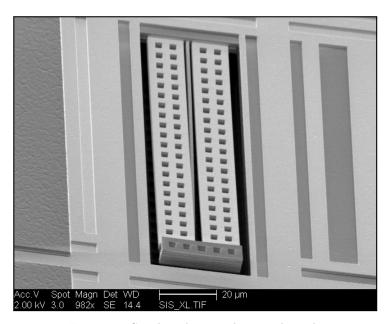

CMOS-MEMS resonator structures have been made by etching CMOS dies after being processed, thus defining structures from the metal layers offered in the CMOS process. Post-processing of CMOS dies was possible through a service known as Application Specific MEMS Process Service (ASIMPS) where Carnegie Mellon University (CMU) has etched and released the MEMS structures. This post-CMOS process was further developed by making MEMS out of two different 90 nm CMOS processes. Five different CMOS runs were performed, three at UiO and two at CMU in  $0.35~\mu\text{m}$ ,  $0.25~\mu\text{m}$  and 90 nm CMOS processes from both Taiwan Semiconductor Manufacturing Company (TSMC) and ST Microelectronics (STM).

Different resonator topologies have been modeled, simulated and measured. A set of basic resonators were combined in order to make more advanced multiport MEMS resonators, enabling down-mixing of high-frequency signals to an intermediate-frequency. Composite resonators have been connected at selected nodal points in order to obtain higher order filtering characteristics. Higher-order MEMS filters were made in different ways and compared. Soft frequency tunable MEMS resonators and multi-mode features of composite MEMS resonators were investigated.

Composite MEMS resonators and CMOS amplifiers have been combined to convert the resonator current to a voltage, enabling voltage-to-voltage filters and mixer-filters. High gain, low-noise Trans-Impedance Amplifiers (TIAs) was made and different Trans-Impedance Amplifier (TIA) topologies were evaluated. The various combinations of MEMS and CMOS resulted in unique filtering capabilities with an increased Q-factor and low-noise performance.

### ACKNOWLEDGEMENTS

During my thesis I have been able to work with a diverse set of competent scientists, researchers and professors that all have been very helpful to me during my PhD. First and foremost I would like to thank my supervisor Oddvar Søråsen who has been there for me for many years here at UiO. Without his support, advices and guidance I would not have been where I am today. My two co-supervisors Tor Fjeldly from UNiK and Geir Uri Jensen from SINTEF have been valuable resources with regular half-year meetings and they have given me the opportunity to use certain facilities and measurement equipment at MiNaLab.

Through a scholarship from the Fulbright Foundation, I was able to do a visiting research scholar stay at Carnegie Mellon University in Pittsburgh, USA. That stay has been incredibly valuable and insightful for me, and I am grateful that my two mentors professor Gary K. Fedder and professor Tamal Mukherjee gave me the opportunity to do research at their university. I learned a lot by working in the project named "Self-Healing MEMS" at CMU with PhD students Andrew Phelps, Chih-Ming Sun, Gokce Keskin and Jonathan Rotner.

The Nanoelectronics group at Institute of Informatics deserves a great deal of credit for being an open and including group. During my PhD, my research group evolved into a more social atmosphere, so a special thanks goes out to my senior engineer Olav Stanly Kyrvestad for his social and academic contributions. I've shared office with Jørgen Michaelsen during most of the time spent working on my PhD thesis where we have done collaborative research and we've had many scientifically related and non-related discussions together.

Finally I would like to thank my family and friends who have been very supportive during my thesis and have been a great aid and listening to me talk about my thesis!

### **PREFACE**

This PhD evolved from my undergraduate studies at Vestfold University College and through working part time at SensoNor. From there I discovered that the typical method of utilizing MEMS sensors was to make the MEMS using a custom process and bonding a separate ASIC die to connect the two worlds together. This subject fascinated me, and it became obvious to me that there was a clear interest of attempting to tightly integrate MEMS with advanced signal processing through a more common platform.

My path then lead me to do my graduate studies at University of Oslo where I was attracted to the world of CMOS and the nanoscale transistors. Doing my Master Thesis at UiO significantly increased my interest for further research on this topic. Thus by engaging in a PhD position at UiO, my work on combining MEMS and CMOS had started.

The job atmosphere at my Nanoelectronics group was diverse, interesting and complementary. Indulging in physics, mathematics, informatics, mechanics and electronics made my work environment both challenging and inspiring. Through a scholarship from the Fulbright Foundation I was able to do research at an American university in Pittsburgh, Pennsylvania. My destination was Carnegie Mellon University with a renowned expertise in this particular research field. My stay there proved to be very valuable for my PhD thesis. After my stay at Carnegie Mellon University I had started the final path of my PhD in a new building: "Ole Johan Dahls hus". With it came an entirely new environment and a refreshing end of my PhD.

This PhD thesis supplies the reader with new knowledge about how to combine CMOS and MEMS and to learn how one can use vibrating micromechanical structures in combination with on-chip amplifiers to signal process intermediate and high-frequency signals.

# Contents

| $\mathbf{A}$ | BSTR       | ACT                                        | III          |

|--------------|------------|--------------------------------------------|--------------|

| A            | CKNO       | DWLEDGEMENTS                               | $\mathbf{V}$ |

| Ρı           | REFA       | CE                                         | VII          |

| 1            | Int        | RODUCTION                                  | 1            |

|              | 1.1<br>1.2 | Thesis outline                             | 3<br>4       |

| 2            | Exp        | PANDING CIRCUIT DESIGN WITH MEMS           | 5            |

|              | 2.1<br>2.2 | MEMS and their applications                | 5<br>10      |

| 3            | RES        | SONATOR MODELING                           | 21           |

|              | 3.1        | Mechanical beam model                      | 21           |

|              | 3.2        | Electromechanical resonator description    | 25           |

|              | 3.3        | Damping mechanisms and the Q-factor        | 30           |

|              | 3.4        | Non-linearity effects                      | 33           |

|              | 3.5        | Gap reduction technique                    | 37           |

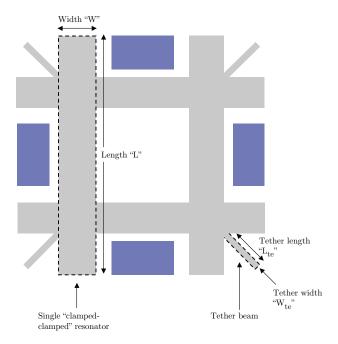

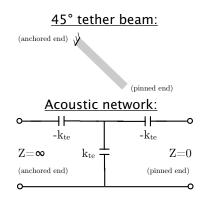

| 4            | Cor        | MPOSITE RESONATOR STRUCTURES               | 43           |

|              | 4.1        | Composite resonator modeling               | 43           |

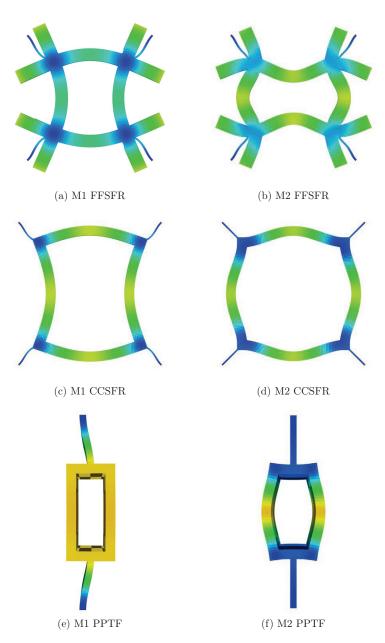

|              |            | 4.1.1 Square-Frame Resonators              | 44           |

|              |            | 4.1.2 The Parallel-Plate Tuning Fork       | 50           |

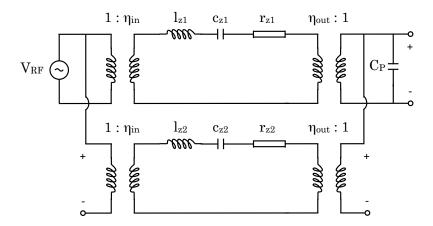

|              |            | 4.1.3 Electromechanical equivalent circuit | 53           |

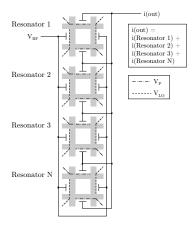

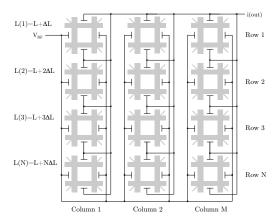

|              | 4.2        | Coupling techniques                        | 54           |

|              |            | 4.2.1 Electrical summation                 | 54           |

|              |            | 4.2.2 Mechanical summation                 | 58           |

|              | 4.3        | Mechanically coupled composite resonators  | 60           |

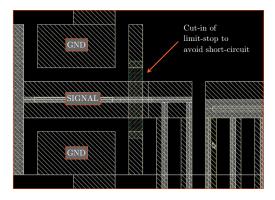

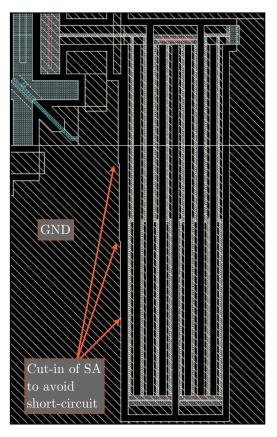

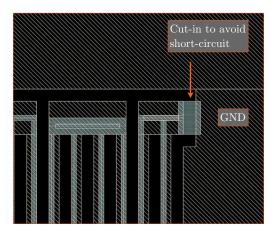

|              | 4.4        | CMOS-MEMS layout considerations            | 66           |

| 5            | CM         | IOS-MEMS IMPLEMENTATIONS                   | 73           |

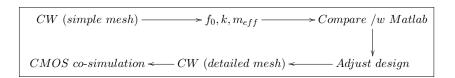

|              | 5.1        | Simulation techniques                      | 73           |

|              | 5.2        | Tuneable MEMS VCO for A/D converter        | 74           |

|              |            | 5.2.1 System idea                          | 74           |

|              |            | 5.2.2 Sustaining amplifier design          | 76           |

#### CONTENTS

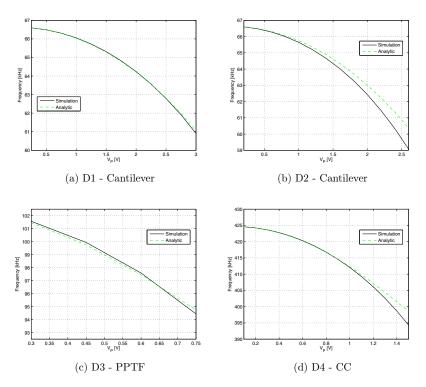

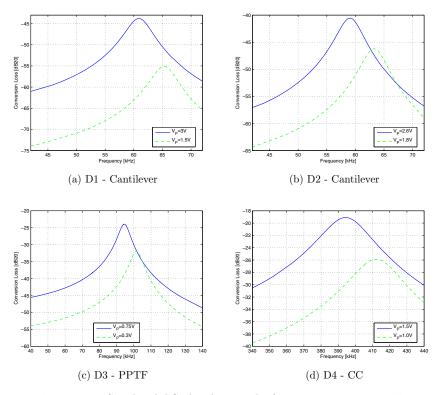

|   |              | 5.2.3  | Results from soft-tuneable resonator implementations | 77  |

|---|--------------|--------|------------------------------------------------------|-----|

|   | 5.3          | Low-n  | oise amplifier design considerations                 | 87  |

|   |              | 5.3.1  | Noise contributions                                  | 87  |

|   |              | 5.3.2  | Investigating amplifier toplogies                    | 91  |

|   | 5.4          | SFR a  | and PPTF implementations                             | 99  |

|   |              | 5.4.1  | TSMC 0.35 $\mu$ m FFSFR filters                      | 99  |

|   |              | 5.4.2  |                                                      | 107 |

|   | 5.5          | Summ   | nary of results                                      | 113 |

| 6 | Hie          | H-LEV  | EL TRADEOFF PARAMETERS                               | 115 |

|   | 6.1          | Discus | ssing the trade-off parameters                       | 116 |

|   | 6.2          | Comp   | arison of research results                           | 120 |

|   | 6.3          | Sugges | stions for improved filter design                    | 121 |

| 7 | Cor          | NCLUSI | ION                                                  | 125 |

|   | 7.1          | Thesis | s summary and conclusions                            | 125 |

|   | 7.2          | Furthe | er work                                              | 127 |

| A | PPEN         | DIX    |                                                      | 129 |

|   | $\mathbf{A}$ | Beam   | boundary conditions                                  | 129 |

|   | $\mathbf{B}$ | Non-li | near capacitive higher order components              | 135 |

|   | $\mathbf{C}$ |        |                                                      | 138 |

| A | CRON         | IYMS   |                                                      | 145 |

| N | OME          | NCLAT  | URE                                                  | 147 |

| L | IST O        | F FIGU | URES                                                 | 149 |

| L | ST O         | F TABI | LES                                                  | 153 |

| R | IBLIO        | GRAPI  | ну                                                   | 155 |

## Chapter 1

#### INTRODUCTION

"To make future wireless sensor devices smaller, smarter and more autonomous, fully integrated and multifunctional nodes will be required. It is challenging to design on-chip RF front-end devices, and today's solutions typically use discrete, off-chip components to meet the RF performance requirements (external inductors, crystals, SAW and ceramic filters). It has been shown that micromachined components (RF MEMS) can beneficially replace a great number of those bulky off-chip components with even better performance, smaller size and lower power consumption."

J. E. Ramstad et al.

In Proceedings of DTIP 2009

The ongoing trend known as "More Than Moore" focuses more on total system integration rather than just reducing the Complementary Metal-Oxide Semiconductor (CMOS) transistor size [1]. Including typical off-chip components on the same die provides a common platform for different technologies. MicroElectroMechanical Systems (MEMS) has traditionally been a technology that has a separate production method compared to CMOS. MEMS devices are typically coarse-grain in size compared to the nanoscale CMOS transistors. Different MEMS oscillators and sensors are used extensively in many commercial and industrial products, therefore there is a driving force of finding a common platform for combining these two technologies. In short, combining MEMS directly with CMOS allows for much more compact devices with less parasitics, lower power consumption and larger Q-factors. For Wireless Sensor Networks (WSNs), the sensing devices and radio transmitting devices are components which could be directly integrated on-chip with the CMOS circuitry.

A tight integration of MEMS with CMOS can result in a reduction of space by including typical off-chip components on the same chip. This compact integration will also result in reduced power consumption, less parasitics and a reduced component price. A somewhat different sensor and transceiver technology with slightly lower overall performance may turn out to be adequate enough for certain application areas. As a consequence of "More Than Moore", it is believed that a new trend will develop within this CMOS industry where the most cost effective integration method with sufficient performance will become popular. My work will demonstrate one of many methods of integrating CMOS with MEMS to demonstrate tight and compact technology integration. Another aspect of this thesis is to evaluate a different method of processing signals than what is commonly done. This is done by utilizing micromechanical beams in different ways used as filters, mixer-filters or oscillators.

This thesis investigates methods of how to combine electronics and micromechanical parts in order to process signals in the context of WSN applications. The combination of MEMS directly in CMOS has certain advantages and disadvantages as will be described later on in this thesis. The combination method has been performed in various CMOS processes of 0.35  $\mu$ m, 0.25  $\mu$ m and 90 nm technology nodes. The newer CMOS processes have certain advantages such as lower power consumption but will also have certain drawbacks, and a comparison between the processes will be shown. The combination of CMOS and MEMS creates a foundation to make resonators and filters where the signal processing is performed in the mechanical domain.

On-chip amplifiers combined with these micromechanical resonators can give filters with a large Q-factor compared to typical off-chip components used today. The embedded CMOS circuitry is used to enhance filter characteristics through controlled impedance levels and self-adjusting bias levels. The combination of CMOS and MEMS results in a voltage-to-voltage conversion with low noise levels. Electrically or mechanically connected resonators combined with on-chip amplifiers results in filters and mixer-filters which may be used in front-end transceivers. The filter characteristics of these CMOS-MEMS integrated filters will be shown with suggestions for improvements and further research.

A part of this thesis has been performed at Carnegie Mellon University in Pittsburgh, Pennsylvania USA. An exchange stay from 2009–2010 has proved to be very valuable for this thesis. The project that I participated at CMU was known as "Self-Healing MEMS Resonators" which was sponsored by DARPA. Design, simulation and results from system implementations of that project will be shown later in this thesis. The integration of CMOS and MEMS in this thesis has been possible through the Application Specific MEMS Process Service (ASIMPS) and through the contact and connections with CMU [2, 3]. The CMOS-MEMS integration method is known as post-CMOS or CMOS-MEMS and will be further explained in this thesis. The ASIMPS allows fabless customers to do prototyping on CMOS-MEMS integrated designs at an acceptable price. The outline of this thesis is shown in the next section.

#### 1.1 Thesis outline

This thesis is built up using the following disposition:

Chapter 2: Expanding circuit design with MEMS - Examples of application areas where MEMS resonators can be used to expand CMOS circuit design are described. The method of how to combine CMOS and MEMS is explained with examples, and tentative design rules for CMOS-MEMS are derived.

**Chapter 3: Resonator modeling** - Mechanical beams with different boundary conditions are modeled. The method of how to use the mechanical beams as electrical signal processing elements is explained and low-level system performance parameters, damping mechanisms and non-linear effects are explained.

Chapter 4: Composite resonator structures - Beams with different boundary conditions are combined to create more complex, composite resonators, allowing resonators with multiple ports and multiple modes. Theory and analytical equations are shown to create a base foundation for these composite resonators. Theory and examples of how to couple composite resonators to create higher order filters are shown.

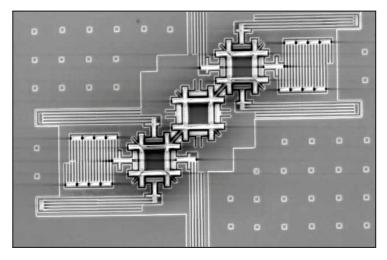

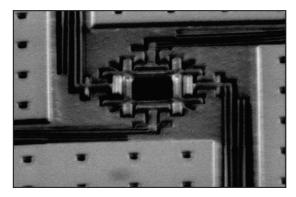

Chapter 5: CMOS-MEMS implementations - Actual implementations of CMOS and MEMS integrated together are demonstrated with schematics, layout and SEM photos. These implementations are in various CMOS technologies. Analytical results, simulation results and measurements from these CMOS-MEMS implementations are presented.

Chapter 6: High-level tradeoff parameters - By investigating the most promising CMOS-MEMS filter in this work, high-level system parameters are derived and compared with other research results. The purpose of this chapter is to show important higher level filter performance parameters, using the low-level parameters defined in the previous chapters. The chapter ends with suggestions of how to improve filter design by using refined high-level and low-level parameters.

#### 1.2 Contributions and publications

The list below shows the papers produced in this thesis and Table 1.1 shows the different CMOS runs that were performed during this PhD thesis.

- [4] O. Soeraasen and J. E. Ramstad. From MEMS Devices to Smart Integrated Systems. In *Journal of Microsystem Technologies*, vol. 14, no. 7, pages 895–901, Springer 2008.

- [5] J. E. Ramstad, K. G. Kjelgaard, B. E. Nordboe and O. Soeraasen. RF MEMS front-end resonator, filters, varactors and a switch using a CMOS-MEMS process. In *Proceedings of DTIP 2009, Symposium on Design, Test, Integration and Packaging of MEMS/MOEMS*, pages 170–175, IEEE 2009.

- [6] J. E. Ramstad and O. Soeraasen. Higher order FFSFR coupled micromechanical mixer-filters integrated in CMOS. In the 28th Proceedings of Norchip, pages 1–4, IEEE 2010.

- [7] J. A. Michaelsen, J. E. Ramstad, D. T. Wisland and O. Soeraasen. Low-power Sensor Interfacing and MEMS for Wireless Sensor Networks. A book chapter in *Wireless Sensor Networks*, pages 373–395, InTech 2011.

- [8] J. E. Ramstad, J. A. Michaelsen, O. Soeraasen and D. T. Wisland. Implementing MEMS resonators in 90 nm CMOS. In *Proceedings of DTIP 2011*, Symposium on Design, Test, Integration and Packaging of MEMS/MOEMS, pages 463–470, IEEE 2011.

- [9] J. E. Ramstad and O. Soeraasen. Modeling and design of higher order, multimode, multi-port MEMS resonators in 90 nm CMOS. In *Proceedings of the Eurosensors XXV Conference*, pages 1–4, Elsevier 2011.

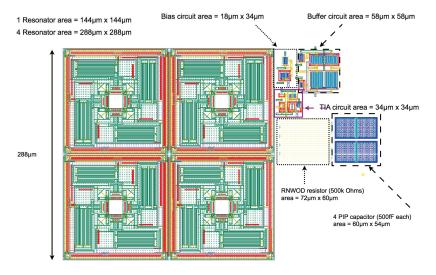

|            | Process                   | Application                                 | Loc. |

|------------|---------------------------|---------------------------------------------|------|

| Nov. 2008  | STM $0.25~\mu\mathrm{m}$  | 45° coupled base resonators as filters      | UiO  |

| July 2009  | STM 90 nm                 | Tuneable MEMS VCO for A/D converter         | UiO  |

| Oct. 2009  | TSMC $0.35~\mu\mathrm{m}$ | FFSFR mech. conn. mixer-filters w/diff. amp | CMU  |

| March 2010 | TSMC $0.35~\mu\mathrm{m}$ | El. summed FFSFR mixer-filter w/ CS TIA     | CMU  |

| Oct. 2010  | TSMC 90 nm                | PPTF, CCSFR and FFSFR mixer-filters w/TIA   | UiO  |

Table 1.1: CMOS runs during the PhD thesis

In publications [5] and [7], co-authors have contributed with details on varactors, switches and FDSMs respectively. The author of this thesis has a large contribution to most of the papers and publications produced in this thesis. The acronyms in Table 1.1 are explained later on in this thesis. Three out of the five tapeouts have been performed at UiO while two tapeouts have been performed during the stay at CMU in 2009–2010. As can be seen in Table 1.1, 0.35  $\mu$ m, 0.25  $\mu$ m and 90 nm CMOS processes have been used. An evaluation of these processes is done in chapter 2, and the system implementations are shown in chapter 5.

## Chapter 2

# EXPANDING CIRCUIT DESIGN WITH MEMS

A DVANCED signal processing can be complemented with other technology platforms in order to enhance system capabilities and performance. A CMOS LC tank with mixer and an LNA for front-end transceiver systems can be made with CMOS inductors and varactors which unfortunately provide low Q-factors for the filter part of the system. Circuit design can be expanded by using a different technology platform for the filter part, as well as including the filter as a part of the mixer, making it a mixer-filter. On-chip filters or mixer-filters with a large Q-factor will put less stringent requirements on the amplifier design and may alleviate the need for a separate mixer, allowing mixing high frequency signals down to an intermediate frequency and perform filtering at the same time.

This chapter will show application areas for integration of CMOS with MEMS including some examples of compact integration to illustrate the possibilities of expanding circuit design with MEMS. The chosen CMOS-MEMS integration method is described, pros and cons of different technology nodes will be highlighted and tentative CMOS-MEMS design rules are developed.

#### 2.1 MEMS and their applications

Using MEMS to complement CMOS circuit design can be done in different ways. Using on-chip micromechanical filters, oscillators or sensor components is a popular research field. The research in my work puts these MEMS resonators combined with CMOS in a context of Wireless Sensor Networks. These micromechanical signal processing elements or sensor elements can be tightly integrated with CMOS.

Table 2.1 shows a list of various research facilities, institutes and universities which perform research on MEMS sensors or front-end transceiver components, all integrated with CMOS with different methods. As can be seen, research is being done in France, Finland, Spain, Canada, USA and Taiwan. Using inductors, varactors or micromechanical resonators for front-end signal processing is shown to be a popular research topic.

| Parameter                           | Research area                                                 |

|-------------------------------------|---------------------------------------------------------------|

| U. of Barcelona [10, 11, 12]        | Resonators, oscillators and mixer-filters                     |

| U. of California, Berkeley[13, 14]  | Resonator amplifiers, mixer-filter, oscillators, switches     |

| Carnegie Mellon U.[15]              | Biological sensors, gyroscopes, filters, inductors, varactors |

| U. of Florida [16]                  | Accelerometers, gyroscopes                                    |

| Georgia Institute of Tech.[17]      | Bulk Acoustic Wave (BAW) resonators                           |

| National Chung-Hsing University[18] | Sensors and resonator filters                                 |

| National Tsing Hua University [19]  | Sensors, resonators and oscillators                           |

| U. of Waterloo [20]                 | Inductors, resonators                                         |

| VTT [21]                            | Filters, resonators, transmission lines                       |

Table 2.1: Research areas

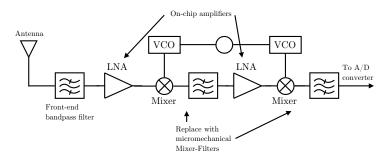

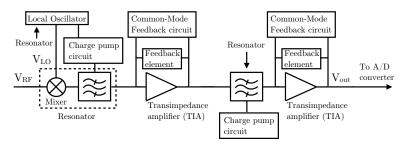

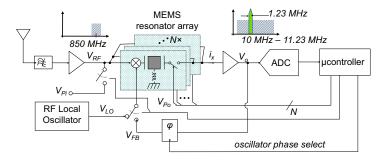

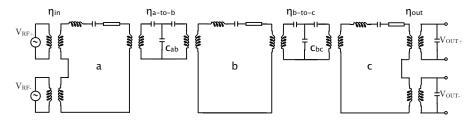

Fig. 2.1 shows a simple transceiver architecture [22]. The various processing elements shown in Fig. 2.1 can potentially be done with different on-chip micromechanical components. Typically off-chip components that perform filtering and mixing tasks may offer better specifications such as lower Insertion Loss (IL), higher filter Q-factor or lower power consumption. The idea of using MEMS resonators as filtering components is to alleviate typical off-chip components for some of these tasks by utilizing on-chip electronics combined with MEMS. The end result of doing this to obtain almost the same results with more flexibility by using the integrated electronics to tune and control the filter frequency.

Figure 2.1: Simple transceiver architecture

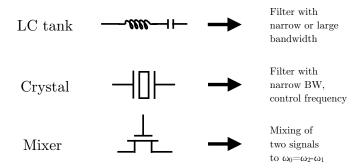

Fig. 2.2 shows typical implementations of filters, oscillators and mixer-filters. An LC tank can be done either on-chip or off-chip, but it only has two terminals, and for CMOS LC tanks the Q-factor is low. An LC tank can offer a narrow or a large bandwidth, depending on the desired usage. A crystal is a component which is typically made of a Quartz material which offers a very large Q-factor, low phase-noise and therefore a very clearly defined resonance frequency. The crystal may also be used to tune the resonance frequency through a third terminal using a polarization voltage on the resonator. Quartz are typically one-port devices, therefore tuning the frequency with a polarization voltage may become difficult. For the same reason Quartz crystals typically offer significant feedthrough from the input to the output of the device which must be compensated. Finally, a mixer can be implemented by using transistors, thus mixing two signals  $\omega_1$  and  $\omega_2$  down

Figure 2.2: Examples of typical filter, oscillator and mixer realizations

to a frequency defined as  $\omega_0 = \omega_2 - \omega_1$ . Using transistors to mix down frequency is a typical method of mixing two signals, although RF frequency capable transistors must be used. Even though RF transistors are specially implemented from the foundry they will also have feedthrough from the input to the output.

By using more complex MEMS resonator architectures, it is possible to include more terminals, reduce feedthrough from the various terminals and to include on-chip electronics to automatically adjust desired parameters. CMOS-MEMS implemented resonators can offer more complex signal processing capabilities by combining the MEMS resonators with CMOS circuitry as well as reducing cost and size. In addition to this, less off-chip engineering will be required, and external impedance matching is not required because everything is done on-chip. This is true for frequencies that are sufficiently low, i.e. lower than the typical 2.4 GHz consumer frequency. Any impedance matching of MEMS resonators must be adjusted to match the following amplifier or any electronics thereafter.

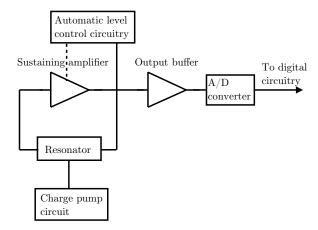

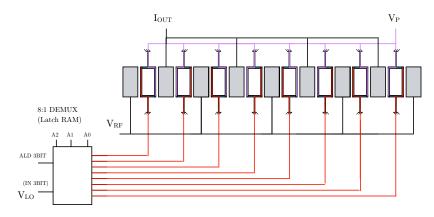

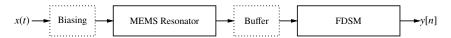

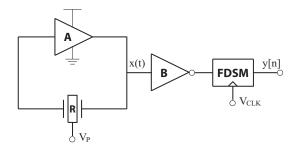

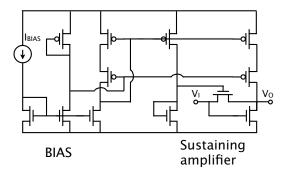

Figure 2.3: Voltage-Controllable Oscillator with MEMS resonator and self-adapting electronics

One example of using MEMS and CMOS together to complement each other is shown in Fig. 2.3. It shows the realization of using the MEMS resonator in a feedback circuit including a sustaining amplifier to make an oscillator circuit. Since the MEMS resonator is a passive element, it requires an amplifier to initiate and sustain oscillation. An Automatic Level Control (ALC) circuit is included to adjust biasing levels at the input and output of the sustaining amplifier. If large voltage levels are required for the MEMS resonator, a charge pump is also implemented. The output of the oscillating circuit goes to an output buffer and a following A/D conversion step. This type of circuit can also be used as a Voltage Controlled Oscillator (VCO) circuit, adjusting the resonance frequency by increasing a polarization voltage.

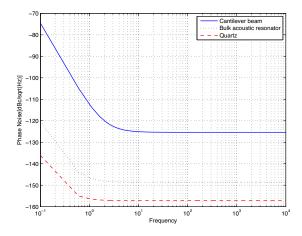

Oscillator circuits or VCO circuits both place stringent requirements on the passive element which dictates the resonance frequency as well as any parasitics from the amplifier. CMOS-MEMS implemented resonators have a low Q-factor compared to state-of-the-art Quartz or MEMS oscillator implementations [15]. However, by utilizing a clever and complex resonator architecture, feedthrough can be substantially reduced. The resulting phase noise of such CMOS-MEMS implemented oscillator circuits may not be as good as other implementations, however the resulting performance may be "adequate" through the usage of CMOS circuitry.

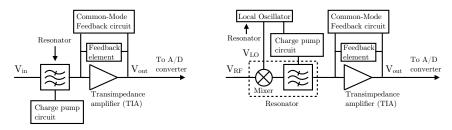

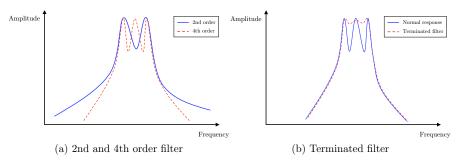

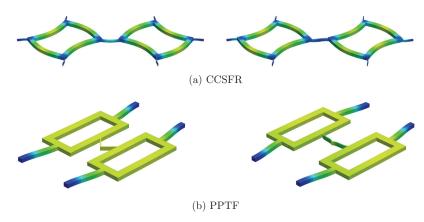

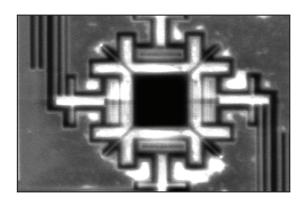

Figure 2.4: Examples of CMOS-MEMS filters and mixer-filters

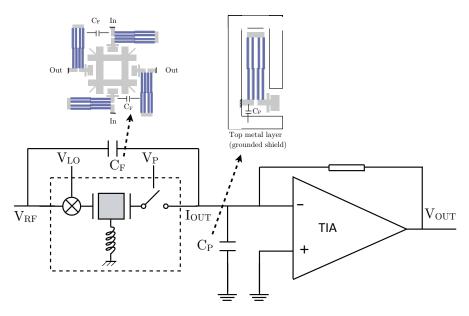

The left part of Fig. 2.4 shows CMOS-MEMS implemented resonator used as a filter. A charge pump circuit can be implemented on-chip to increase the polarization voltage, thus the total filter will comply with voltage levels required from the CMOS foundry design rules. Following the output of the resonator filter is a Trans-Impedance Amplifier (TIA) with a feedback element and a Common-Mode Feedback (CMFB) circuit. The CMFB ensures correct voltage levels of the input and output of the amplifier. The feedback element can consist of a resistor, capacitor or transistor and converts the motional current out from the resonator to a voltage at the output of the amplifier.

The right part of Fig. 2.4 demonstrates a RF signal mixed with an LO signal down to an Intermediate Frequency (IF). This IF signal is at the same frequency as the MEMS resonator and is further filtered through the resonator. Using multiple terminals on a resonator, it is possible to both downmix a signal and filter at the same time, using the one and same device to both tasks [23]. The LO frequency is generated from a Local Oscillator (LO) which can also be implemented as a

CMOS-MEMS resonator. The downmixed filtered current is then converted into an output voltage  $V_{out}$  by the same output circuitry.

Figure 2.5: Augmenting CMOS with MEMS resonator filters and mixer-filters

By combining both parts that were shown in Fig. 2.4, it is possible to achieve a total on-chip CMOS-MEMS mixer-filter and CMOS-MEMS filter with appropriate electronics. An example of this is seen in Fig. 2.5. At the receiver part of a transceiver system, mixing down an RF to IF is performed and then followed by low-noise amplifiers and an additional filtering step. All of this can be implemented using CMOS-MEMS resonator filters, mixer-filters and oscillators. The output from this system is then led to an Analog-to-Digital (A/D) converter. The system implementation of Fig. 2.5 is less dependent on impedance levels and voltage levels as they can be controlled internally. Even if the CMOS-MEMS resonators were to have large impedance values, this could be compensated for by using the on-chip circuitry to achieve a 1:1 conversion gain and still consuming little power.

| Pros of CMOS-MEMS                    | Cons of CMOS-MEMS             |

|--------------------------------------|-------------------------------|

| Integrate filters or sensors on-chip | Possible small electrode area |

| Reduced parasitics                   | Material composition limited  |

| More routing capabilities            | Comply to CMOS foundry rules  |

| Compatible with CMOS technologies    | Possible lower Q-factor       |

| Can reduce bill of materials (BOM)   | Packaging challenges          |

Table 2.2: Pros and cons of CMOS-MEMS integration

A summary of pros and cons of implementing MEMS components directly in CMOS is shown in Table 2.2. These advantages and disadvantages of making MEMS directly in CMOS will be further pointed out throughout this chapter. It should be mentioned that the final advantage of using CMOS-MEMS devices is that even though it has some drawbacks, it may turn out that this implementation method may offer sufficient performance at a cheap price.

This work will investigate one of several methods of combining CMOS and MEMS which is shown in section 2.2.

#### 2.2 Integrating MEMS with CMOS

All methods of integrating MEMS with CMOS will face different types of challenges. A common denominator for these integration methods is that in order for compact integration to take place, the MEMS process must adapt to the CMOS process line as foundries typically do not want to change their existing process line infrastructure too much. All integration methods must take into consideration the fabrication temperature, photolithography mask complexity, internal stress, acceptable materials, the possibility of creating good interconnections and using acceptable packaging methods [24, 25, 26].

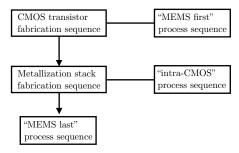

The different integration methods are illustrated in Fig. 2.6. A MEMS first method is more difficult to implement as the CMOS foundries are reluctant to accepting "dirty" silicon wafers which have been processed in beforehand. An example of MEMS first are processes that use Deep Reactive Ion Etching (DRIE) etches deep into the silicon to make microstructures from Silicon On Insulator (SOI). These SOI processes can offer lateral moving micromechanical resonators with a large electrode area and high Q-factor [27].

Figure 2.6: Process integration methods

An intra-MEMS process consists of integrating the MEMS part after the transistor fabrication part has been performed (deposition of polysilicon) but before the metallization sequence takes place. For polysilicon microstructures, this method makes it possible to anneal the polysilicon at high temperatures to get a good stress profile. This type of integration method is relatively complex as it disrupts the normal CMOS process flow, maybe requiring fabrication at different foundries.

The last integration method in Fig. 2.6 is the post-CMOS method which implements microstructures after the metallization fabrication sequence has been performed. This is known as "MEMS last" or post-CMOS. Because the polysilicon and interconnects have already been made, the thermal budget is critical. The deposition temperature for the structural material must be lower than this thermal budget in order to not alter the characteristics of the transistors and the interconnects.

There are two different types of post-CMOS implementation methods. The first one is based on depositing materials on top of the top metal layer to make microstructures. The second method is based on using the embedded metal layers

to make microstructures.

An example of the first post-CMOS method is by depositing AlN on top of Pt to make Bulk Acoustic Wave (BAW) resonators. The deposition temperatures during fabrication comply with the acceptable temperatures allowed by the foundry. This method does not damage CMOS interconnects or the CMOS transistors after fabrication.

There is a lot of research going on in the area of integrating MEMS and CMOS. My work does not go into the depth of describing the different integration methods and refers to the literature [24, 25, 26] for in depth details.

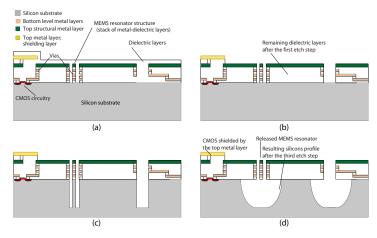

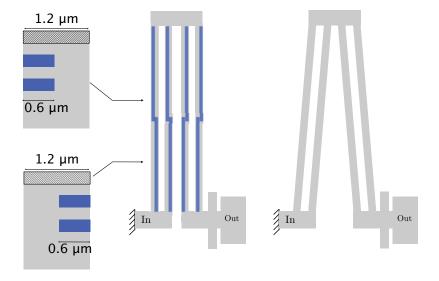

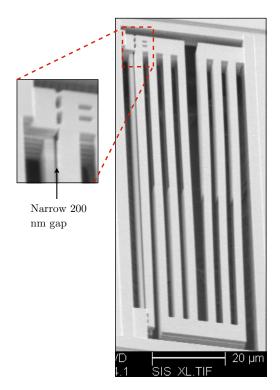

My work is based on a post-CMOS process where the already existing metaldielectric stack from the CMOS is used to make micromechanical structures. This post-CMOS process has been made possible through a service known as Application Specific MEMS Process Service (ASIMPS), offered both in Europe and in USA [2, 3]. The process steps of this post-CMOS process are shown in Fig. 2.7.

Fig 2.7(a) shows the die immediately after being produced at the respective CMOS foundry. The yellow metal layer is typically set to be the top metal layer from the CMOS process and is used to protect the CMOS circuitry from becoming etched during processing. The green metal layer is the top structural layer and is used to define the MEMS structures.

Figure 2.7: General CMOS-MEMS process etch steps

In Fig. 2.7(b) the openings without the green metal layer allows for etching trenches down towards the silicon substrate by using an anisotropic etch step sequence. An optional DRIE etch step is shown in Fig. 2.7(c) etching about 35  $\mu$ m into the silicon substrate. The last step is shown in Fig. 2.7(d) where an isotropic etch releases the MEMS structures, creating circular trenches which cut in under the openings. This process step is tentative and can be modified in many ways. However, for this thesis, Fig. 2.7 shows the general dry etch steps that have been used in this thesis through ASIMPS.

The process flow in Fig. 2.7(b) is based on Table 2.3. Etching the dielectric where there are narrow gaps is the biggest challenge of this process due to chemical reactions during the RIE etch. More details of this etch process is found in [28].

| Parameter       | Value      |

|-----------------|------------|

|                 | $20 CHF_3$ |

| Gas flow [sccm] | $20 CF_4$  |

|                 | $95 O_2$   |

| Pressure [mT]   | 100        |

| Power [W]       | 65         |

| DC bias [V]     | 270        |

| Time [min]      | $\sim 120$ |

Table 2.3: Typical dielectric etch parameters

The reason for the dielectric step in Fig. 2.7(b) being the most difficult etch step is because of the fluorocarbon  $(C_xF_y)$  reactions during the dielectric etch [28].  $CHF_3$ ,  $CF_4$  and  $O_2$  in Table 2.3 contributes to this unwanted fluorocarbon reaction. In general, there are four unknown factors to the dielectric etch:

- Type of etch equipment used for the dielectric etch

- The type of dielectric material in the CMOS process

- The thickness of the dielectric layer(s)

- Type of metal layer, i.e. aluminum or copper

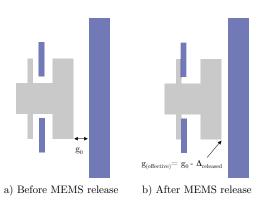

It is also possible to take the gap between two structures into account as an unknown factor. However, due to these uncertain factors – it is not possible to clearly define the gap between two structures. As will be described in chapter 3.5, a method of changing the gap after the etching has been performed is used in order to achieve a controlled gap. This means that it is possible to tune the process to get an adequately small gap size and then later on control the actual gap. The etch equipment may be different for the different processing steps, i.e. Plasma-Therm 790 parallel-plate RIE system for the dielectric etch and Surface Technology Systems (STS) for the deep silicon RIE etch [28]. Steps (c) and (d) in Fig.2.7 are less challenging than the dielectric etch, although they may also contribute to determine post-CMOS design rules.

This thesis is will not go into the very depth of topic of post-CMOS processing as it is possible to write a PhD thesis on that topic alone [28]. It should be mentioned that the materials offered in a CMOS process have changed throughout the years, going from aluminum to a newer dual Damascene copper process. This means that the etch process must be modified slightly in order to accommodate for this copper composite material. The challenge of etching the dielectric layer remains the most difficult etch step, which is why this thesis relies on using a gap reduction technique after processing.

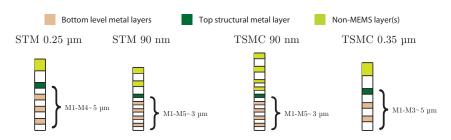

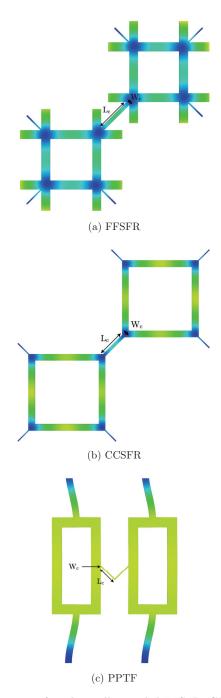

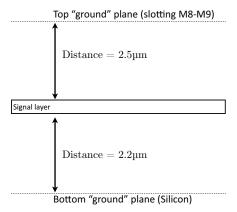

Figure 2.8: Cross section of the selected CMOS processes

This work has implemented MEMS resonators in four different CMOS processes, all through ASIMPS. Design rules for the official CMOS-MEMS process are offered by ASIMPS and are not shown here due to copyright rules. This thesis has attempted to implement CMOS-MEMS structures in more modern and fine-pitch CMOS processes (sub 100 nm CMOS processes): An unofficial development of the ASIMPS in two 90 nm CMOS processes has been attempted. This section will describe and show the possibilities that open up when migrating from coarse-grain (large transistor sizes) CMOS to fine-pitch CMOS. Fig. 2.8 shows a cross section of various CMOS processes that are used in this thesis. These CMOS processes offer different structural thicknesses and a different amount of metal layers.

Table 2.4 shows extracted parameters for 4 different CMOS processes encountered in this thesis. The STM 0.25  $\mu$ m process became obsolete in 2009, and the STM 90nm became phased out to a newer STM 65nm process in 2010. One STM 0.25  $\mu$ m run was done in November 2008. Two TSMC 0.35  $\mu$ m runs were done while doing an exchange stay at CMU (2009-2010) and one TSMC 90nm run was done in October 2010. All implementations were performed using the ASIMPS service offered by CMU. Creating MEMS devices from two different foundries (ST Microelectronics and TSMC) as well as implementing MEMS designs in both coarse-grain (0.25 to 0.35  $\mu$ m) and fine-pitch CMOS (90 nm or smaller) has provided insightful information about CMOS-MEMS implementations. It should be mentioned that 0.35  $\mu$ m CMOS are stable and old processes which will still be around for a while, however they too will be phased out sometime in the future which was an important reason for investigating CMOS-MEMS implementations in 90nm CMOS.

|                                                               | STM 0.25 $\mu m$        | STM 90 nm             | TSMC 90 nm            | TSMC 0.35 $\mu m$       |

|---------------------------------------------------------------|-------------------------|-----------------------|-----------------------|-------------------------|

| # of metal layers                                             | 5                       | 7                     | 9                     | 4                       |

| Stack thickness [µm]                                          | $\sim 5 \mu \mathrm{m}$ | $\sim 3 \mu \text{m}$ | $\sim 3 \mu \text{m}$ | $\sim 5 \mu \mathrm{m}$ |

| Top stack layer                                               | M4                      | M5                    | M5                    | M3                      |

| Bottom stack layers                                           | M1-M3                   | M1-M4                 | M1-M4                 | M1-M2                   |

| Shield layer(s)                                               | M5                      | M6-M7                 | M6-M9                 | M4                      |

|                                                               | 1P5M aluminum           | 1P7M copper w/        | 1P9M copper w/        | 1P4M                    |

| Material features                                             | w/M1 as tungsten        | Dual Damascene        | Dual Damascene        | aluminum                |

|                                                               |                         | interconnect          | interconnect          |                         |

| $\sqrt{E/\rho}$ ratio $\left[\sqrt{\frac{Pa}{kg/m^3}}\right]$ | 6470                    | 4115                  | 4115                  | 5435                    |

Table 2.4: Extracted parameters for the selected CMOS processes

In this work, the microstructure which is a metal-dielectric composite is known as "the stack". The 0.25 and 0.35  $\mu$ m processes define roughly 5  $\mu$ m thick MEMS structures while the two 90 nm processes defines a stack of about 3  $\mu$ m thick. The two 90 nm processes were implemented as a variant of the standard ASIMPS service with extended etching time during dielectric etch in order to be able to etch narrow gaps and be able to etch away all the dielectric and get to the silicon level. With this in mind, both 90 nm processes were designed with a smaller thickness. Also, the lower-pitch processes have a different thickness composition compared to the coarse-grain processes as shown in Fig. 2.8.

Fig. 2.8 shows that the coarse-grain processes define a 5  $\mu$ m thick stack using 3 or 4 metal layers, while for the 90 nm processes, 5 metal layers must be used to achieve only 3  $\mu$ m thick structures. The TSMC 90 nm run, which was performed after the STM 90 nm run, was designed to have the same amount of metal layers (5) to define MEMS structures. This was done even though the process had two extra metal layers (M6 and M7) which in turn could have resulted in roughly 4.2  $\mu$ m thick structures. Certain beams tend to bend upwards after being released, this effect is known as curling. The underlying mechanisms and equations behind the curling phenomenon are explained in chapter 3.5. By making the stacks homogenous (that is, metal and dielectric are roughly equally thick), will reduce the amount of curling. Table 2.4 shows that the coarse-grain processes will have a higher  $E/\rho$  (Young's modulus E divided by material density  $\rho$  will define the resonance frequency, see chapter 3.1) ratio compared to the fine-pitch copper processes while the coarse-grain processes will allow for thicker structures instead and a larger electrode area. The fine-pitch CMOS processes, however, allows for more intricate routing capabilities as they have more bottom level metal layers.

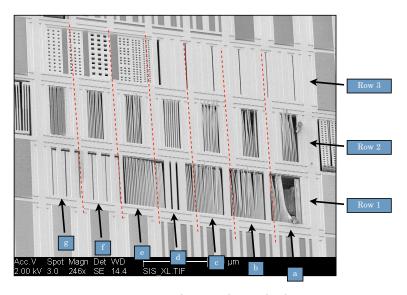

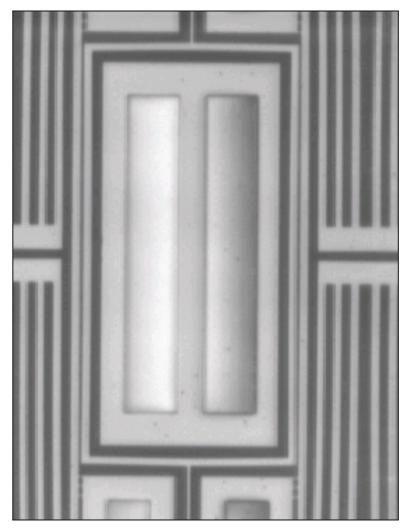

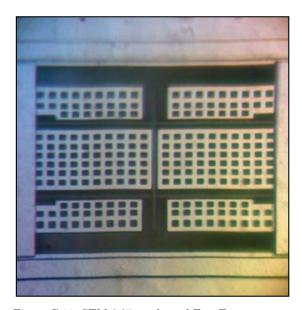

Figure 2.9: An optical test island

|       | a     | b     | С     | d         | e            | f               | g      |

|-------|-------|-------|-------|-----------|--------------|-----------------|--------|

| Row 1 | W=0.6 | W=0.8 | W=1.0 | W=1.2     | W=1.2        | W=20            | W=20   |

| Row 2 | M4M1  | M5M4  | M7M6  | M5 (poly) | M5 (poly VW) | M5 (w/o active) | Alucap |

| Row 3 | SA    | SA    | SA    | SA        | VH           | VH              | VH     |

Table 2.5: Optical test island table

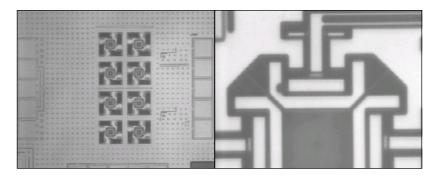

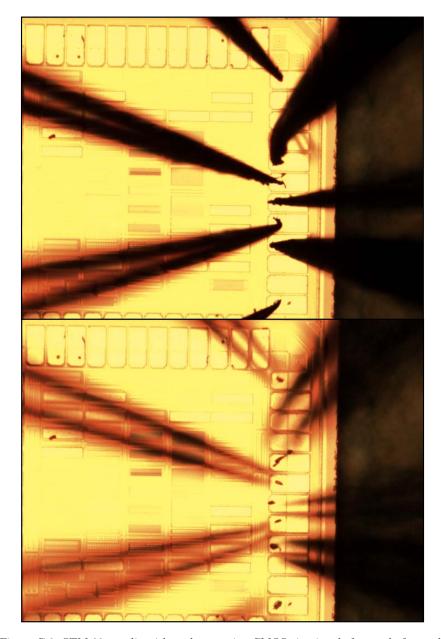

An implemented optical test island with various structures are demonstrated in Fig. 2.9. These test structures were implemented in a STM 90 nm process in the first attempt to make MEMS in fine-pitch CMOS. Table 2.5 shows the implemented optical test island where all dimensions are given in  $\mu$ m. Row 1 consists of cantilever beams with varying width (W). Row 1 f and g consists of 20  $\mu$ m wide beams. Row 2 consists of varying the amount of metal layers internally. Some of these structures include polysilicon beneath (2d and 2e) where 2e has Varied Width (VW) of the polysilicon layer. 2f consists of all metal layers up to metal 5 (M5) but without something called the Active layer (see p. 17–18) to see possible excessive out-of-plane curling. 2g consists of the aluminum cap layer from foundry, typically used for bond pads. The third row consists of rather wide beams of 40  $\mu$ m to see if they were released (SA=Semi-Anchored). Row 3e to 3g consists of holes with varying dimensions (VH=Vary Holes).

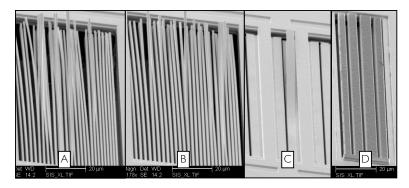

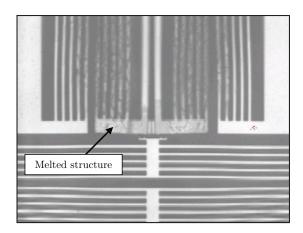

Figure 2.10: Delaminated and curling structures

Examples of delaminated and curling structures are seen in Fig. 2.10. In B, the far left three beams are homogenous consisting of metal 1 up to metal 5, while the other beams have a varying amount of metal layers embedded. A rather wide M5 part of a 20  $\mu$ m wide beam started to delaminate (detach itself from the underlying structure) in C. D shows a rough aluminum surface, showing that it reacts more with the etch recipe than the copper does.

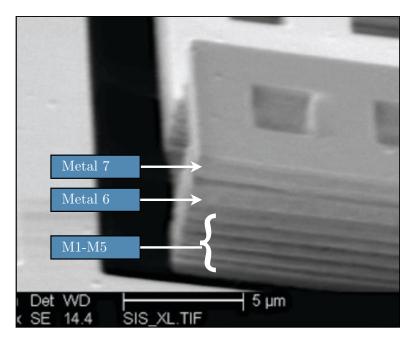

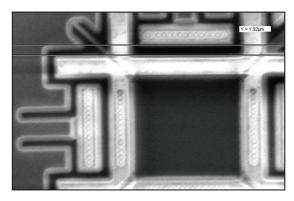

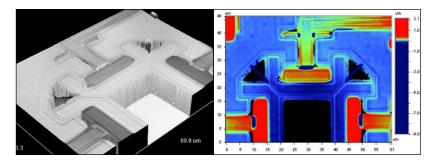

The cross section of a STM 90 nm released beam with metal layers can be seen in Fig. 2.11. From Fig. 2.11 it can be seen that metal layers M1-M5 have roughly equal thickness of the dielectric and metal layer while M6 and M7 have roughly twice the thickness. Table 2.6 shows the various thicknesses for both coarse-grain and fine-pitch CMOS processes. Exact thicknesses are not stated due to copyrights. However, the thicknesses in Table 2.6 give a general idea of possible stack thickness that can be made from metal-dielectric stacks.

Figure 2.11: SEM showing cross section of STM 90 nm metal layers

| Dim. in nm       | Coarse-grain CMOS | Fine-pitch CMOS |

|------------------|-------------------|-----------------|

| Metal 7          |                   | 800             |

| Via6 (M7-M6)     |                   | 800             |

| Metal 6          |                   | 800             |

| Via5 (M6-M5)     |                   | 800             |

| Metal 5          | 1200              | 300             |

| Via4 (M5-M4)     | 1200              | 300             |

| Metal 4          | 650               | 300             |

| Via3 (M4-M3)     | 650               | 300             |

| Metal 3          | 650               | 300             |

| Via2 (M3-M2)     | 650               | 300             |

| Metal 2          | 650               | 300             |

| Via1 (M2-M1)     | 650               | 300             |

| Metal 1          | 650               | 300             |

| Via (M1-Silicon) | 650               | 300             |

| Total thickness  | $\sim 7600$       | $\sim 6200$     |

Table 2.6: General thicknesses for coarse-grain and fine-pitch CMOS processes

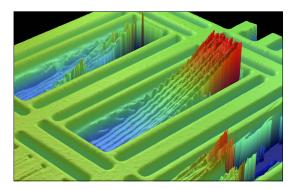

Released cantilever beams for process characterization are shown in Fig. 2.12. The curling and delamination effects shown in Fig. 2.10 and 2.12 can occur due to several reasons. The delamination effect consists of beams becoming detached from the underlying material, starting to curl out-of-plane even before the silicon release etch. This delamination effect occurs due to the processing temperatures and the geometry of the device as seen in Fig. 2.12.

Figure 2.12: Wyco measurement of cantilever beams

A stack which is as homogenous as possible will reduce the internal stress in the mechanical structure. If the internal stress is too large, the free parts of a released beam may bend upwards or downwards. One method of reducing the amount of internal stress is to include a layer offered from the CMOS process which is known as the Active layer. The Active layer is used to define transistors as areas with this layer will contain a small dielectric deposited at lower temperatures. This will result in a reduced internal stress and therefore a reduced amount of curling [28].

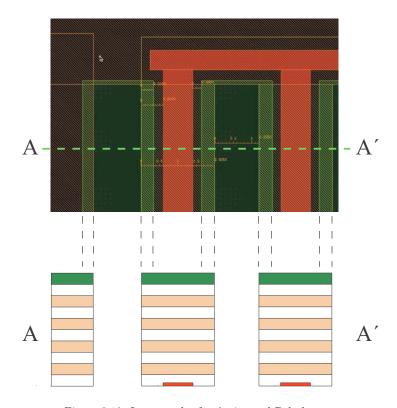

The implementation of Active layers can be seen in Fig. 2.13. The light green area defines the Active layer. The red layer is polysilicon. CMOS foundry rules do not allow the Active layer to cross the polysilicon unless polysilicon and the Active layer both overlap each other (something which is not possible for the structure which is to be released). Therefore structures with polysilicon beneath are partially covered by the Active layer. The CMOS rules state that there must be a small separation from the Active layer to the polysilicon layer. Also, if the polysilicon is too close to the edge of the structure, it may become etched.

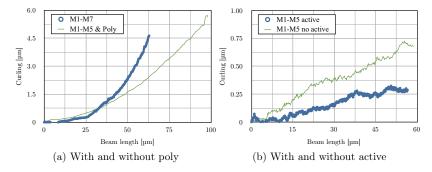

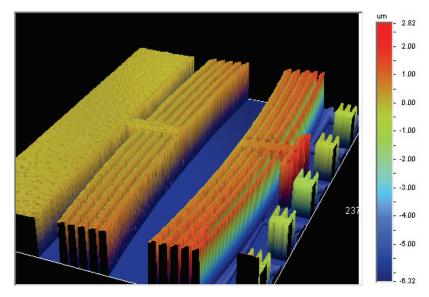

Fig. 2.14 shows Wyco measurement of long thin simply clamped beams. Fig. 2.14(a) shows beams consisting of M1-M7 (thick blue line) and M1-M5 including polysilicon beneath. It is clear that the M1-M7 beam has more curling, starting to bend 4.5  $\mu$ m at 60  $\mu$ m from the anchor. It was not possible to measure the whole 100  $\mu$ m long beam due to resolution limitations. This clearly shows that a more homogenous beam will curl less. Fig. 2.14(b) shows a M1-M5 beam with and without the Active layer. The thin green line is without the Active layer, showing that the curling is roughly 700 nm for a 100  $\mu$ m long beam compared to roughly 300 nm curling for the beam with the Active layer.

Figure 2.13: Layout rules for Active and Poly layers

Figure 2.14: Results from Wyco measurements

Figure 2.15: Corroded copper surface from a 2007 0.25  $\mu$ m BiCMOS tapeout

As seen in Fig. 2.15, corrosion of the surface material may occur when exposed to the environment for a too long time. If the die package is not sufficiently sealed, moisture from the environment will cause corrosion of the surface material. CMOS processes based on aluminum tend to corrode less. By cleaning with Ar or rinsing with IPA (Isopropynol Alcohol), it is possible to reduce this corrosion effect for copper composite materials [28]. Curling, delamination, corrosion, materials for the microstructures and possible Q-factor are challenges for this post-CMOS method.

|                        | Dim. $[\mu m]$ | Rule name | Comment            |

|------------------------|----------------|-----------|--------------------|

| Minimum width          | 1              | W1        | Delamination       |

| Maximum width          | 10             | W2        | CMOS rule          |

| Max length fixed-free  | < 60           | L1        | Delamination       |

| Max length fixed-fixed | < 100          | L2        | Curling            |

| Max stack thickness    | 5              | H1        | Preliminary        |

| Gap spacing            | 1.2            | S1        | Guarantees release |

| Poly from metal edge   | 0.6            | S2        | Prone to etch      |

| Active cover edge      | 0.3            | A1        | Reduce curling     |

| Active sep poly        | 0.1            | A2        | CMOS rule          |

Table 2.7: Tentative fine-pitch CMOS-MEMS design rules

Table 2.7 illustrates the developed rules for 90 nm CMOS designs. These design rules are tentative and are slightly adjusted compared to the coarse-grain CMOS-

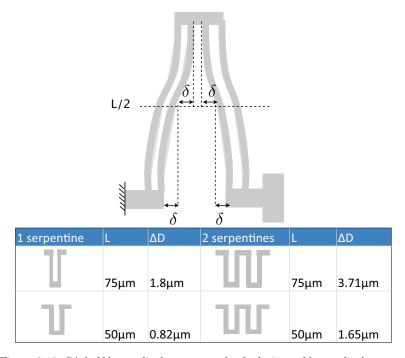

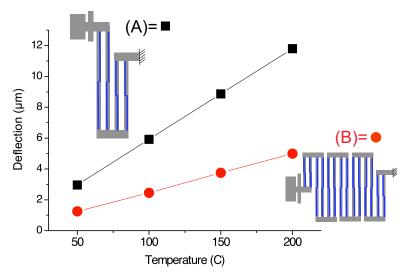

MEMS implementations. For example, to avoid delamination of structures, the width should be 1  $\mu$ m or larger. However, if a beam is sufficiently short and fixed at two ends, the width may be designed to be less than 1  $\mu$ m. The CMOS foundry places maximum widths for the structures, although by clever design it is possible to create larger widths. Due to curling and delaminated structures, a maximum length has been set for fixed-free and fixed-fixed structures. The maximum thickness is given by the selected CMOS process and the gap size has been limited to 1.2  $\mu$ m where self-adjusting gaps after release will create an even smaller gap as explained in chapter 3.5.

| Pros of fine-pitch                   | Cons of fine-pitch          |

|--------------------------------------|-----------------------------|

| Less parasitics                      | Excessive curling may occur |

| Lower $V_{DD}$ and power consumption | Small stack thickness       |

| Intricate routing capabilities       | Stringent CMOS design rules |

| In line with newer CMOS technology   | Delamination effects        |

Table 2.8: Pros and cons of fine-pitch CMOS-MEMS

As can be seen in Table 2.8, a comparison of coarse-grain and fine-pitch CMOS-MEMS has been demonstrated. It should be noted that the stack thickness can be roughly 5  $\mu$ m thick by including two more metal layers, making the total stack thickness comparable to coarse-grain CMOS-MEMS. The reason why this was not done was to keep the resonator thickness as homogenous as possible in order to reduce delamination and curling effects. Fine-pitch CMOS has even less parasitics compared to coarse-grain CMOS, and the power consumption is much less due to a lower  $V_{DD}$ . The foundry design rules for 90 and 65 nm CMOS are much more stringent and demanding compared to the 0.25 and 0.35  $\mu$ m CMOS processes, requiring more of the designer to be able to implement the wanted micromechanical structures. However, through the usage of Verilog-A code it is possible to make semi-automated layout design which will satisfy the foundry rules. With clever layout design and resonator architecture, fine-pitch CMOS can offer even better results than coarse-grain CMOS-MEMS.

This chapter has gone through some examples of utilizing MEMS with CMOS circuitry and described various methods of how to combine CMOS and MEMS. The chosen implementation method has been explained with examples of tentative derived design rules for fine-pitch CMOS-MEMS designs. With the implementation method being explained, the functionality and description of the resonator is described in chapter 3.

## Chapter 3

## RESONATOR MODELING

V IBRATING beams inhibits behavior of self resonating modes which produces distinct frequencies with maximum throughput, thus making it possible to use resonating beams as signal processing elements. These self resonating modes are due to a dynamic behavior of external forces which in turn generates a spring effect from the beam; a force generated internally in the beam which counteracts the external force. This spring effect results in a movement of the beam at distinct frequencies. It is possible to register this self resonating dynamic behavior of a beam if the surrounding ambient does not produce a damping which is greater than the internal spring force from the beam. A beam at a self-resonating mode will vibrate back and forth until an external or internal damping mechanism limits this vibration. Modeling of the resonator and its self resonating modes is necessary in order to build more complex MEMS resonator filters. This chapter will describe how beams can have different modes and show the model for an electromechanical equivalent description. Finally this chapter will go through some damping mechanisms, non-linear effects and a method of increasing resonator throughput by using a gap reduction technique.

#### 3.1 Mechanical beam model

By using the Euler-Bernoulli beam theory [29, 30], it is possible to find a static spring stiffness and a dynamic resonating frequency. The Euler-Bernoulli beam theory is valid for beams with a length to width ratio of 10 or more and assumes that translational and angular shear forces are small compared to the bending deformation.

$$EI\frac{d^4z}{dx^4} + \rho A\frac{d^2z}{dt^2} = 0 \tag{3.1}$$

The dynamic beam behavior is described in eq. 3.1. E is the Young's Modulus, I is the area moment of inertia,  $\rho$  is beam density and A is the cross section area. z(x,t) is the amount of bending of the beam depending on the position x throughout the beam length where the time part of z is disregarded in this analysis:

$$z(x) = C_1 \sin(\beta x) + C_2 \cos(\beta x) + C_3 \sinh(\beta x) + C_4 \cosh(\beta x)$$

(3.2)

The trial solution in eq. 3.2 is used to find solutions for the radial frequency of the beam that have different boundary conditions. The mode number  $\beta_N$  (where  $\beta_N = \beta x$ ) in eq. 3.2 is related to the radial frequency of the beam:

$$\omega_0^2 = \frac{EI}{\rho A} \beta_N^4 \tag{3.3}$$

$$f_{0,nom} = \kappa \frac{\beta_N^2}{4\pi\sqrt{3}} \sqrt{\frac{E}{\rho}} \frac{W}{L^2}$$

(3.4)

The radial frequency is related to the resonance frequency by  $\omega_0 = 2\pi f_{0,nom}$ . Eq. 3.4 is a rearranged version of eq. 3.3 where a scaling factor  $\kappa$  has been introduced to model a possible frequency shift due to topological variations of the resonator [31]. W is the resonator width and L is the resonator length. Eq. 3.4 is very important in this work as it is used to model different resonator types which will have different resonance frequencies depending on the mode number  $\beta_N$ .

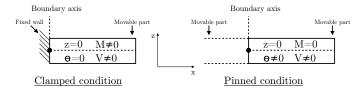

Fig. 3.1 shows two different boundary conditions. The derivative of z(x) up to three times results in the momentum M (z'(x) = M), the angle  $\theta$  ( $z''(x) = \theta$ ) or the shear force V (z'''(x) = V). The clamped condition has a boundary axis which is fixed and it has zero displacement and bending because that part can not move. The clamped condition has a momentum and shear forces. The right side of Fig. 3.1 is the pinned condition where the boundary axis is not fixed, but the circular dot in the middle is fixed, making it a fixed point. The pinned condition will not experience displacement nor momentum, but it will have a bending angle and shear forces.

Figure 3.1: Two beam boundary conditions

For beams connected at one or two ends in various ways, the two boundary conditions of Fig. 3.1 can then be used in eq. 3.2. The general characteristic equation for beam bending can be solved by using boundary conditions that are known.

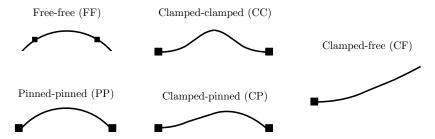

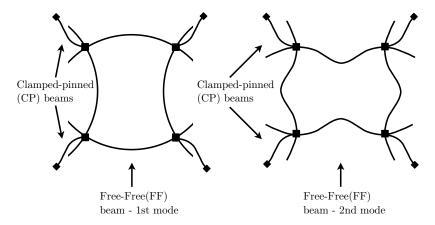

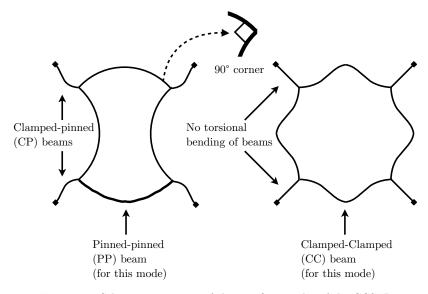

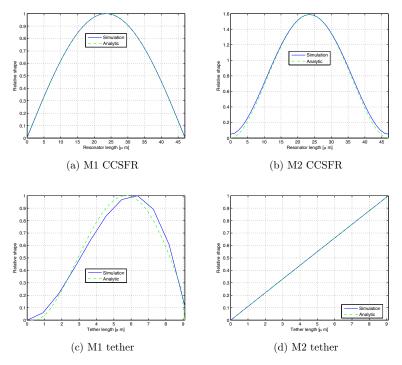

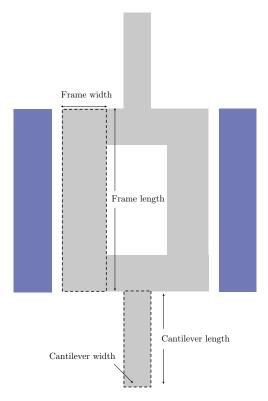

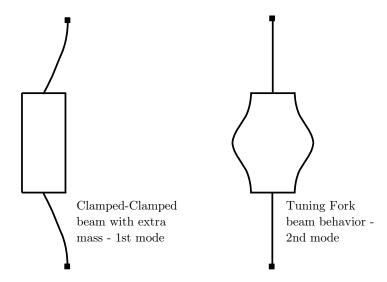

In this work, there are five different beam boundary conditions which are used as can be seen in Fig. 3.2. A Clamped-Clamped (CC) condition means that both ends will not have any angle, but the Pinned-Pinned (PP) condition shows that there will be an angle at the point where it is fixed. The Clamped-Free (CF) condition in this work is referred to as a cantilever beam. The Clamped-Pinned (CP) condition is another important beam type used in this thesis.

A final important bending condition for the beams is the Free-Free (FF) condition. This mode can in one sense be seen upon as a Pinned-Pinned mode with

Figure 3.2: The 5 different boundary conditions

additional beams attached to its end. However, the fixed points are located at strategically  $\lambda/4$  and  $3\lambda/4$  positions on the beam. This will make the free ends bend in an opposite direction as the middle part of the beam, making it vibrate back and forth as one vibrating beam. The Free-Free beam can lead to certain advantages as will be explained in chapter 3.3.

| Boundary condition   | $\beta_1$  | $\beta_2$  | $\beta_3$   |

|----------------------|------------|------------|-------------|

| Clamped-Free (CF)    | 1.875105   | 4.694091   | 7.854757    |

| Clamped-Pinned (CP)  | 3.92660231 | 7.06858275 | 10.21017612 |

| Pinned-Pinned (PP)   | $\pi$      | $2\pi$     | $3\pi$      |

| Clamped-Clamped (CC) | 4.73004074 | 7.85320462 | 10.9956079  |

| Free-Free (FF)       | 4.73004074 | 7.85320462 | 10.9956079  |

Table 3.1: 3 mode numbers for various beam clamping conditions

Finding the mode numbers for the beams presented in Fig. 3.2 is possible by using the same general beam bending movement (eq. 3.2). The mode numbers for all five beam types are shown in Table 3.1. The details on finding these mode numbers are more thoroughly explained in chapter **A** in the appendix. These five beam conditions, their mode numbers and equation 3.4 are important as they are used extensively in this work. Not all of these five beam conditions are to be used as resonators, but anchoring beams and coupling beams will be used which have mode numbers different from the actual resonator.

All of these beam types will, regardless of boundary type, have a certain static mass given by:

$$m_{static} = \rho LWH \tag{3.5}$$

where H is the thickness of the beam. A vibrating beam, however, will not have a constant mass throughout the beam length due to the fact that kinetic energy must be constant:

$$E_{k} = \frac{1}{2}mv^{2} = \frac{1}{2}\rho A \int_{0}^{L} v^{2}\left(x'\right) dx'$$

(3.6)

Because the velocity of the beam will vary depending on the location x throughout the beam length, the mass must also vary in order for the kinetic energy to

remain constant. By integrating the length L from the start of the beam to the end of the beam and dividing that by a non-integrated  $E_k$  term, it is possible to obtain the effective mass:

$$m_{eff}(x) = \frac{E_k}{\frac{1}{2}v(x)^2} = \frac{\frac{1}{2}\rho A \int_0^L v(x')^2 dx'}{\frac{1}{2}v(x)^2}$$

where the velocity is defined as

$$v^2(x) = -\omega^2 x_{mode}^2(x)$$

and where  $x_{mode}$  is a description of the deflection of the beam relative to x, and  $\omega$  is the angular velocity. As an example of this, eq. 3.7 describes the beam shape of a cantilever beam

$$x_{mode}(x) = z \cdot \gamma(\sin\beta x - \sinh\beta x + \alpha(\cosh\beta x - \cos\beta x))$$

(3.7)

where  $\gamma=0.367,~\beta=\frac{1.875}{L}$  and  $\alpha=1.362$  [26]. z is the maximum deflection that the beam experiences which will be due to electrostatic forces as described in section 3.2. For the cantilever beam, a maximum amplitude occurs for x=L. By inserting the  $x_{mode}$  equation and the velocity equation in the general effective mass equation yields:

$$m_{eff}(x) = \frac{\rho W H \int_{0}^{L} \left[ x_{mode}(x') \right]^{2} dx'}{\left[ x_{mode}(x) \right]^{2}}$$

(3.8)

The modeling of resonators with effective mass is shown in eq. 3.8 where the dynamic behavior of the beam is taken into consideration. The effective mass will be larger towards any anchored ends and have its minimum at parts of the beam which is displaced the most. For the cantilever beam, the lowest effective mass is experienced at the tip of the cantilever which is lower than the calculated static mass  $(m_{static})$ . The Free-Free, Pinned-Pinned and Clamped-Clamped beam types follow the same type of analysis to find the effective mass, each with its own  $x_{mode}$ . Most resonators used in this work has the lowest effective mass at the middle of the beam due to pinned or clamped conditions at the start and at the end of the beam. A special case occurs for the CC and FF boundary condition where their mode number (and resonance frequency) are the same, but their beam mode shape is different resulting in a slightly different effective mass.

The stiffness of the beam can be obtained through a static analysis similar to the dynamic analysis which was performed earlier in this section. However, due to the fact that effective mass is not constant throughout the beam length means that the mechanical spring stiffness,  $k_m$ , must also vary throughout the beam length:

$$\omega_0 = \sqrt{\frac{k_m}{m_{eff}}} \to k_m(x) = \omega_0^2 m_{eff}(x)$$

(3.9)

$\omega_0$  is obtained from eq. 3.3 or eq. 3.4 where  $\beta_N$  depends on the type of beam boundary condition. As with  $m_{eff}$ ,  $k_m$  will have its minimum value where maximum beam displacement occurs and  $k_m$  will be rather large towards its anchoring points.

#### 3.2 Electromechanical resonator description

The previous section described the vibrating beam as a pure mechanical device. To make the beam vibrate back and forth at various frequencies is possible by using electromagnetic, piezoelectric, magnetostrictive, electrostrictive or thermal actuation [32]. This work will use the electrostatic actuation principle due to relatively good coupling efficiency, speed and its simplicity. If the beam experiences an external force, the net force the on the beam must be zero at all times and is given by

$$F_{net} = F_{el} + F_{mech} = -\frac{\varepsilon_0 A_e V^2}{2g^2} + k(g_0 - g) = 0$$

(3.10)

where  $z=g_0-g$ . The total net force is the sum of the electrostatic force  $F_{el}$  and the mechanical force  $F_{mech}$ . The electrostatic force has an opposite sign compared to the mechanical force. The mechanical force  $F_{mech}$  is given by Hooke's law F=kz. This mechanical term opposes the electrical force which initiates displacement of the beam. The electrostatic force equation originates from potential energy equation:

$$E_p = \frac{CV^2}{2} \to F_{el} = -\frac{dE_p}{dq} = -\frac{V^2}{2} \frac{dC}{dq}$$

(3.11)

where  $C = \frac{\varepsilon_0 A_e}{g}$ . The solution in eq. 3.10 becomes unstable for a small change of the net force divided by a small change of the gap less than zero  $(dF_{net}/dg < 0)$ . This unstable area is not used for resonators but typically applied for mechanical switches which cause the beam to collapse onto the electrode. The resonator must therefore have a voltage lower than the pull-in voltage which is defined as

$$V_{pi} = \sqrt{\frac{8kg_0}{27\varepsilon_0 A_c}} \tag{3.12}$$

The pull-in voltage becomes low for a small spring stiffness, low initial gap  $(g_0)$  or large electrode area  $(A_e)$ . The resonator must be operated at voltage levels lower than  $V_{pi}$ . It should be mentioned that the analysis provided here is based on a linear Hooke's law and the parallel-plate theory, assuming that the displacement of the beam is the same throughout the beam length, something which is not necessarily the case for the different beams in this thesis. If the beam displacement is only a fraction compared to the beam length, these simple equations can be used. However, Finite Element Method (FEM) simulations must still be performed to compare with analytical calculations. If the analytical equations are too coarsegrain compared to the simulation results, expanding the resonator equations with non-linear capacitive or stiffness terms will make the results more comparable with FEM simulations. Non-linear resonator behavior is explained in section 3.4. The effective spring stiffness of the resonator is defined as k and is given by:

$$k = k_m - k_e \tag{3.13}$$

where  $k_e$  the electrical spring stiffness. The effective beam stiffness is obtained by subtracting the electrical spring stiffness from the mechanical spring stiffness [31].

Large voltage values can cause a noticeable reduction of k as  $k_e$  becomes large enough. This effect is known as spring softening due to reduction of the effective spring stiffness k in  $\omega_0^2 = \frac{k}{m_{eff}}$ . This softening of the spring stiffness may result in a non-linear behavior of the beam. It is possible for the beam to also experience a stiffening effect. Both of these effects are more described in section 3.4.

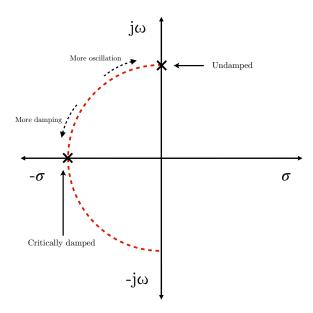

Beams that are stimulated with a sinusoidal electrostatic force has a counteracting mechanical force which opposes the electrostatic force which causes the beam to move back and forth; the beam starts oscillating. For an ideal case without any damping, the beam would vibrate back and forth infinitely. However, the real world will provide damping to these mechanical systems. Any vibrating beam with damping mechanisms will follow

$$F_{el} = m_{eff} \frac{d^2 z}{dt^2} + b \frac{dz}{dt} + kz \tag{3.14}$$

where  $F_{el}$  is the electrostatic force which initiates oscillation and b is a damping term. Eq. 3.14 shows the physical behavior for a beam opposing the electrostatic force. By using LaPlace and rearranging, this relationship can be rewritten as a function of displacement  $z(j\omega)$

$$z(j\omega) = \frac{F_{el}(j\omega)}{k} \frac{1}{1 + \frac{j\omega}{O\omega_0} - (\frac{\omega}{\omega_0})^2}$$

(3.15)

Eq. 3.15 shows the resonator displacement response as a function of frequency. If  $\omega = \omega_0$  then the  $\frac{F_{el}(j\omega)}{k}$  term becomes amplified by Q, thus enhancing the resonator displacement by the resonator Q-factor. For really large Q-factors, the displacement may become rather large:

$$z(\omega = \omega_0) = \frac{F_{el}Q}{k} \tag{3.16}$$

The resonator displacement at the first resonance mode of the beam is given in eq. 3.16. The electrostatic force  $F_{el}$  was previously stated in 3.11 but is now redefined as:

$$F_{el} = V_{ac} \frac{\varepsilon_0 A_e V_P}{q^2} \tag{3.17}$$

The  $V^2$  in eq. 3.11 has now been replaced by  $V_{ac}$  and  $V_P$ . It turns out that  $V^2 = V_{ac}^2 sin^2(\omega_0 t)$  will cause the resonator to oscillate at  $sin(2\omega_0 t)$  in addition to  $sin(\omega_0 t)$ . By using a DC polarization voltage  $(V_P)$ , the resonator will resonate at the desired frequency. For this to be possible,  $V_P$  must be orders of magnitude larger than  $V_{ac}$ .  $V_P$  will act as an amplifying term for the resonator, allowing an increase in resonator throughput.

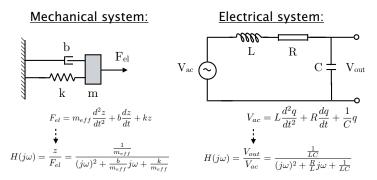

Eq. 3.14 stated that an oscillating behavior is stimulated from the electrical force  $F_{el}$ . A simple schematic of a mechanical oscillating system and its electrical equivalent is shown in Fig. 3.3. The left part of Fig. 3.3 shows  $F_{el}$  attracting a beam

mass m which has a damping factor b and coupling to an anchored wall through the beam stiffness k. The right part of Fig. 3.3 shows the electrical equivalent of the mechanical model. Analyzing the electrical schematic results in a transfer function which is comparable with the mechanical transfer function. From this comparison it can be seen that the mass is proportional to the inductor (L), the spring stiffness k is inversely proportional to the capacitor (1/C) and the damping b is proportional to the resistor (R).

Figure 3.3: Schematic comparison of a mechanical and electrical system

The LCR schematic of Fig. 3.3 is a direct conversion schematic of mechanical components to electrical ones. A more accurate schematic for the resonator is developed which takes into account a transformation between the mechanical and electrical domain. Eq. 3.17 showed that  $F_{el}$  will increase linearly with  $V_{ac}$  due to  $V_P$ . From eq. 3.17 it is now possible to define this linearized relationship:

$$F_{el} = \eta V_{ac} \text{ where } \eta = V_P \frac{dC}{dz} = V_P \frac{\varepsilon_0 A_e}{g^2}$$

(3.18)

Eq. 3.18 shows an important parameter, the electromechanical coupling coefficient  $\eta$ . The  $\eta$  is valid for small perturbations of the beam and represents the winding ratio of the schematic equivalent of the resonator. Explained in a simple manner, the  $\eta$  describes the winding ratio of a transformer, converting the electrical signal to a mechanical signal. As the vibrating beam is a mechanical device, this part of the resonator schematic is really just a mechanical response induced by an electrostatic force. Going from the resonator to an output electrode, the output from the resonator goes through a transformer with winding ratio which represents going from the mechanical energy domain to the electrical energy domain again.

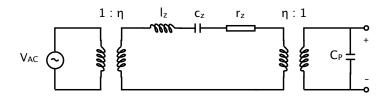

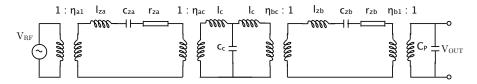

The equivalent schematic of the resonator with transformers is shown in Fig. 3.4. The resonator is described by  $l_z$ ,  $c_z$  and  $r_z$  that are assigned in lower case to specify that these are component values in the mechanical domain. Looking at the resonator from the outside of this two-port schematic, the  $l_z$ ,  $c_z$  and  $r_z$  are turned into  $L_z$ ,  $C_z$  and  $R_z$  by removing the transformers and including  $\eta$ . The upper case LCR values then represents the electrical values as seen in or out of this "black box" which represents the resonator.

Figure 3.4: Simple electromechanical resonator schematic

$$L_z = \frac{m_{eff}}{\eta^2} \tag{3.19}$$

$$C_z = \frac{\eta^2}{k} \tag{3.20}$$

$$R_z = \frac{\sqrt[\kappa]{km_{eff}}}{Q\eta^2} \tag{3.21}$$

Eq. 3.19-3.21 shows that  $L_z$ ,  $C_z$  and  $R_z$  are converted into electrical component equivalents in the electrical domain through the usage of  $\eta$ .  $R_z$  can be represented in an alternative way:

$$R_z = \frac{kg^4}{\omega_0 Q \varepsilon_0^2 A_e^2 V_P^2} \tag{3.22}$$

Eq. 3.22 shows the resonator motional impedance [31]. This is one of the most important equations when describing the performance of a resonator. This value should typically be around 50  $\Omega$ , thus matching any previous or following circuitry.

Achieving a very low  $R_z$  is possible by a low electrostatic gap g, a large electrode area  $A_e$ , a large polarization voltage  $V_P$  or a large resonator Q-factor. There is a lot of ongoing research on various methods of how to achieve a very low  $R_z$  value by different means. This could for example be tuning the process thus allowing a small gap or a large electrode area, applying a large  $V_P$  or make the MEMS resonator using a material which inhibits a very low intrinsic loss and therefore resulting in a large Q-factor. The latter example is possible by making the MEMS resonator out of a material such as diamond [33].

This work does not focus on trying to fine tune the process to achieve a very low  $R_z$  value. However, what is of focus in this work is the investigation of expanding CMOS by using MEMS to simplify signal processing. This does not mean that  $R_z$  can be designed to be huge, however it is possible to allow it to have a value in the few tenths to hundred of  $k\Omega$  (in contrast to sub  $k\Omega$  in other research literature). This is possible by having control of the following on-chip amplifier accompanying the resonator. More details on total filter description of CMOS-MEMS resonators with important performance parameters are described more throughout this thesis.

$$i_o = V_P \frac{dC}{dt} = V_P \frac{dC}{dz} \frac{dz}{dt} = \frac{\omega_0 Q \varepsilon_0^2 A_e^2}{k q^4} V_P^2 V_{ac}$$

(3.23)

Eq. 3.23 shows the resonator output motional current which arises from a time varying capacitance (dC/dt) multiplied by the polarization voltage across the gap at the output of the resonator. This term can be split into dC/dz times dz/dt where the time varying part can be replaced by  $z\omega_0$ . Alternatively, eq. 3.23 can be obtained by from eq. 3.22 and assuming that  $L_z$  and  $C_z$  are of equal value during resonance, thus canceling each other. The  $i_o$  for micromechanical resonators is typically on the orders of a few nA up to a few hundred nA.

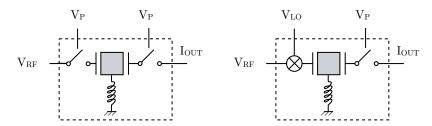

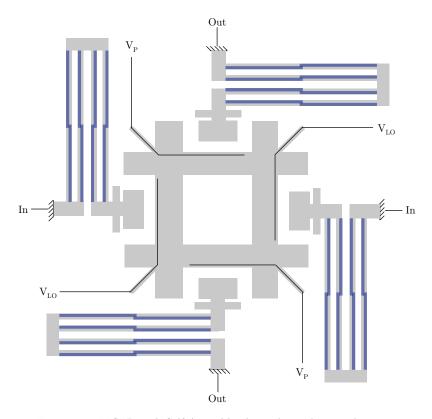

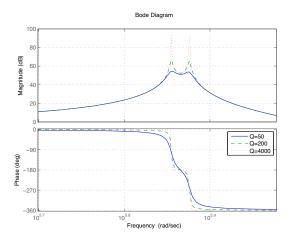

Figure 3.5: Filter and mixer-filter resonator symbol

Fig. 3.5 shows the symbol of the micromechanical component as a schematic symbol. The left part shows the symbol of a 2-port MEMS resonator filter with a spring-mass-dashpot attached to it. Internal routing of the resonator may allow different terminals inside the resonator itself, thus allowing two  $V_P$  terminals. These may be connected together or can be two different voltages, depending on the desired usage of the device. By referring to Fig. 3.4, the left  $V_P$  is the left transformer and the right  $V_P$  is the right transformer.

In the right part of Fig. 3.5, the resonator is connected as a mixer-filter. It is almost the same symbol, except that one of the  $V_P$  terminals has been replaced by a mixer symbol and a  $V_{LO}$  terminal. This allows the possible mixing of  $V_{RF}cos(\omega_{RF}t)$  with  $V_{LO}cos(\omega_{LO}t)$ . The internal routing of the resonators gives the flexibility of both doing mixing and filtering of a signal at the same time, which in transceiver architectures are typically done with two different components. Eq. 3.24 and 3.25 describes the down-mixing functionality of frequency and electrostatic forces due to the mixing of the  $V^2$  term from eq. 3.10 [34]:

$$\omega_{IF} = \omega_0 = \omega_{RF} - \omega_{LO} \tag{3.24}$$

$$F_{el,mixer-filter} = V_{RF} \frac{\varepsilon_0 A_e V_{LO}}{2q^2} cos \left( [\omega_{RF} - \omega_{LO}] t \right)$$

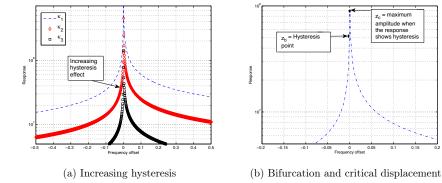

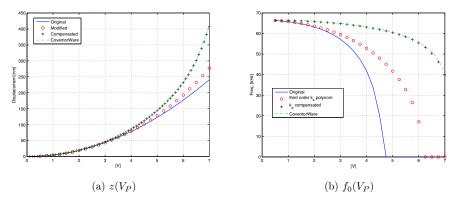

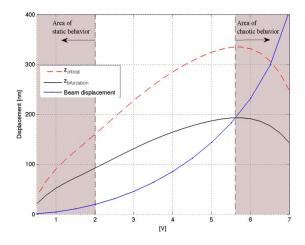

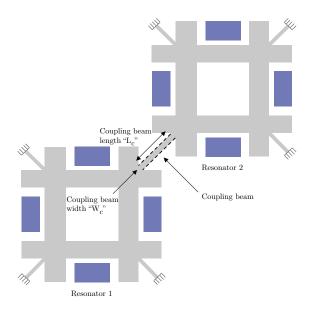

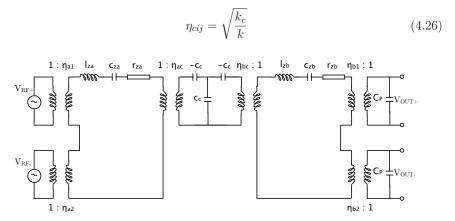

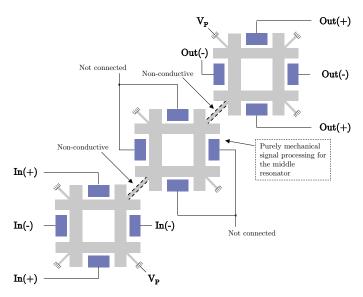

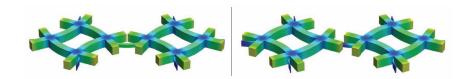

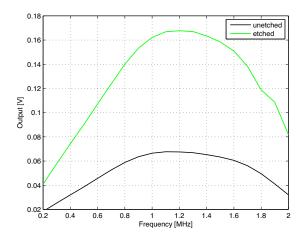

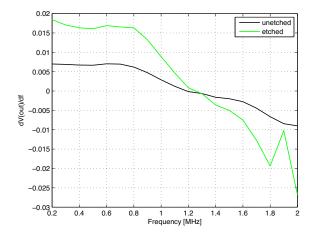

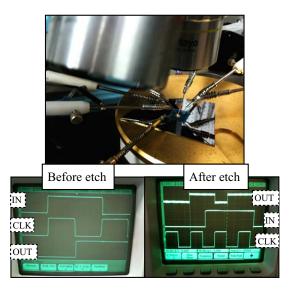

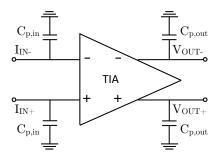

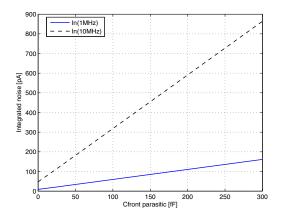

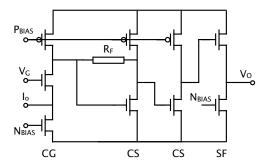

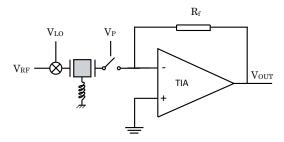

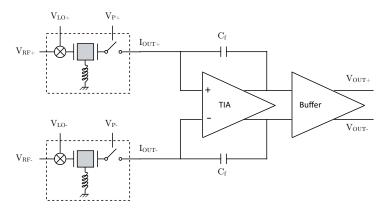

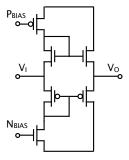

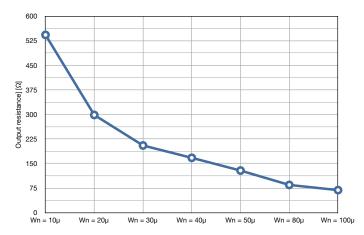

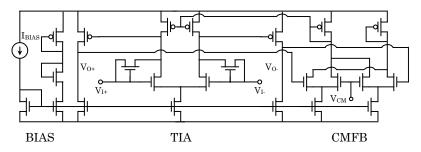

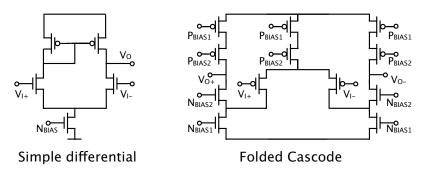

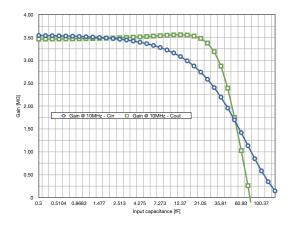

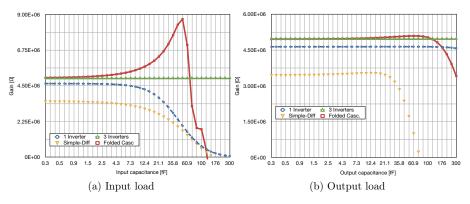

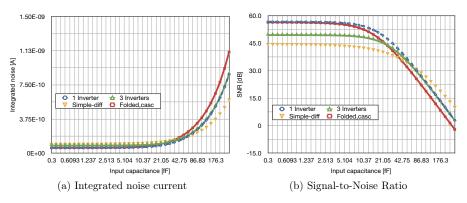

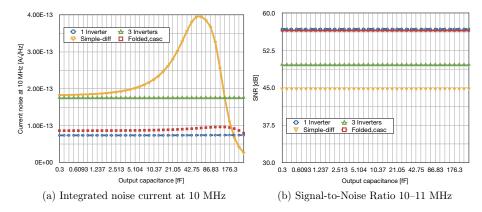

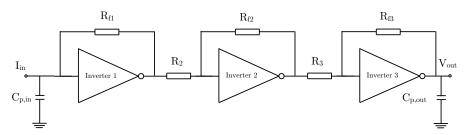

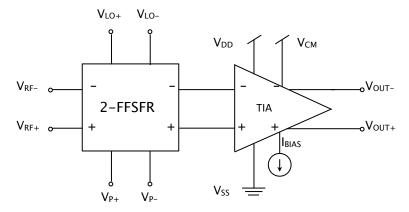

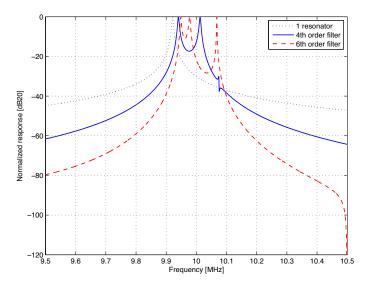

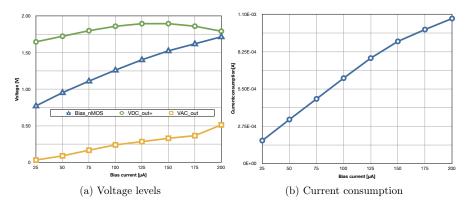

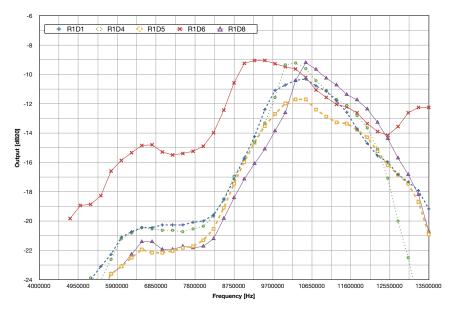

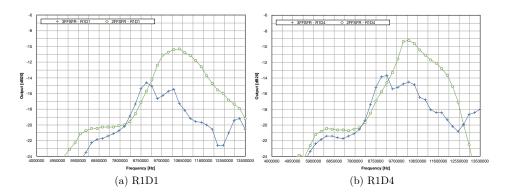

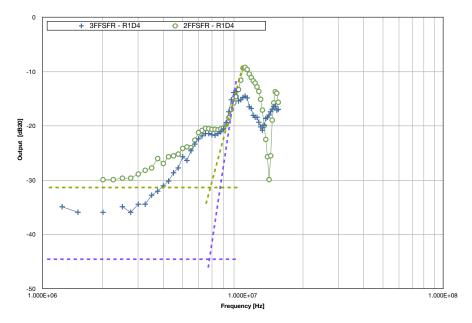

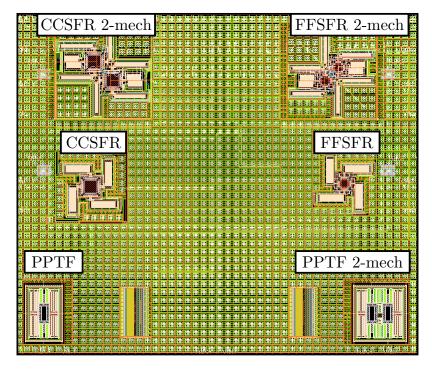

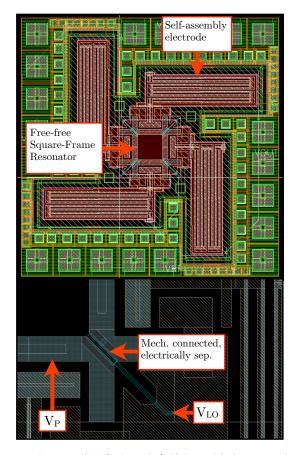

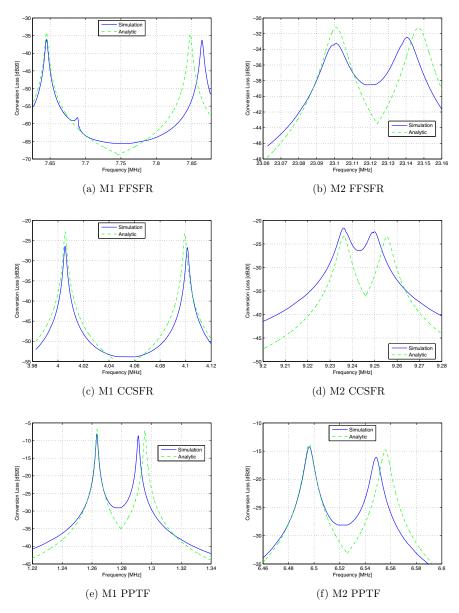

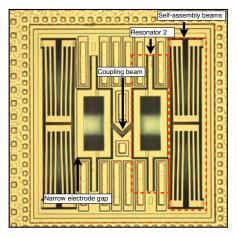

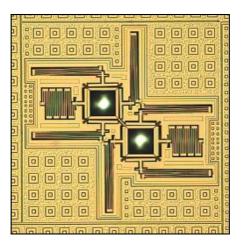

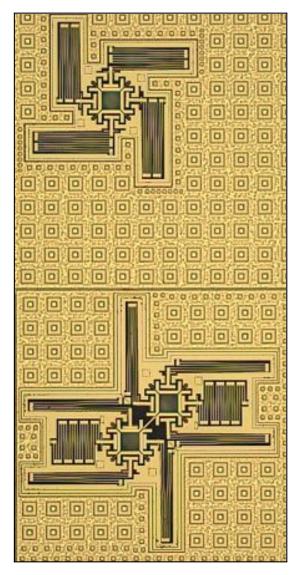

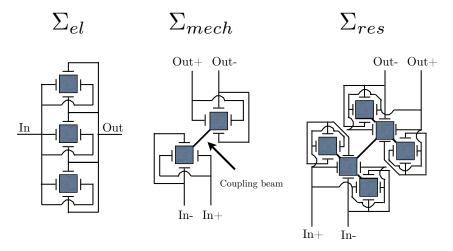

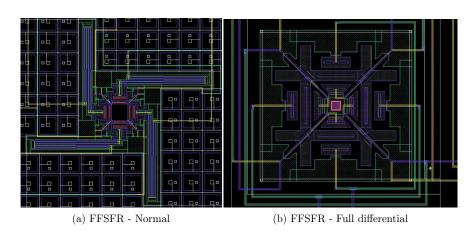

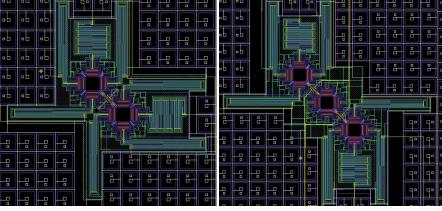

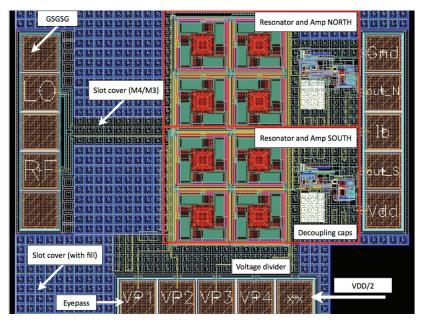

(3.25)