UNIVERSITY OF OSLO Department of Informatics

Offloading an encrypted user space file system on Graphical Processing Units

Master thesis

Magne Eimot magneei@ifi.uio.no

# **Contents**

| A | bstra | e <b>t</b>                                 | ix |

|---|-------|--------------------------------------------|----|

| A | cknov | wledgments                                 | xi |

| 1 | Intr  | oduction                                   | 1  |

|   | 1.1   | Background and Motivation                  | 1  |

|   | 1.2   | Problem Statement                          | 2  |

|   | 1.3   | Main Contributions                         | 3  |

|   | 1.4   | Outline                                    | 4  |

| 2 | Gra   | phic Processing Units Programming Examples | 5  |

|   | 2.1   | Introduction                               | 5  |

|   | 2.2   | Accelerating Reed-Solomon Coding           | 5  |

|   | 2.3   | PhysX Physics API                          | 6  |

|   | 2.4   | Seti@Home Distributed Computing            | 6  |

|   | 2.5   | Folding@Home Distributed Computing         | 7  |

|   | 2.6   | Video decoding, encoding and transcoding   | 8  |

|   | 2.7   | Mars MapReduce GPU implementation          | 8  |

|   | 2.8   | Summary                                    | 8  |

| 3 | Gra   | phic Processing Units Architectures        | 11 |

|   | 3.1   | Introduction                               | 11 |

|   | 3.2   | NVIDIA G80 Graphics Processing Unit        | 11 |

|   | 3.3   | AMD                                        | 14 |

|   | 3.4   | Intel Larrabee                             | 16 |

|   | 3.5   | Summary                                    | 18 |

| 4 | Con   | npute Unified Device Architecture          | 19 |

|   | 4.1   | Introduction                               | 19 |

|   | 42    | Programming CLIDA                          | 20 |

|   | 4.3         | The compiler                                     | 22             |

|---|-------------|--------------------------------------------------|----------------|

|   |             | 4.3.1 Compilation stages                         | 23             |

|   |             | 4.3.2 Runtime                                    | 24             |

|   | 4.4         | Performance                                      | 24             |

|   | 4.5         | Debugging                                        | 25             |

|   | 4.6         | Other technologies                               | 26             |

|   |             | 4.6.1 Shading language                           | 26             |

|   |             | 4.6.2 Stream SDK                                 | 26             |

|   |             | 4.6.3 BrookGPU                                   | 26             |

|   |             | 4.6.4 OpenCL                                     | 27             |

|   | 4.7         | GPU multitasking                                 | 27             |

|   | 4.8         | Summary                                          | 27             |

| 5 | A EC        | Emanyation on CUDA anabled CDUs                  | 29             |

| 3 | 5.1         |                                                  | 29<br>29       |

|   | 5.2         |                                                  | 30             |

|   | J.Z         | • •                                              | 31             |

|   |             | , 1                                              | 31             |

|   |             |                                                  | 32             |

|   |             |                                                  | 32             |

|   |             |                                                  | 33             |

|   |             | 9                                                | 33             |

|   |             | <del>-</del>                                     | 33             |

|   | 5.3         | -                                                | 38             |

|   | 5.5         | •                                                | 38             |

|   |             |                                                  | 39             |

|   | 5.4         | • •                                              | 40             |

|   | J. <b>4</b> |                                                  | <del>4</del> 0 |

|   |             |                                                  | 43             |

|   |             | 1                                                | 43             |

|   | 5.5         | 1 1                                              | 44             |

|   | 5.6         |                                                  | 46             |

|   | 5.7         |                                                  | 46             |

|   | J.7         | Summary                                          | 10             |

| 6 | Offl        | oading of encryption in a user space file system | 49             |

|   | 6.1         | Introduction                                     | 49             |

|   | 6.2         | Filesystem in User space                         | 50             |

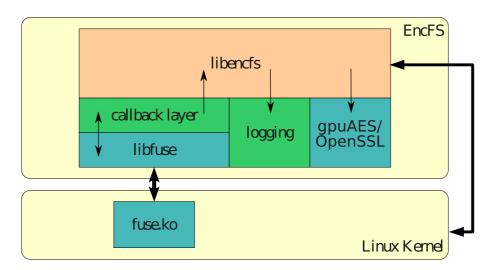

|   | 6.3         | EncFS                                            | 52             |

|    | 6.4  | Implementation                          | 54 |

|----|------|-----------------------------------------|----|

|    | 6.5  | Results                                 | 55 |

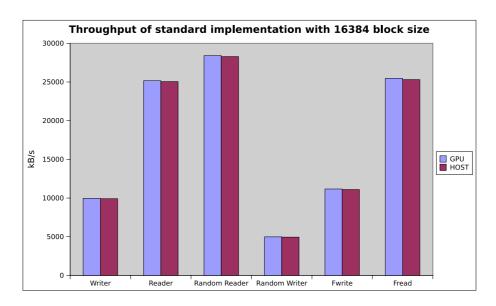

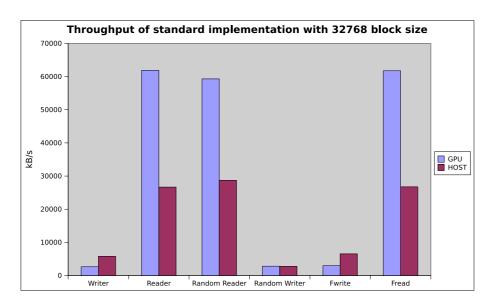

|    |      | 6.5.1 Standard implementation           | 56 |

|    |      | 6.5.2 Lookup-table based implementation | 59 |

|    | 6.6  | Discussion and lessons learned          | 61 |

|    | 6.7  | Future work                             | 63 |

|    | 6.8  | Summary                                 | 63 |

| 7  | Opt  | imizing AES with CUDA streams           | 65 |

|    | 7.1  | Introduction                            | 65 |

|    | 7.2  | CUDA Streams                            | 65 |

|    | 7.3  | Implementation                          | 68 |

|    | 7.4  | Results                                 | 68 |

|    | 7.5  | Discussion and lessons learned          | 69 |

|    | 7.6  | Future work                             | 71 |

|    | 7.7  | Summary                                 | 71 |

| 8  | Disc | cussion                                 | 73 |

|    | 8.1  | Introduction                            | 73 |

|    | 8.2  | CUDA for development                    | 73 |

|    | 8.3  | CUDA Tools                              | 74 |

|    | 8.4  | Debugging                               | 75 |

|    | 8.5  | Encryption on the GPU                   | 75 |

|    | 8.6  | Offloading a file system                | 76 |

|    | 8.7  | Streams                                 | 77 |

| 9  | Con  | clusion                                 | 79 |

|    | 9.1  | Summary and contributions               | 79 |

|    | 9.2  | Critical Assessments                    | 80 |

|    | 9.3  | Future Work                             | 80 |

| Aj | peno | dix                                     | 83 |

# **List of Figures**

| 1.1  | A NVIDIA GTX 280 Card (From NVIDIA [1])                                | 1  |

|------|------------------------------------------------------------------------|----|

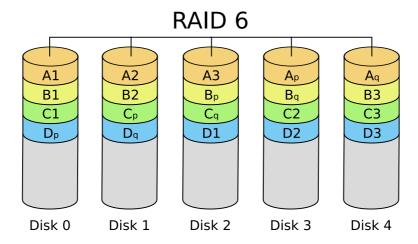

| 2.1  | Overview of RAID 6 (From Wikipedia [2])                                | 6  |

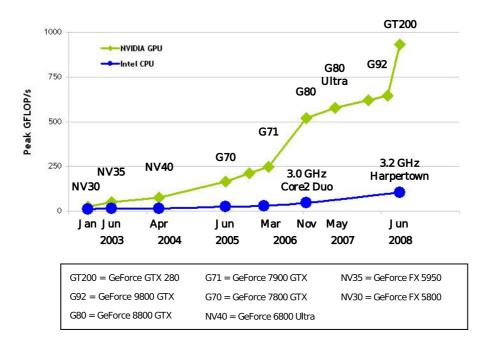

| 3.1  | Development of GPU and CPU measured in Gigaflops (From NVIDIA          |    |

|      | [3])                                                                   | 12 |

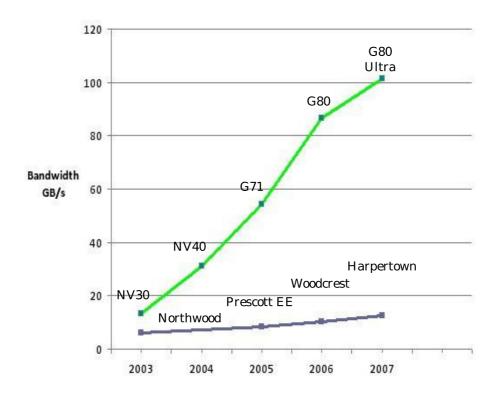

| 3.2  | Development of GPU and CPU memory bandwidth (From NVIDIA [3])          | 13 |

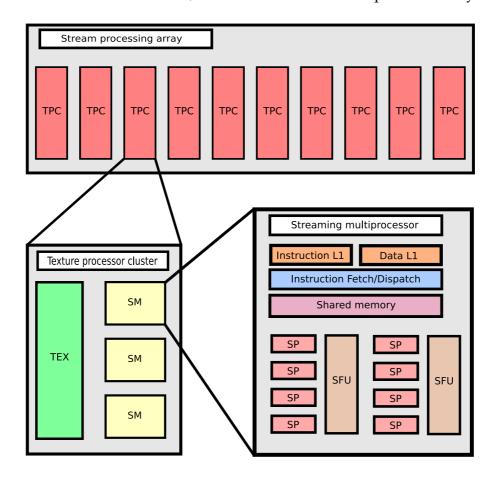

| 3.3  | Architecture of the GeForce 8 GPU                                      | 14 |

| 3.4  | AMD and NVIDIAs groups of SPs (from Anandtech [4])                     | 15 |

| 3.5  | Architecture of the Intel Larrabee Core                                | 16 |

| 3.6  | Overview of the Intel, AMD and NVIDIA cores                            | 17 |

| 3.7  | Overview of the Larrabee architecture                                  | 18 |

| 4.1  | CUDA architecture overview (From NVIDIA [5])                           | 20 |

| 4.2  | nvcc compilation flow (From NVIDIA [3])                                | 23 |

| 5.1  | The SubBytes step (From Wikipedia [6])                                 | 31 |

| 5.2  | The ShiftRows step (From Wikipedia [6])                                | 32 |

| 5.3  | The MixColumns step (From Wikipedia [6])                               | 32 |

| 5.4  | The AddRoundKey step (From Wikipedia [6])                              | 33 |

| 5.5  | ECB Encryption (From Wikipedia [7])                                    | 35 |

| 5.6  | ECB Decryption (From Wikipedia [7])                                    | 35 |

| 5.7  | Encrypted and decrypted image of Linux mascot Tux (From Wikipedia [7]) | 36 |

| 5.8  | CBC Encryption (From Wikipedia [7])                                    | 36 |

| 5.9  | CBC Decryption (From Wikipedia [7])                                    | 37 |

| 5.10 | CTR Encryption (From Wikipedia [7])                                    | 37 |

| 5.11 | CTR Decryption (From Wikipedia [7])                                    | 38 |

| 5.12 | Throughput vs number of threads (Lookup implementation)                | 42 |

| 5.13 | Throughput vs number of threads (Standard implementation)              | 42 |

| 5.14 | Throughput vs optimization (Standard implementation)                   | 44 |

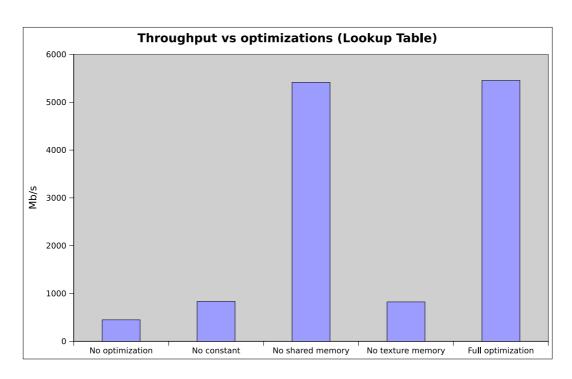

| 5.15 | Throughput vs optimization (Lookup implementation)                   | 45 |

|------|----------------------------------------------------------------------|----|

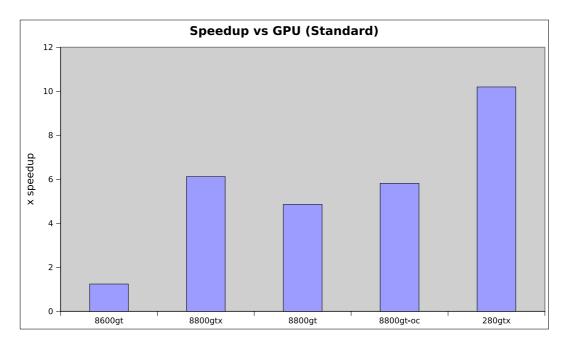

| 5.16 | Speedup vs GPU (Standard implementation)                             | 45 |

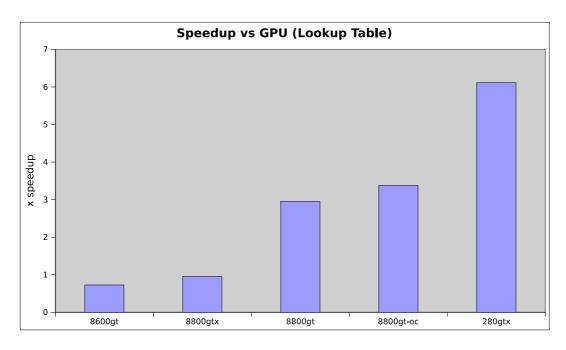

| 5.17 | Speedup vs GPU (Lookup implementation)                               | 46 |

| 6.1  | Implementation of readdir function                                   | 52 |

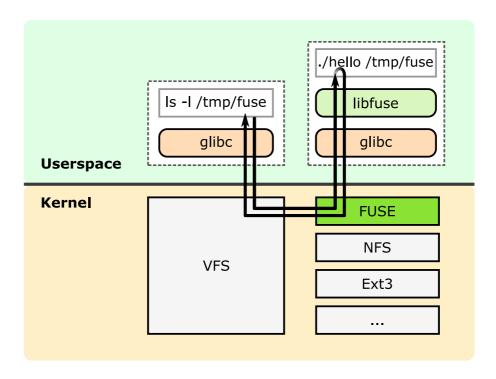

| 6.2  | FUSE structure image (From Wikipedia [8])                            | 53 |

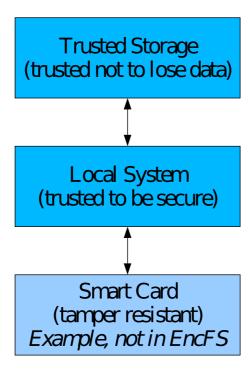

| 6.3  | Separation of trust with encrypted file systems (From EncFS [9])     | 53 |

| 6.4  | EncFS structure image (From EncFS [9])                               | 54 |

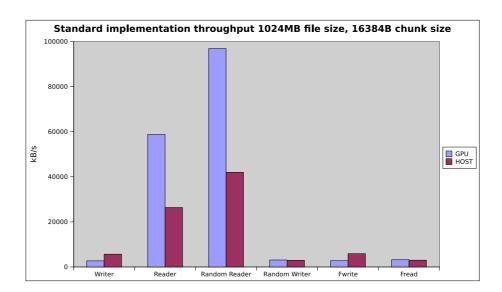

| 6.5  | EncFS standard implementation throughput (16384)                     | 57 |

| 6.6  | EncFS standard implementation throughput (32768)                     | 57 |

| 6.7  | EncFS standard implementation throughput (65536)                     | 58 |

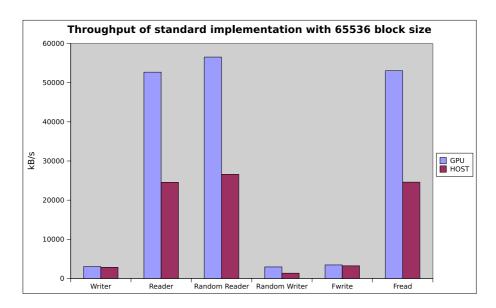

| 6.8  | EncFS standard implementation throughput (81920)                     | 59 |

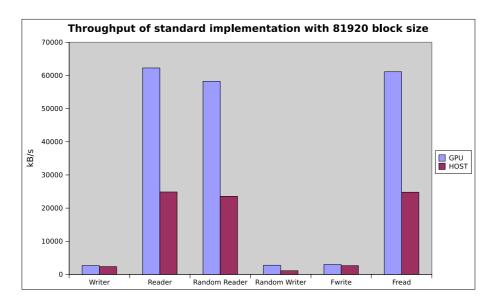

| 6.9  | EncFS GPU throughput                                                 | 59 |

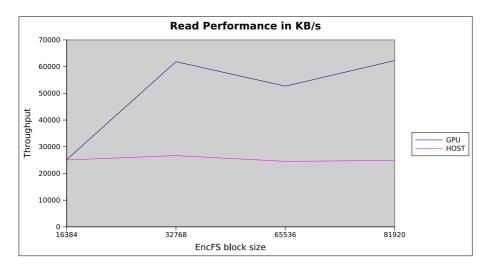

| 6.10 | EncFS standard implementation throughput for small files with 32768B |    |

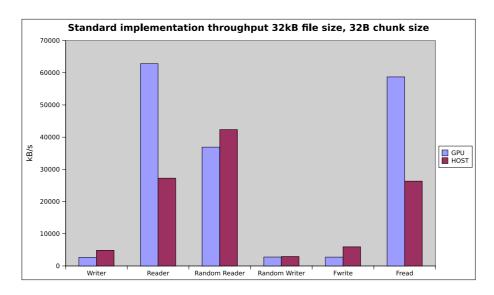

|      | EncFS block size                                                     | 60 |

| 6.11 | EncFS standard implementation throughput for large files with 32768B |    |

|      | EncFS block size                                                     | 61 |

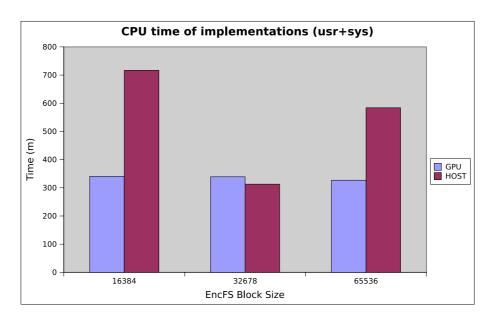

| 6.12 | EncFS standard implementation CPU time                               | 62 |

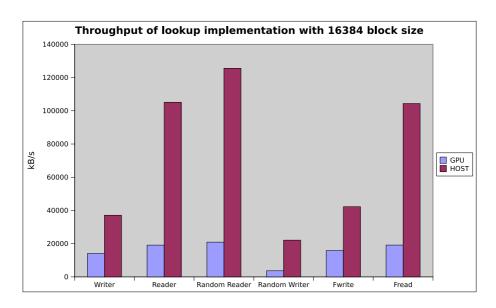

| 6.13 | EncFS lookup implementation throughput (16384)                       | 63 |

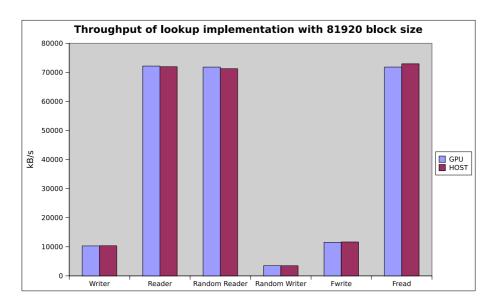

| 6.14 | EncFS lookup implementation throughput (81920)                       | 64 |

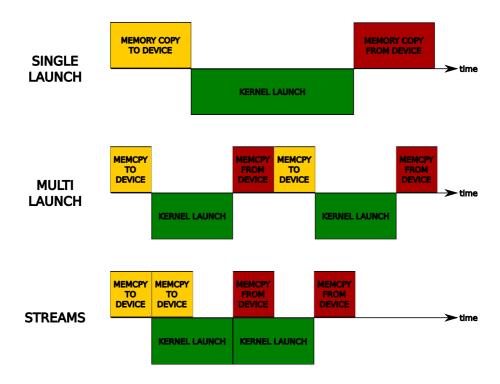

| 7.1  | Overlapping memory copy and computation, under optimal condition .   | 67 |

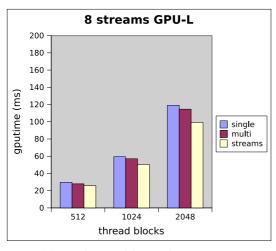

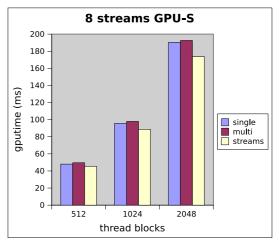

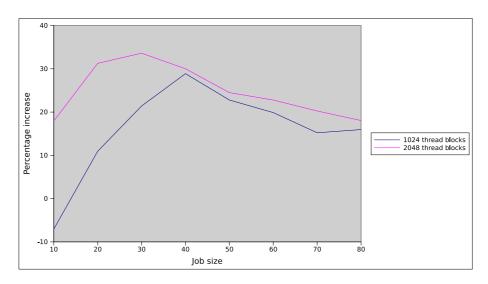

| 7.2  | Streams GPU                                                          | 69 |

| 7.3  | Job completion ratio on stream implementation                        | 69 |

# **List of Tables**

| 2.1 | Current performance numbers, taken from Stanford University [10]                                                                                               | 7  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Number of GPU Processing Cores (From NVIDIA [11])                                                                                                              | 13 |

| 4.1 | nvcc supported files (From NVIDIA [12])                                                                                                                        | 22 |

|     | Number of rounds given key size                                                                                                                                |    |

|     | User and System time of EncFS standard implementation                                                                                                          |    |

| 7.1 | The average increase in speedup of the kernels running 512, 1024 and 2056 thread blocks compared with different number of streams compared to a single launch. | 70 |

## **Abstract**

Modern computers often have a powerful graphics processing unit (GPU), either on dedicated graphic cards or integrated on the motherboard. These units can used by applications for demanding computation. Another use of this technology is to assist the main CPU in the system, offloading some of its work. Offloading can give increased performance, as well as decreased load on the main CPU. Decreasing the load frees resources for other applications.

Keeping documents, images and other potentially sensitive files private is important for many users. One way to do this is to use an encrypted file system, which can prevent others from gaining unauthorized access. However, such a file system occupies resources in the computer system. In this thesis, we evaluate how GPUs can be used for assisting the computationally expensive encryption part of an encrypted file system.

Programming GPUs, is challenging because of the GPUs massively parallel nature and their many memory types. We will look into different architectures, focusing mainly on NVIDIAs architecture and programming framework in our work on evaluating the effects of using graphic processing units for offloading an encrypted file system. In this thesis, we see that offloading parts of this file system is beneficial, giving better performance and reduced CPU load.

# Acknowledgments

I would like to thank my advisors, Håkon Kvale Stensland, Pål Halvorsen and Carsten Griwodz. Their feedback and assistance have been inspiring, and this thesis would not have been possible without them. I would also like to thank Håvard Espeland and Paul Beskow for valuable feedback.

I would also like to thank Alexander Ottesen, which I have worked with for some of this thesis. His help has been invaluable and his hard-working attitude has been inspiring.

Writing this thesis at Simula Research Laboratory has been great, I would like to thank the whole lab for a great social and academic environment.

Also, I would like to thank my friends and family, which have been of great support through this thesis.

Oslo, May 3, 2009

Magne Eimot

# Chapter 1

## Introduction

## 1.1 Background and Motivation

Modern GPUs from NVIDIA, Intel and AMD have over the years evolved into highly programmable processing units, that can be used for other purposes in addition to rendering graphics. We will investigate some of the possibilities these architectures give us, with an emphasis on the NVIDIA architecture and programming method. An example of an NVIDIA Graphics Card is seen in figure 1.1.

Figure 1.1: A NVIDIA GTX 280 Card (From NVIDIA [1])

Security is an important aspect in todays society, and protecting ones data is important. For a computer to be protected against someone gaining unauthorized access,

an important attack vector is the local storage of a computer. The most common way to prevent these attacks is to use data encryption to render the content of the storage medium useless, unless the correct authentication token can be provided. This token is commonly a pass phrase, which can be combined with a physical token like a smart card. Having a encrypted local storage, requires an encrypted file system. In such a file system, the data encryption is compute intensive. In addition to require good performance from the encrypted storage, it is desirable not to occupy too much of the CPU time of the system, because the computer will generally be used for other tasks in addition to the encryption required to secure data.

Utilizing the GPU, which is present in many modern computer systems for the encryption and decryption, process is interesting to investigate; both in terms of performance and to make CPU resources available for other applications in the system. When we discuss offloading in this thesis, both of these aspects will be considered.

In the CPU market, there is no longer a race for higher clock frequencies of the processors. Generally, increasing the clock frequency also increases the power consumption, and therefore the heat in the processors. For example, a Pentium IV processor has the power density (*Watts/cm*<sup>2</sup>) of a hot plate. To increase performance, the new generation of processors now have multiple cores, which means that developers need to focus on parallel programming. This phenomena is often called the *Power wall*, because there is a limit to the clock frequency a processor can have. For the computation power to increase, more cores have to be added. GPUs on the other hand have lower clock frequencies, and a much higher number of cores, and we want to investigate how and if these devices can be used on tasks previously done by CPUs.

Using GPU which is often available in modern computer systems to assist in the encryption process of a file system is therefore interesting, considering the GPUs good performance. Previous research have been successful in offloading tasks to a GPU, e.g. the Reed Solomon encoding done by Curry et al. [16], where a RAID solution was offloaded using a GPU.

#### 1.2 Problem Statement

GPGPU is an area of research where there are unknown factors regarding the usage. Parallelizing applications for running on GPU is challenging, as there are limited debugging available, and the massively parallel architecture of the GPUs.

Adapting existing applications to run on GPU is one way to use the GPUs, as an alternative to writing the applications from scratch to suit the GPUs. To adapt the applications, requires that one finds the computationally demanding parts of the application. The problem must then be analyzed too see if it is possible to map the problem to suit a GPU. Most applications were never intended to run on GPU, and porting them to GPU is therefore challenging.

One field where little work has been done, is file systems. Some of these have advanced features like data encryption, or built in redundancy. They are traditionally written to run on ordinary CPUs, which could possibly be better used for other applications.

In this thesis we want to evaluate the benefits of offloading the encryption part of a file system to the GPU.

#### 1.3 Main Contributions

This thesis evaluates GPU offloading of the encrypted file system EncFS. We divide the job of offloading an application into several parts, looking at the GPU kernel, the whole application, and optimization of the application. We investigate and run experiments on each part to get a better understanding of running an application on the GPU.

We will look into how the popular *Advanced Encryption Standard (AES)* algorithm work. Following this, we two create GPU implementations of AES, based on different CPU implementations, and evaluate their properties. These implementations will form a basis for offloading the encryption part in a user space file system, where we will integrate these implementations, and investigate their effects.

In this thesis, we evaluate the performance of some different AES encryption implementations. We look into different optimization techniques, and show how memory accesses can be done more optimal. We show that an lookup based encryption implementation can run even faster on GPU, and that a naive encryption implementation can have a even higher relative increase in performance.

This is followed by an investigation in how the CUDA framework can be used for porting an encryption application to the GPU, what type of applications are best suited, and what happens to the execution time of two different implementations of an encryption algorithm. We also look into the encrypted user space file system, and evaluate what offloading effects we can achieve if we use the GPU to run the encryption algorithm, instead of running it on the CPU.

Finally, we investigate a method for increasing application performance by allowing overlap between GPU computation and memory copying, called CUDA streams. We show how using CUDA streams can give a reduction in execution time.

#### 1.4 Outline

In chapter 2, we look into different possibilities for programming modern GPUs. This is followed by introduction to the different architectures of modern GPUs in chapter 3. We further investigate one of the frameworks mentioned, namely the CUDA framework in chapter 4, and see what possibilities this gives us. In chapter 5, we investigate how a encryption application can be ported and ran on the GPU, how we best use the GPU, and compare it to a CPU based implementation. This is followed by chapter 6 where we investigate the offloading of encryption in a user space file system. We will then look into CUDA streams in chapter 7, followed by a discussion in chapter 8, and a conclusion of our work in chapter 9.

# **Chapter 2**

# **Graphic Processing Units Programming Examples**

#### 2.1 Introduction

General-purpose computing on graphics processing units (GPGPU) is the technique of using a GPU not for graphics but for solving general computer problems with the hardware available on the GPU. In this chapter, we look into some example of what GPUs are used for, like accelerating RAID solutions, physics simulations, Folding@Home and video coding.

The purpose of this chapter is to get a introduction into what kind of tasks can benefit from GPU assistance, before we continue exploring one framework for programming a GPU and look closer into one use case for GPUs.

## 2.2 Accelerating Reed-Solomon Coding

Reed-Solomon is an error-correcting code, which is used in many applications, like CDs and DVDs, data transmission and for providing data redundancy. Redundant Array Of Inexpensive Disks 6 (RAID6) is a data redundancy technique which gives n-2 hard disks of capacity, given n hard disks. The structure of a RAID 6 is seen in figure 2.1, where the numbered blocks are data chunks, and the blocks called p and q are parity blocks. It can sustain data integrity when up to two of the hard drives fail. The Reed-Solomon coding required to store this redundancy is compute intensive, and we therefore look into a GPU assisted implementation of RAID6.

Figure 2.1: Overview of RAID 6 (From Wikipedia [2])

Curry et al. have investigated how a GPU can be used for computationally intensive RAID solutions, where you have 2 or more parity disks [16]. They found that a GPU would handle much larger data throughput, in some cases 5 times the throughput of a Intel Core 2 Quad 6600. They also found that because of all the bus transfer of data, the solution would be most effective if incoming data were written to a buffer, and that the write operation would seem for the application to be completed, then done in the background by the GPU. If it would be checksummed while the write-operation had not yet returned, it would cause a greater latency than when used with the CPU.

#### 2.3 PhysX Physics API

Another application is the PhysX Physics API [17] for games. PhysX was a solution created by Ageia which created a hardware-accelerated solution for games, where physics heavy computing could be offloaded. This computation allowed more advanced and realistic game performance. NVIDIA acquired Ageia, and they have ported PhysX to work on their CUDA enabled GPUs. PhysX is designed for vector calculations and trajectories of large quantities of physical objects, that this is a type of calculation well suited for a GPU.

## 2.4 Seti@Home Distributed Computing

Seti@Home [18] is a distributed computing project, where the goal is to detect intelligent life outside Earth. The project analyzes large data sets from radio receivers, and

| OS Type          | Current TFLOPS <sup>a</sup> | Active CPUs | Total CPUs |

|------------------|-----------------------------|-------------|------------|

| Windows          | 200                         | 210098      | 2104468    |

| Mac OS X/PowerPC | 7                           | 8200        | 117721     |

| Mac OS X/Intel   | 28                          | 8928        | 55312      |

| Linux            | 70                          | 40917       | 320755     |

| GPU              | 921                         | 8370        | 20669      |

| PLAYSTATION®3    | 1347                        | 47757       | 568013     |

| Total            | 2573                        | 324270      | 3186938    |

Table 2.1: Current performance numbers, taken from Stanford University [10]

have ported their client to support GPUs from NVIDIA.

## 2.5 Folding@Home Distributed Computing

Folding@Home [19] is another distributed computing project, performing CPU-intensive simulations on protein folding. The project allows users to run a client on their computer, which will download jobs from a central server, do simulations on the data, and upload the data back to the server. The purpose of this research is to better understand diseases, like Alzheimer's disease, Parkinson's etc. The distributed computing allows researchers to get access to more processing power than they could get by running it on their own hardware.

In October 2006, a Folding@Home client for the Microsoft Windows XP operating system was released, which included support for running the simulations on the ATI R520 family of GPUs. After 9 days, the project had received 31 teraFLOPS of computational performance, which averaged 70 times the performance of CPU based simulations on the project [20], the current performance numbers shown in table 2.1. Recently a client that supports NVIDIAs GPUs has been released, which have further increased the computational power available from GPUs. Now the GPUs have 4 times the computing power of CPUs, even though there are ten times as many CPU-oriented clients.

The project also supports PlayStation 3 (PS3), which are based on the Cell Broadband Engine Architecture (CBEA) [21].

The current performance numbers of the various clients in the Folding@Home project are shown in table 2.1.

<sup>&</sup>lt;sup>a</sup>TFLOPS are actual performance numbers, not theoretic peak

#### 2.6 Video decoding, encoding and transcoding

Another application for GPUs can be to offload some of the calculations needed for decoding video frames. Wesley et al. have investigated the performance gains available when offloading some of the calculations to the GPU. They have implemented a pixel-shader based approach to decoding video frames and have shown that this was about twice as fast on a GPU than on a CPU [22]. This was with respectively a non CUDA-enabled NVIDIA GeForce 6800 GPU and a AMD Athlon XP 2800+ CPU.

Elemental Technologies, Inc. has an application called Badaboom Media Converter [23], which is an application for transcoding and encoding video and audio files, that of-floads some of the process to the GPU.

## 2.7 Mars MapReduce GPU implementation

MapReduce [24] is a software framework designed to support distributed computing on large data sets. It was inspired by the map and reduce functions used in functional programming, and requires that your problem can be written in this form.

- The Map step takes input, divides it into smaller problems, and distributes it to worker nodes (which the worker node might do again).

- The worker nodes then solve the problem, and returns the answer back.

- The Reduce step assembles the answers in the correct order, to yield the correct result.

He et All found that implementing MapReduce on a GPU in what they called the Mars framework could be up to 16 times faster than its CPU based counter part for some common web applications [25].

#### 2.8 Summary

In this chapter we have investigated some of the possible applications for using a GPU. We have seen that many different compute intensive applications have benefited from using a GPU. Therefore we want to look further into how a GPU is designed, by looking into the hardware and structure of some different GPU architectures from NVIDIA,

Intel and AMD, where we get a understanding of how these architectures can provide a platform for high performance applications.

# **Chapter 3**

# **Graphic Processing Units Architectures**

#### 3.1 Introduction

NVIDIA, Intel and AMD all make or develop programmable GPUs. To understand the differences between programming them, we first look at their architectures to provide background on how they work and what sets them apart.

## 3.2 NVIDIA G80 Graphics Processing Unit

On November 8, 2006 NVIDIA released a new family of graphics cards based on the *G80* architecture [26]. In the NVIDIA G80 architecture shown in figure 3.3 we find a Stream Processor Array (SPA). There are multiple SPAs on each chip. Each SPA consists of Texture Processor Clusters (TPC). A TPC consists of two Streaming Multiprocessors (SM), a group of processors which can run threads. The TPC also contains one texturing unit which is not as relevant in the context of GPU programming, because we mostly use the SMs.

The SMs can access four different types of memory. The memory types accessible are one set of 32-bit registers, a shared memory, a read-only constant cache and a read-only texture cache. There are also uncached local and global memory spaces, that are implemented as read-write regions of the memory of each device. Each SM appears as eight streaming processors (SP) which are scalar ALUs able to run a single CUDA thread. The SM runs several threads in parallel with low overhead. The low thread scheduling overhead means that one can use more threads than one uses in traditional

CPU programming. To get optimal performance from the GPU, more threads than ALUs are required, the reason for this will be explained further in section 4.3.2.

Figure 3.1: Development of GPU and CPU measured in Gigaflops (From NVIDIA [3])

Some of the different architectures from NVIDIAs, has their performance in GFlops (billion floating operations per second) displayed in figure 3.1. Performance measured in GFlops have not increased fast on modern Intel CPUs in the years from 2003 to 2008. On the GPUs, however, we can see a much faster increase. This gives some indication of the potential of a modern GPU compared to traditional CPU. It is important to notice that these performance numbers concerns only floating point operations, which is not the most relevant for all types of applications. However, floating point operations are common in scientific calculations that require a lot of computing power.

The memory bandwidth of NVIDIA GPUs has increased much faster than the memory bandwidth has increased for modern x86 CPUs, seen in figure 3.2. In 2003, the NV30 chipset from NVIDIA did not have that much higher bandwidth than the Intel "Northwood" processor. However, we see that the bandwidth has not increased much in the years up to 2007 for the x86 CPUs, compared to the very high increase for the NVIDIA chipsets, where the G80 Ultra has a memory bandwidth of up to 100GB/s.

These two performance metrics give some indication of the potential of the GPU to fulfil certain tasks. Especially, data-intensive floating point operations benefit from using the GPU.

The GeForce 8800 GTX has eight TPCs, with a total of 128 SPs, each TPC with 1024

Figure 3.2: Development of GPU and CPU memory bandwidth (From NVIDIA [3])

| Chip                   | TPCs | SMs per TPC | SPs per SM | Total SPs |

|------------------------|------|-------------|------------|-----------|

| GeForce 8 and 9 Series | 8    | 2           | 8          | 128       |

| GeForce GTX 200        | 10   | 3           | 8          | 240       |

Table 3.1: Number of GPU Processing Cores (From NVIDIA [11])

32-bit registers. Figure 3.3. shows one of SPAs, which consists of 8 TPCs, each TPC has 16KB of shared cache between the SPs. This is shown in figure 3.3, a NVIDIA GeForce 8 GPU. For optimal performance, programs should follow the same code path in each SM, otherwise the programs will be run in sequence, instead of in parallel. Stream processors are somewhat similar to vector processors, but can reduce bandwidth demands on the memory system, and can thus support an order of magnitude more ALUs with the same memory bandwidth [27]. Table 3.1 shows some of the specifications of the newest NVIDIA GPUs.

The NVIDIA GeForce architecture is called Single Instruction Multiple Thread (SIMT), meaning that one instruction gets executed by multiple threads, in the TPC. Threads are organized in *warps*, which are groups of 32 threads. The SIMT processor manages the threads in a warp, and warps are batch scheduled. In a warp, all threads have the same starting point in the code, but can branch freely. The fastest execution is achieved when all threads in the warp agree on a code path. This means branching have a high cost, unless you get all threads in a warp to take the same branch.

The SM will, given a set of threads to run, divide these into warps, and schedule them for execution. For each instruction, the SM will choose a warp that is ready.

Figure 3.3: Architecture of the GeForce 8 GPU

#### 3.3 **AMD**

AMD produces graphics chipsets under the ATI brand. Radeon R770 (code named RV770) [28] is AMD's name for the latest generation of graphics chipset which is used in modern ATI products, like the ATI Radeon HD 4800. This chipset contains 800 streaming processors, which is an increase from the previous 320 cores found in the ATI HD 3800 card [29], that was based on the RV600 architecture. These units are divided into groups of 10 SIMD cores.

The RV770 architecture features a 256-bit memory controller, and was the first GPU to support GDDR5 memory, running at 900 MHz. This memory achieves a bandwidth of up to 115 GB/s. ATI previously used a ring bus like the Intel Larrabee architecture, that has been replaced for a combination of a crossbar and an internal hub in the RV770

architecture, see chapter 3.4.

AMD's Streaming Processor, seen in figure 3.6, consists of Stream Processing Units (SPU), that resemble NVIDIAs SP. The SPU consists of five units, called x,y,z,w and t. x,y,z,w are ordinary ALUs, and t is a transcendental unit, which can do all the operations of x,y,z,w and also transcendental operations. This means that unlike the SPs on NVIDIA cores, the AMD core can run five instructions simultaneously, giving the possibility for Instruction Level Parallelism (ILP), not only Thread Level Parallelism (TLP) as NVIDIA supports, because each of the NVIDIA cores can do only one instruction at the time.

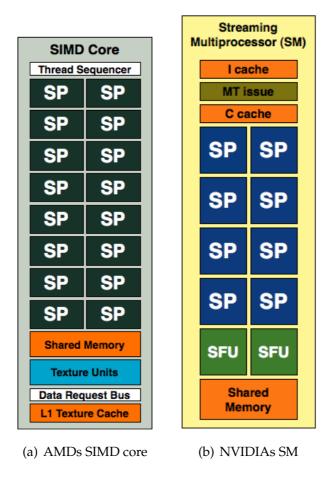

Figure 3.4: AMD and NVIDIAs groups of SPs (from Anandtech [4])

AMD group their SPs into a *SIMD core*, which is somewhat similar to the SMs in the NVIDIA architecture, shown in figure 3.4. There are, however, some differences worth noting. There are more SPs in AMDs SIMD Core, two times as many, and these SPs can do ILP. A difference between the AMD and NVIDIA cores is that there is no constant and instruction cache located in AMDs SIMD core, it is shared between SIMD cores. NVIDIA has no texture cache in its SM, which AMD has on the SIMD core.

#### 3.4 Intel Larrabee

Intel is developing their own hybrid GPU technology, called Larrabee [30]. This design differs from the NVIDIA and ATI GPUs in that it will support the x86 instruction set, including EMT64.

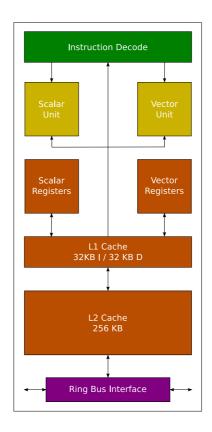

Figure 3.5: Architecture of the Intel Larrabee Core

Intel's Larrabee architecture is based on the Intel Pentium core. In order to increase the number of possible cores on a single die, the Larrabee core is based on a 45nm process, instead of the original 600 nm  $(0.60\mu\text{m})$  which was used for the Pentium. The Larrabee cores can run 4 threads of execution, where each thread has its own set of registers, unlike the original Pentium, which did not support Simultaneously Multithreading (SMT). It can execute 2 instructions per cycle, and has a pipeline depth of 5 stages. The Larrabee core also features a larger cache than the original Pentium, a total of 64KB L1 cache, split equally between Instruction and Data (32KB for each), where the Pentium had 8KB, and 256KB L2 cache, whereas the Pentium relied on a optional external cache on the motherboard. An overview of the Larrabee Core is shown in figure 3.5. The biggest change from the original Pentium core is that the new Larrabee core has a SIMD unit. A Larrabee core vector ALU is 16 data elements wide, whereas the original Pentium architecture did not have any SIMD unit, except for the later Pentium

revisions which supported MMX instruction set [31].

Larrabee does not have as many cores as the NVIDIA and AMD Streaming Processors architectures, so it relies on its wide vector ALU and high number of registers to yield high performance. Initial versions of Larrabee are estimated to have between 8 and 16 cores [32].

Larrabee will not be a GPU in the traditional sense, but rather a set of x86 compatible cores that can also be used for general purpose programming. However, Intel will make DirectX and OpenGL front-ends for Larrabee, to enable it to work like a GPU.

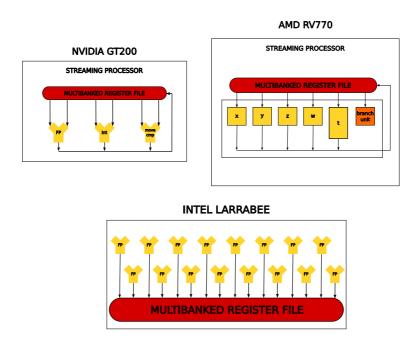

Figure 3.6: Overview of the Intel, AMD and NVIDIA cores

An overview of the Intel, AMD and NVIDIA SIMD architectures is given in figure 3.6, showing the different architectures. The AMD and NVIDIA cores look more similar the the Larrabee. However, they will differ widely in instruction set and other properties. The NVIDIA SP can process a single operation at the time. AMDs SIMD core can process five. Intels core can process sixteen. AMD already have challenges scheduling five operations at the time, a lot of compiler help is needed to use the core efficiently, so we might see some challenges for Intel utilizing the vector ALU to its full capacity.

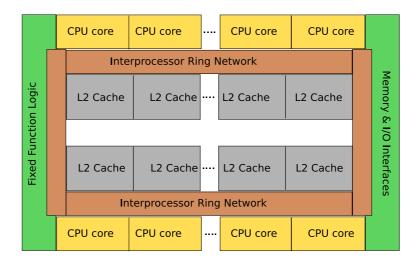

Intel's Larrabee Cores will be connected by a ring bus architecture. The large amount of cache available on the Larrabee cores is expected to be one of Larrabees strengths, as each Larrabee core has four times the L1 cache of the original Pentium. The reason for this is that the core can work on four times the number of threads as the Pentium. The Larrabee cores will each have 256KB L2 cache. These caches on the Larrabee are fully

Figure 3.7: Overview of the Larrabee architecture

coherent. Communication between the L2 caches is handled by the ring bus architecture seen in figure 3.7. If a core cannot find the desired data in its L2 cache, a request will be placed on the ring bus, and if one of the other cores L2 cache has it, it will be transferred back to the correct cache.

Even though the Larrabee architecture support the x86 instruction set, several features from the Intel Core 2 architecture are not supported. The Larrabee architecture will not support out-of-order execution and branch prediction. It does, however, have a larger number of cores, which will mean that a different programming model must be used to yield good performance. This might result in some of the same challenges that we encounter while programming the NVIDIA and ATI GPUs, explained further in chapter 4.

## 3.5 Summary

In this chapter, we have looked into some of the different GPU architectures that are or soon will be available. We have seen that the GPUs hardware will give great possibilities for programming and porting applications to the GPUs to give increased performance than running on the CPU. One of the most important differences between the architectures is the vectorization required to efficiently use the hardware. We will look into how GPU is programmed, by looking at one of the frameworks available for programming GPUs, NVIDIAs CUDA framework in the next chapter, in order to give us the possibility of investigating further how an application is ported to run on the GPU. We will also briefly discuss alternatives to NVIDIAs CUDA framework.

# Chapter 4

# **Compute Unified Device Architecture**

#### 4.1 Introduction

We have chosen to further investigate the NVIDIA GPUs, because it has shown good potential, and we have seen many example applications that use NVIDIAs GPUs. In this chapter we investigate which possibilities the NVIDIA Compute Unified Device Architecture (CUDA) [33] gives us.

Of the three architectures we looked into in chapter 3 we choose to investigate the NVIDIA GPUs and therefore the CUDA framework, because of the easy access to documentation, and a programming model which was not to complicated to comprehend. We felt that other architectures were not as well documented, nor as widely used as the NVIDIA architecture. This chapter will focus on the NVIDIA programming model, however, we will also look into some other programming models for GPUs. The NVIDIA programming model was the only mature GPGPU framework available for our platform when we started this thesis.

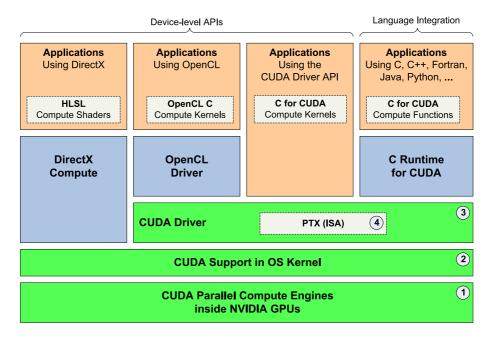

An overview of CUDA, which gives a introduction to how CUDA is structured is shown in figure 4.1. The CUDA architecture consists of several components, one through four, which we will discuss in this chapter.

- 1. Parallel Compute engines in the GPU

- 2. Kernel level support

- 3. User mode driver

- 4. PTX instruction set architecture

Figure 4.1: CUDA architecture overview (From NVIDIA [5])

### 4.2 Programming CUDA

The NVIDIA CUDA technology consists of an extension to the C programming language, and a compiler that understands the extended programming language. The language C is extended in such a way as to enable programming on GPUs without changing the way of writing computer programs. It also contains libraries for Fast Fourier Transform and Basic Linear Algebra Subroutines. A key part of CUDA is the driver, which enables computing on the GPU.

CUDA gives a number of advantages by allowing to program the GPU with the C programming language directly, instead of using a Graphics API. CUDA also supports scattered writes are supported, meaning you can write to arbitrary GPU memory addresses. The framework also gives full integer support.

The CUDA solution is proprietary, and runs on Windows (32/64bit) and Linux (32/64bit) as well as Mac OS X. The CUDA SDK was initially released to the public in February 2007. CUDA requires a modern NVIDIA graphics card with a unified shader architecture. The first card who had this capability was the GeForce 8.

CUDA enables the programmer to write programs almost as standard programs, except that some syntax is different, and that you program a lot more threads have to be considered, for optimal performance.

Which parts of the CUDA library are supported on a GPU is determined from what

Compute capability the GPU has. For example, a G80-based GeForce 8800 GTX has Compute capability 1.0, while a G92-based GeForce 8800 GT has Compute capability 1.1, meaning that more of the CUDA library is supported. Even though the 8800GTX card is better in some ways, by having more stream processors, it lacks some of the features that the CUDA API offers, like for instance atomic memory operations. The latest version as of now is CUDA version 2.0, where some of the newest features requires Compute capability 1.2.

CUDA abstracts away some of the low level programming, where programmers need to use a assembly language for programming. This means that NVIDIA can make changes to the architecture and instruction set without having to rewrite applications. This is different to how the Intel instruction set is carved in stone. It cannot be changed because of the many applications that are written partially in Intel assembly code, meaning they could potentially stop working. It can, however, be extended with new features (like MMX [34] and SSE [35]).

The program that executes on the GPU is called a *kernel*. This kernel is invoked from CPU code. The kernel can call other functions that are declared as \_\_device\_\_ functions, but not functions running on the CPU. The kernel does not return any value. When invoking the kernel, the number of *blocks*, and threads in each block must be declared. A block is a group of threads that are executed together, and have synchronization possibilities. A *grid* is a number of thread blocks which must be completed before the next grid can start.

Only limited synchronization is available, which can be a problem when writing applications. Threads can synchronize internally in a block, between blocks however, no synchronization is available. The CPU code can wait until all threads are synchronized, so in a way it is possible to synchronize between the blocks, but only with help from CPU code. The synchronization is done with the \_\_syncthreads() function. This is a barrier function, meaning that all threads in a block must reach this point, before they can continue.

The main system memory is not available from the GPU threads. Therefore, data must be copied to the GPU for processing, and back again when the data is processed. This is one of the challenges for GPU programming. Even though the memory bandwidth and speed of the GPU is high, transferring enough data over the bus can be a challenge. The bus between the GPU and CPU is PCI Express. For example, the PCI Express version 1.1 has a capacity of 250MB/s in each lane. A graphics card normally has 16 lanes (called PCI Express 16x), which gives a data rate of 4GB/s. The latest version of the PCI Express standard, version 2.0 doubles this data rate.

| .cu             | CUDA source file               |

|-----------------|--------------------------------|

| .cup            | Preprocessed CUDA source file  |

| .c              | C source file                  |

| .cc, .cxx, .cpp | C++ source file                |

| .gpu            | Gpu intermediate file          |

| .ptx            | Ptx intermediate assembly file |

| .o, .obj        | Object file                    |

| .a, .lib        | Library file                   |

| .res            | Resource file                  |

| .so             | Shared object file             |

Table 4.1: nvcc supported files (From NVIDIA [12])

## 4.3 The compiler

The CUDA compiler is called *nvcc*, and is based on Open64, which is an open source compiler originally designed for the IA-64 Intel architecture. NVIDIA chose Open64 because of the strength of its optimizations [36], although customizing the gnu compiler collection (gcc) was also an option. It uses gcc for compiling the programs. The nvcc compiler hides some of the details of compilation. We will, however, discuss some of the details here.

The *nvcc* compiler can compile regular .c files, which it just passes directly to gcc for compilation, as these files contain only standard C. nvcc also deals with .cu files, that are made in the extended C language which is used in CUDA. .cu and .cup files, that include both host code and device functions. It is therefore possible to use pure C code directly in CUDA, without having to change anything. This code will then run as normal on the CPU and not on the GPU. In case of running nvcc on a Windows platform, code compilation is not always forwarded to gcc, but for example to the Microsoft Visual Studio C compiler.

The nvcc compiler also supports generating an emulation version of the code. This means that the code will not actually run on the GPU. This emulation code can be useful for testing, as it is easier to debug, for example with a debugger like gdb [37] or with printing data to the screen, neither is possible when running on the GPU. The emulation mode is, however, limited because it does not run the threads in parallel, but in sequence. This implies that a lot of errors can go past without being noticed in emulation mode. It also means that if one thread depends on the outcome of another, it might stall, because the other thread will not run until the first has completed its execution. Emulation mode is often slower, so testing code in emulation mode might take more time.

Cubin are a file format the compiler generates as intermediate files, and it can be instructed to keep these files for inspection. In these files we are able to see some information about the code. Especially interesting are the shared resources required by each thread, like shared memory used for the parameters, and the number of registers needed per thread. These numbers can be interesting in explaining performance figures.

## 4.3.1 Compilation stages

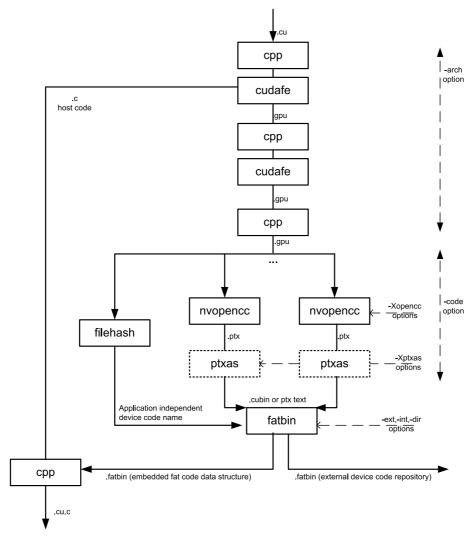

Figure 4.2: nvcc compilation flow (From NVIDIA [3])

The stages of the nvcc compilation is shown in figure 4.2. The input program is separated by nvcc into a gpu part, and the part that is running on the host code. The part of nvcc responsible for this is called *cudafe*. This code is then processed further and

generates cubin and ptx (device only) code files, while the host-only code is forwarded directly to gcc. Cubin are CUDA binary files, while ptx are intermediate files, seen from table 4.1. The code is assembled and a *fatbin* is generated which is merged with the previously separated host code. A fatbin is a binary with all code that needs to be run on the GPU embedded.

Preprocessing is done multiple times, first the .cu files, then later for expanding CUDA macros. The last preprocessing step merges the files back together. Cudafe can be used for preprocessing, which hides some output.

#### 4.3.2 Runtime

The runtime is the part of CUDA that executes programs on the GPU. This has support in the driver, which is mandatory for CUDA. The runtime does memory management, and shuffles data between the main and GPU memory in the system.

#### 4.4 Performance

CUDA performance is often measured in how well the GPU is utilized. NVIDIA offers a spreadsheet for calculating how well the GPU is utilized, giving the developer a metric for calculating efficiency. NVIDIA has also provided a profiler, which gives the developers a possibility to optimize their applications.

When optimizing CUDA applications, there are certain things one should consider. A parallelizable algorithm is beneficial where many threads have to be able to work on the program without exchanging data with each other (thus avoiding too much waiting). One also has to think about memory accesses. When many threads try to access the same memory the memory can be locked, and the threads forced to wait, thus degrading the performance. To get high utilization on the GPU, many threads should be used. Instead of having few threads doing a lot of work, one should have many threads doing less work. Loops should be unrolled if they do not have too many iterations. This can be done either manually, or with the pragma statement for the CUDA preprocessor, which can unroll loops for you. The programmer can write #pragma unroll 5, will unroll the loop to five iterations. This means the loop must be done in a multiple of 5 times, to yield correct results. Divergence in a single warp should be avoided, branching should preferably be done for the whole warp.

One of the most important places where we can optimize is how we use the memory available on the GPU. We have seen in chapter 3 that we have several types of memory available: shared, registers, constant, texture and uncached local and global memory. The shared memory can be viewed as a sort of used managed cache, and Selberstein et al. have investigated this idea [38]. This memory is shared between all threads in a block, and is as fast as the registers when the access pattern is correct. The access pattern should avoid multiple threads trying to access the same *bank*. A bank is a 32-bit part of the memory. Shared memory should be preferred, because using to many local variables in the code means that some of these variables can be placed in the uncached global memory, and this can severely impair the efficiency of the program. To see if variables are placed in global memory one can inspect the assembly code from the compiled. Texture and constant memory are read-only, but can be very efficient for lookup tables and other memory that should not be edited.

The NVIDIA CUDA Visual Profiler, is a tool from NVIDIA which can profile applications executing on the GPU. It can plot and write out tables on the performance of the applications running, listing number of calls, GPU time, CPU time, and other information. It can also show the occupancy of a program running on the GPU, meaning how much of the time the multiprocessors are executing code, and not waiting for memory accesses.

Ryoo et al. have investigated optimization principles for CUDA programming [39]. They found that optimizing various applications gave between a 1.16X and 431X total application speedup, showing some of the potential of optimizing programs running on the GPU.

## 4.5 Debugging

NVIDIA has released a debugger called CUDA-GDB [40]. It is based on GNU GDB [37]. This debugger as of writing only supports Linux, and is therefore has a more limited user base. It's goals are to make debugging CUDA applications easier than it was earlier, and to present developers with a well known debugger. It requires a compiler flag for compiling and will only work when code is compiled without optimization. It gives the possibility to pause CUDA execution at any function symbol or line of code, like normal GDB. Because all device functions are inlined, it is not possible to step over a function.

## 4.6 Other technologies

There are several other technologies for programming GPUs. We look into Shading languages, Stream SDK, BrookGPU and OpenCL.

### 4.6.1 Shading language

The first method of programming GPUs was basically just to use the shading language available in OpenGL [41] and DirectX [42]. This requires knowledge of OpenGL/DirectX and meant you had to use a lot of time implementing, not being able to focus on the algorithms [43]. Available shading languages include Cg, HLSL and the OpenGL shading language.

#### 4.6.2 Stream SDK

Close to Metal (CTM) was ATI's (and now AMDs) alternative to CUDA [44]. It is now called Stream SDK [45]. Stream SDK is available for Windows XP (32/64bit) and Linux(32/64bit).

CTM was originally intended to be more low level than CUDA, but was changed when the name changed to a more high level platform. Stream SDK still gives access to a low level programming model, through the Compute Abstraction Layer (CAL). Libraries included in Stream SDK are the AMD Core Math library (ACML), which provides access to mathematical functions. The AMD Performance Library (APL) is also included and a video transcoding library called COBRA. The latter assists in video transcoding, which is a computationally intensive task, and has been successfully offloaded to the GPU.

#### 4.6.3 BrookGPU

BrookGPU [46] is developed at Stanford University. It is a variation of the Brook programming language, which is an extension to the C programming language. Brook is one of few GPGPU libraries that is licensed under a free license, namely the BSD license. BrookGPU works on Intel, NVIDIA and ATI GPUs. Brook is currently in version 0.5 beta.

## 4.6.4 OpenCL

Open Computing Language (OpenCL) is Apple's alternative for programming GPUs [47]. This is based on the C standard C99. OpenCL is an attempt to create an industry standard for programming GPUs, and is therefore named in the same way as OpenGL and OpenAL, and also submitted to Khronos Group, which has standardized OpenGL. OpenCL is set to be included in Mac OS X version 10.6 (Snow Leopard). OpenCL is now standardized by the Khronos Group, and has a syntax similar to CUDA.

## 4.7 GPU multitasking

Using the CUDA framework there are some challenges with running multiple applications at once. They share the GPU, but there is currently no trivial way to instruct the GPU on what tasks to run when, and GPU memory is not pageable, so the GPU can easily run out of memory running many applications.

## 4.8 Summary

We have in this chapter discussed how the CUDA framework works, and briefly discussed other alternatives to the CUDA framework. We discussed NVIDIAs CUDA, which we believe is one of the most mature frameworks for GPU programming, and we therefore wish to further use this framework, when we in our next chapter investigate programming an actual application, to investigate various parts of optimization.

## **Chapter 5**

# **AES Encryption on CUDA-enabled GPUs**

#### 5.1 Introduction

In this chapter, we will investigate the Advanced Encryption Standard (AES) encryption, how it works, and how an ordinary CPU implementation of a AES encryption program can be converted to run on the GPU.

AES is an important part of the encrypted file system we will investigate in chapter 6. Before we can investigate offloading the CPU intensive encryption in this file system, we first look into some different implementations for encryption on the GPU, to see what kind of performance we get from a GPU implementation, compared to a CPU implementation.

AES is also an algorithm which is massively parallelizable, which we will see in this chapter. In will addition to be an important part of the file system we will investigate, serve as an example of an application that is ported from running on the CPU to GPU, using the CUDA framework. We will also look into a variety of optimization techniques, where AES also is a good example, but these techniques can be applied in a variety of applications.

## 5.2 Advanced Encryption Standard

AES [48] is a block cipher encryption standard, designed as a successor to the Data Encryption Standard (DES). It was designed to be easy to implement in hardware and software, and requires little memory. The AES algorithm was designed by two Belgian cryptographers, Joan Daemen and Vincent Rijmen, and submitted to the AES selection process under the name of Rijndael.

AES encryption consists of several steps, mentioned here, with the individual sub steps described later. Decryption of data is achieved by doing all the stages in reverse order. Some of the items in the list are repeated several times, in what is called rounds. Note that there is no MixColumns in the last round. The number of rounds in the encryption process is based on the key size seen from table 5.1.

- KeyExpansion

- AddRoundKey (Initial round)

- SubBytes (Rounds 1 to N-1)

- ShiftRows (Rounds 1 to N-1)

- MixColumns (Rounds 1 to N-1)

- AddRoundKey (Rounds 1 to N-1)

- SubBytes (Last round)

- ShiftRows (Last round)

- AddRoundKey (Last round)

The definition of a block cipher is that it operates on blocks of data, which in this case are 16 bytes large. The block is called a state during the encryption phase, and can be viewed as a 4x4 matrix. The block cipher takes either a plain text input that yields a encrypted output called a cipher text, which is the same size as the plain text, or a cipher text input that yields a plain text. Without knowing the key the cipher text should be impossible to decode correctly. It can be required to know a initialization vector, as we see in paragraph 5.2.5.

One important thing to be aware is that the AES algorithm is big-endian, so in case we are on a little-endian architecture (like normal Intel-compatible architectures used in desktop-computers and many servers) data must be converted to big-endian before

| Key size | Number of Rounds |  |  |  |

|----------|------------------|--|--|--|

| 128      | 10               |  |  |  |

| 192      | 12               |  |  |  |

| 256      | 14               |  |  |  |

Table 5.1: Number of rounds given key size

the algorithm is run, and must be converted back to little-endian after the algorithm has been run.

## 5.2.1 KeyExpansion

This stage converts the encryption key into a set of round keys. This operation is known as the Rijndael Key Schedule. The round keys are used in the later stages to encrypt the data.

## 5.2.2 SubBytes

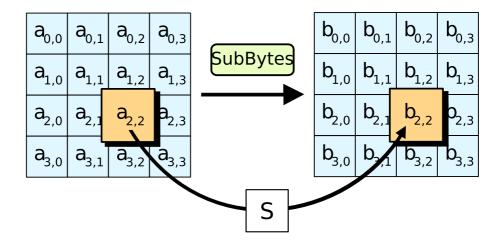

In the SubBytes stage all the bytes in the cipher block are substituted with a byte from a substitution box table (sbox). The original value is used as an index in the sbox. The purpose of this is to avoid linearity in the cipher block. The SubBytes stage is seen in figure 5.1.

Figure 5.1: The SubBytes step (From Wikipedia [6])

#### 5.2.3 ShiftRows

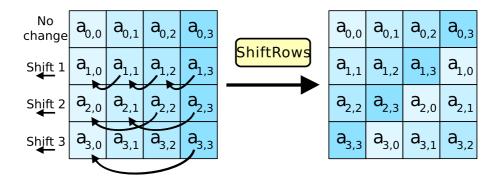

The ShiftRows stage operates on rows in the cipher block. For 128 and 192 bits keys, it leaves the first row intact, rotates the second row one position to the left, and the third and fourth row two and three positions respectively. For 256 bits keys the first row is left intact, while the second third and fourth are shifted one three and four bytes respectively. The ShiftRows stage is shown in figure 5.2.

Figure 5.2: The ShiftRows step (From Wikipedia [6])

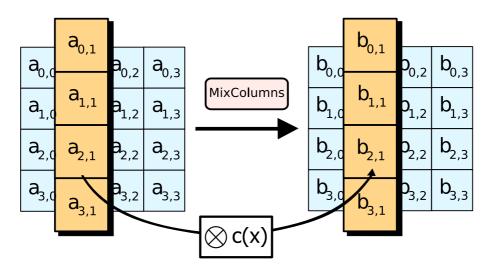

#### 5.2.4 MixColumns

The MixColumns stage operates on columns in the state. It multiplies each column of the cipher block with a fixed polynomial c(x) as seen in figure 5.3. The purpose of this stage is to provide diffusion in the cipher block, which means that redundancy in the plain text is dissipated in the statistics of the cipher text.

Figure 5.3: The MixColumns step (From Wikipedia [6])

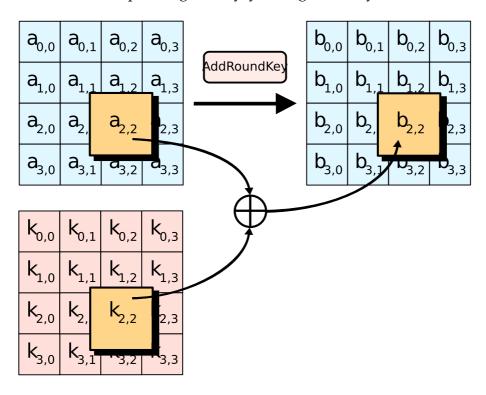

## 5.2.5 AddRoundKey

The AddRoundKey stage is where the state is combined with a subkey of the round key, to introduce the key in the encryption. The subkey is added by XORing each byte of the state with the corresponding subkey, yielding a new byte for the state.

Figure 5.4: The AddRoundKey step (From Wikipedia [6])

## 5.2.6 Lookup table

It is possible to speed up the execution of AES on systems with 32 bits or wider data types, by combining the SubBytes, ShiftRows and MixColumns into lookup tables. These tables require four 256-entry 32-bit tables, needing a total of four kilobytes. Each round now needs 16 table lookups and 12 XOR operations. It is also possible to use just one single 256-entry 32-bit table by using circular rotates.

## 5.2.7 Modes of operation

A *Mode of operation* describes how a stream of data is encrypted using block ciphers, because block cipher algorithms themselves only describe what is done with a block of a fixed length. Data lengths are arbitrary, and to have secure encryption one has encrypt

blocks differently, even though they have the same plain text input, thus avoiding dictionary and replay attacks. The simplest mode of encryption does not protect against these threats. This mode is called Electronic Cookbook (ECB) and is regarded as insecure. This is the only mode of operation which does not require an initialization vector. None of the modes of operation described in this section provides integrity protection, when they are used for encryption, meaning a change in the encrypted data either by error or an attack can go undetected. They can, however, provide integrity protection instead of encryption.

#### **Initialization vector**

A initialization vector (IV) is used to start the encryption process for the first block. The IV must be known for decryption, but does not have to be kept secret like the key. However, for encryption, the same IV should not be reused for encrypting different data, as it can be possible to detect patterns in the cipher text. The length of the IV must also be large enough, to avoid IV collisions, which was a problem for security the Wired Equivalent Privacy 802.11 standard [49]. This made it possible to brute force attack the encryption of Wireless LANs using this form for encryption.

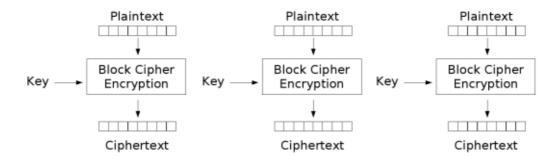

#### **Electronic Cookbook (ECB)**

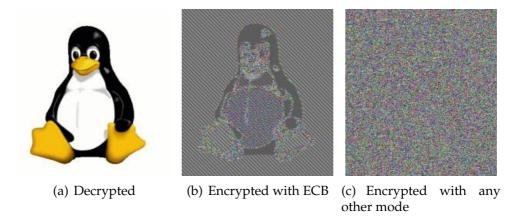

In this mode of operation, each block is encrypted in the same way. This is the simplest mode of operation to implement, and is easy to do in parallel because there are no inter-block dependencies. The encryption simply runs the cipher block algorithm on each block in the data, see figure 5.2.7 for the encryption process, and figure 5.2.7 for the decryption process. This means that two identical plain texts will be encrypted to identical cipher texts. As mentioned it has a severe problem with security. In figure 5.7 we see a picture of the Linux mascot Tux decrypted, encrypted with ECB (in the middle) and how it would look encrypted with any other mode of operation. We see in figure 5.7(b) that it is possible to distinguish the original picture, and this shows that the encryption with ECB in some cases is not sufficient. One should however, note that even though figure 5.7(c) looks random, it is not a guarantee that the encryption is secure.

Electronic Codebook (ECB) mode encryption

Figure 5.5: ECB Encryption (From Wikipedia [7])

Electronic Codebook (ECB) mode decryption

Figure 5.6: ECB Decryption (From Wikipedia [7])

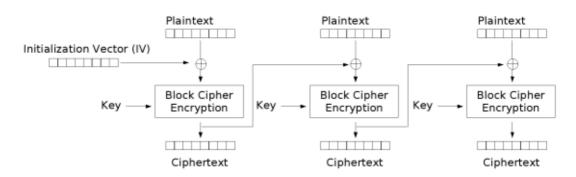

#### Cipher Block Chaining (CBC)

Cipher Block Chaining (CBC) is a mode of operation developed by IBM in 1976. It is based on XORing each plain text with the previous cipher key before being encrypted. The first plain text is XORed with the IV as seen in figure 5.2.7. This mode of operation is common, but has the disadvantage that its encryption stage cannot be parallelized as efficiently as ECB, because of the inter-block dependencies of the mode of operation. To decrypt the data, each decrypted block must be XORed with the previous cipher key, or the IV for the first block as seen in figure 5.2.7.

Figure 5.7: Encrypted and decrypted image of Linux mascot Tux (From Wikipedia [7])

Cipher Block Chaining (CBC) mode encryption

Figure 5.8: CBC Encryption (From Wikipedia [7])

#### **Cipher Feedback**

Cipher Feedback (CFB) is somewhat similar to CBC. It first encrypts the IV, and XORs this encrypted data with the plain text to yield the cipher text. It then takes this cipher text, encrypts it and XORs it with the following plain text. CFB have the advantages over CBC that the block cipher is only used in the encryption stage, and that the message does not need to be padded to a multiple of the cipher block size.

#### **Output Feedback**

Output Feedback (OFB) is a mode of operation, where the IV is encrypted, and this is XORed with the plain text to yield the cipher text. The encrypted IV is then encrypted, and is XORed with the next plain text, to yield the next cipher text. This is called a synchronous stream cipher. It has the advantages that it allows many error correcting

Cipher Block Chaining (CBC) mode decryption

Figure 5.9: CBC Decryption (From Wikipedia [7])

codes to work, because it does not use the cipher text as input for the next encryption.

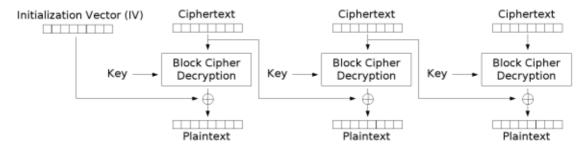

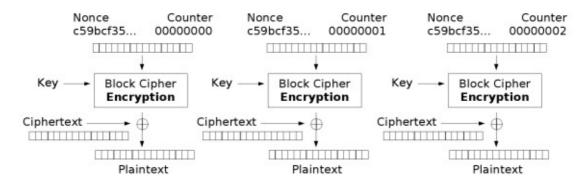

#### Counter

Counter (CTR) is another mode of operation, but works different from the other modes of operation. It introduces a new term called *nonce*, that is similar to the IV, but has a changing element called a *counter*, in addition to a static element that remains the same throughout the encryption. CTR encrypts this nonce for every stage, with the counter element increased with one for each cipher block. The encrypted nonce is then XORed with the plain text for each cipher block, and this yields the cipher text as seen in figure 5.2.7. Because of there are no inter-block dependencies, as seen in the figure CTR is fully parallelizable. In figure 5.2.7 we see how a block is decrypted, by decrypting the nonce and XORing it with the cipher text.

Counter (CTR) mode encryption

Figure 5.10: CTR Encryption (From Wikipedia [7])

Counter (CTR) mode decryption

Figure 5.11: CTR Decryption (From Wikipedia [7])

#### **Error propagation**

Error propagation is something that happens with the sequential modes of operation, where a bit error in one cipher text will follow into the next cipher text decryption.

## 5.3 Implementation

We have investigated two different approaches to the AES algorithm on a GPU using the CUDA framework. Both are based on the CTR mode of operation, because of both is security and its possibility to be parallelized. Both implementations are based on an implementation written for a conventional CPU. We also want to show that it is possible to get higher efficiency porting these applications to a GPU.

We also give a background on programming CUDA, and will look into some examples of code to see how it differs from traditional programming.

## 5.3.1 Standard Implementation

Our standard implementation is a implementation, written by directly following the AES encryption standard [50], without focus on optimization. It is based on a implementation aimed for beginners wanting to understand how the AES algorithm works [51]. This implementation is well documented, and does not focus on speed. We decided to use this implementation to give an introduction to CUDA programming, and also show how we can get performance benefits from porting this application

written for a traditional CPU to a GPU-assisted program for encryption/decryption of data.

We first re-wrote the application to use a CTR mode of operation, for high security combined with the possibility of parallel execution of cipher block encryption. We also wrote a simple threaded implementation of this code for use on CPU, so we could compare the GPUs with traditional multi-core CPU architectures. The multithreading for CPU was implemented with the POSIX threads (pthreads) library. It ran one thread per core, and divided the encryption job into equally sized parts, after reading the data for encryption into memory, it then wrote the result back to file. This is not an optimal way of multithreading of this application, because it performs both reads and writes to/from the file single threaded, but we wanted to make it more similar to how the GPU implementation was done.

A lot of the work with this implementation was making it thread safe, because it used several global variables, which is not well suited for parallel execution. When this work was completed, it needed only minor adjustments to run on the GPU. By itself, this did not give the speedup we wanted, so we did further work to increase the efficiency. We stored the round key and nonce in texture memory, which is cached. We reasoned that this would be beneficial because of frequent accesses to the round key. The nonce, however, is only accessed once, so it might not be as important to the performance. We also used constant tables for the sbox, which are not changed, but accessed frequently. This memory is also cached. Last we used shared memory for the state matrix. Because the state matrix is not shared between threads, we allocated shared memory for one state per thread, and accessed the shared memory based on the thread index.

## 5.3.2 Lookup Table Implementation

We also had an AES implementation which uses lookup tables, this implementation reduces the calculations needed to perform AES encryption, because it uses lookup tables with precalculated values for the calculations as described in section 5.2.6. For use on a CPU, this is much faster than the standard implementation, as we will see in the results section. We wanted to see how much of a speedup we could get on a already optimized program, compared to the standard implementation which was initially not optimized at all. This code was originally based on an implementation made by Philip J. Erdelsky [52], modified to support counter mode of operation.

| GPU                       | 8800 GTX | 8800GT  | 8800GT-OC | 8800GT  | GTX 280 |

|---------------------------|----------|---------|-----------|---------|---------|

| Architecture              | G80      | G84     | G92       | G92     | GT200   |

| Stream processors         | 128      | 32      | 112       | 112     | 240     |

| Core Clock (MHz)          | 575      | 540     | 600       | 660     | 602     |

| Shader Clock (MHz)        | 1350     | 1180    | 1500      | 1674    | 1296    |

| Memory Clock (MHz)        | 900      | 700     | 900       | 950     | 1107    |

| Memory Amount             | 768MB    | 256MB   | 256MB     | 512MB   | 1024MB  |

| Memory Type               | GDDR3    | GDDR3   | GDDR3     | GDDR3   | GDDR3   |

| Memory Interface          | 384-bit  | 128-bit | 256-bit   | 256-bit | 512-bit |

| Memory Bandwidth (GB/sec) | 86.4     | 22.4    | 57.6      | 60.8    | 141.7   |

| Compute Capability        | 1.0      | 1.1     | 1.1       | 1.1     | 1.3     |

Table 5.2: Hardware specifications for the GPUs we have tested on [13] [1] [14] [15]

We modified this implementation to use different types of memory for better performance. Texture memory was used for the nonce and texture, and shared memory for the cipher block internal state. The lookup tables were stored in constant memory, and because the cache is 8kB per multiprocessor we reasoned that the whole lookup table could be stored in the cache.

For both the standard and the lookup table implementation we implemented support for a arbitrary number of threads. This was done in order to be able to test which effect the amount of threads had to the performance. We read the entire job into memory and divide it into chunks based on the amount of threads we were testing with. The chunks were sized in such a way as to have sufficient blocks for encryption. Because it was hard to calculate the number of blocks and threads correctly to be able to encrypt the data, we had to pad data so that all launches were the same size. We modified the benchmarks in such a way that it accounted for this padding.

### 5.4 Results

For testing we tested the execution time of the GPU kernel, and compared different GPUs, the two implementations and also compared this to the original CPU implementations run on a few different computers. We also tested how many threads we could run on each implementation and what kind of differences in performance this yielded. We tested the code on two different machines, one with a E6750 2.66 GHz Intel Core 2 Duo processor (2 cores in total), the other with 4 AMD Opteron 8218 2.6 GHz processors (8 cores in total). We also tested the code on the GPUs listed in table 5.4.

#### 5.4.1 Overview

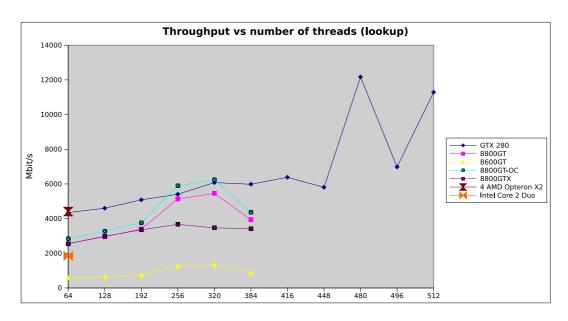

Figure 5.12 show an overview of the different architectures performance, running the lookup table implementation. The X-axis show the number of threads per block, and the Y-axis shows the encryption performance in Mbit/s. Note that the X-axis is not linear, the increments are not always equal. This is partly because we see an interesting dip in the performance when running with 496 threads, which will be discussed later in this section. We see that all but one of the graphic cards are faster then the Intel Core 2 Duo processor, while only three of the cards outperform the 8-core AMD Opteron machine. We can also observe that the overclocked 8800GT card outperforms the highend GTX 280 card running with 320 GPU threads per block. We believe this is because the lookup table implementation is memory bound, and therefore the higher core clock on the overclocked 8800GT card allows the lookups in the tables to go faster, with this amount of threads per block.

We can also see that for all implementations the performance increases until a peak. We believe this is because this is due to the shared resources available for each multiprocessor, and how it is used optimally. Increasing the thread count means that it is easier for the scheduler to hide away memory latency, because it can easier find a new warp which is ready for execution. However, when increasing the thread count beyond this peek, it seems that there are too few shared resources available for each thread, and some local variables need to be placed in global memory, impeding performance. The sudden peak for the 280GTX card is also interesting, which might be because this new card hits a point in the scheduling where latency for memory accesses to a large degree hidden, because there are always available new threads for execution when a warp has to wait for memory accesses. The later dip in performance might be related to the fact that threads are scheduled in warps of 32 threads, and running with 496, the last warp will only have 16 threads. We see the increased performance later for the 280GTX, because it has more shared resources available on each multiprocessor, than the other cards. The other cards are not able to run more than 384 threads per block, at that point there is not available resources in the multiprocessors to give each thread gets what it needs. It is also interesting to note that the three cards with compute capability 1.1 (8600GT, 8800GT and 8800GT-OC) all have a similar curves, even though the performance is different. This is probably because their architectures are similar, but the number of multiprocessors are different.

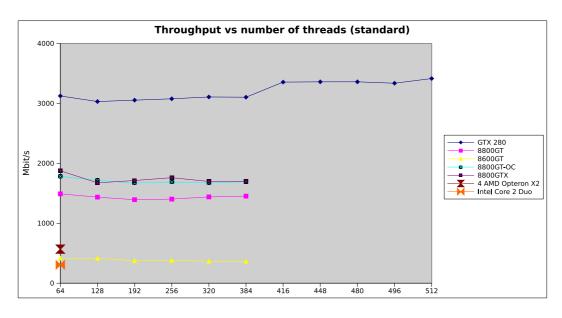

In figure 5.13, we see the same measurements done with the standard implementation. These numbers are different, which is due to the fact that this implementation is computationally bound. We see that the line for all GPUs are flat, and that we do

Figure 5.12: Throughput vs number of threads (Lookup implementation)

not get an increase in the performance increasing the number of threads. Because the implementation is computationally, there are always threads available for execution, since we test with minimum 64 threads, and each warp are 32 threads. There should be no memory accesses that needs to be hidden away with increasing the number of threads like in the memory bound lookup table access, because all operations in this kernel works on on chip shared memory.

Figure 5.13: Throughput vs number of threads (Standard implementation)

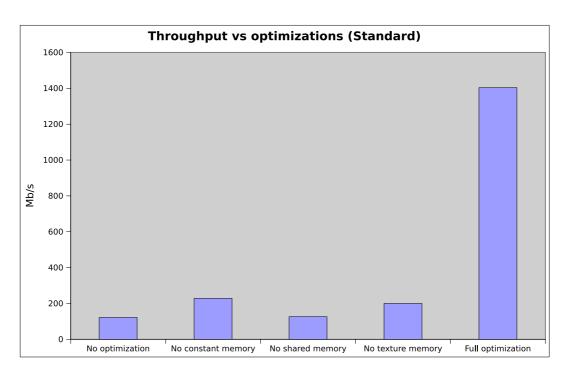

## 5.4.2 Optimization